百万门系统级芯片的时钟树设计

2014-12-05张玲,王澧

张 玲,王 澧

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着集成电路的快速发展,人们对数字系统的要求越来越高,集成电路正朝着大规模、小体积的方向飞速发展,片上集成系统(SoC)也应运而生。这些高速度、低功耗、高性能的大规模集成电路对于时钟树的实现提出了更高的要求。时钟树综合的主要目标就是使时钟偏差、相位延迟最小化,以最大限度地为时序收敛服务,并尽可能减小时钟网络的功耗、噪声和连线间耦合。一个好的时钟树设计可以对整个设计的时序、功耗、面积以及布线拥塞度和串扰影响起到至关重要的作用。

在现有基于标准单元设计的ASIC流程中,通常将扇出较大的时钟网络在综合阶段设置为理想时钟,在物理设计阶段进行时钟树综合,因此,时钟树综合是后端物理设计的关键步骤之一。

本文介绍采用Synopsys公司Astro后端工具对一款百万门级、基于0.18 μm工艺的SoC芯片时钟树综合过程中遇到的问题以及解决方法,详细说明时钟树综合的基本过程,特别是在多种工作模式下时钟树综合遇到的问题及解决方案,介绍时钟树综合的功耗优化、复位信号的平衡和时序优化。芯片是基于0.18 μm Salicide 1P6M CMOS工艺制造的SoC芯片,规模约为200万门,工作频率100 MHz,封装引脚391个。

2 芯片介绍

该芯片是一款为用户定制的专用SoC芯片,采用0.18 μm 1P6M Salicide CMOS常规工艺。芯片内部集成有ARM核、全定制设计的IP、多个SRAM等宏单元,是一颗典型的全数字SoC芯片。芯片采用双电源供电方式工作,分别为3.3 V与1.8 V供电。电源、地引脚分为3组,其中2组为1.8 V供电,1组为芯片内核及端口前级驱动供电,1组为芯片DPLL供电;另1组为3.3 V供电,为芯片上所有端口后级驱动供电。

3 时钟简介

在大规模电路中,每个寄存器之间的数据传输是通过时钟信号的稳定脉冲来进行同步控制的,而数据传输和数据接收的速度则是由时钟频率所决定的。时钟树设计的两个最重要的目标就是时钟偏差和相位延时的最小化,并且使时钟网络的功耗最优化。

3.1 时钟定义

时钟树规划第一步是查看逻辑综合时对时钟的定义。时钟信号的特征参数很多,时钟周期(频率)、时钟延迟以及时钟信号的不确定性是时钟定义三要素。该信息一般存于.sdc文件中。逻辑综合时对时钟的定义主要使用create_generated_clock和create_clock来完成。它们基本相同,不同的是create_generated_clock定义的是产生内部的一个时钟,时钟属性无法自由定义,只能继承它的时钟源的时钟属性;而create_clock则可以自由定义时钟属性。通过时钟的定义可以了解芯片所采用的时钟系统。

描述时钟的几个要素是[1]:(1)时钟源(source):时钟起点,一般为锁相环或专门的时钟处理模块的输出端;(2)时钟周期(period):时钟从低电平到高电平再回到低电平直至下一个高电平上升前的时间,即时钟波形重复的最小时间间隔;(3)波形(waveform):简单的波形有上升沿和下降沿,描述两个边沿就可以说明波形,即上升沿位置和下降沿位置。

3.2 时钟偏差

时钟偏差是指从时钟源点(Source)到各时钟汇点(Sink)的最大延时时间的差值。在芯片电路设计中,要保证系统功能正确,必须满足式(1)所示的关系。

在式(1)中,dL是组合逻辑电路的最长路径延时,tskew是时钟偏差,tsu是沿触发同步器件的建立(Setup)时间(时序元件正常工作时一般数据信号先于时钟信号到达的时间),tcq是沿触发器件的时钟端到Q输出端的延时。随着集成技术的发展和器件尺寸的缩小,dL、tsu、tcq都明显减少,因此,对于深亚微米工艺,时钟偏差skew对电路速度的影响更为突出。Bakoglu指出skew对高性能系统的时钟周期的贡献超过了10%[2]。较大的时钟偏差也可能会引起电路同步失效。所以,时钟树综合成为后端设计中一个重要的步骤。关于时钟偏差的示意图见图1。

图1 时钟偏差Skew的示意图

3.3 时钟种类

(1)自定义时钟:用create_clock可以自定义一个时钟,在逻辑综合工具进行门级网表综合时,时钟源点可以设定在层次化模块的端口处或具体的标准单元的引脚上。

(2)衍生时钟:create_generated_clock可以创建生成的时钟,该芯片中不仅仅只有外部的晶振时钟,还有内部生成的分频时钟。新的时钟频率可以直接在原时钟的频率上进行一个整数倍的分频。用create_generated_clock生成的时钟称为衍生时钟,它在时钟树综合时可以看作一个新的独立的时钟源来对它控制的模块进行时钟树综合,但是本质上它依然是原始时钟源的一个分支。平衡这个分支和原始时钟源点间的时钟偏差或时钟延时可以通过调整衍生时钟源点的位置或插入时钟缓冲器来完成。

4 百万门级系统芯片的时钟树综合实现

4.1 芯片内部时钟结构

该芯片内部时钟由独立的4个模块和选择器产生,4个独立模块分别是PLL模块、DPLL模块、CLK_SEL模块和CLK_RAD模块。芯片内部的时钟结构如图2所示。

4.2 时钟树综合参数设置

时钟树综合的约束文件通常包括3类:工艺库定义的约束DRC(design rule constraints),约束文件(SDC)定义的约束,时钟树综合设置中自定义的约束。工艺库定义的约束在技术文件中规定,是芯片制造厂制定的[3]。约束文件定义的约束是逻辑综合或静态时序分析根据时序给出的参考约束。规范说明书的约束是自定义约束的一种,一般最为严格。3类文件的约束中最严格的约束会被施加在时钟树上。此芯片的时钟树综合中,需要确定做时钟树综合的时钟名、时钟偏差skew的约束设置以及需用到的缓冲器类型。该芯片用到的缓冲器类型有CLKBUFX1、 CLKBUFX2、CLKBUFX3、CLKINVX1、CLKINVX2、CLKINVX3等。该芯片使用tcl脚本语言设置时钟树参数。创建时钟树的脚本信息如图3所示,如需对时钟树的设置做一些改动,可以在该脚本上进行。

图2 芯片内部时钟结构示意图

图3 脚本形式设置时钟树参数图

4.3 时钟树综合策略

时钟树综合是时序优化处理中最重要的一步,时钟树综合的目的是减小时钟偏斜和插入延时。在本芯片的时钟树综合中主要考虑了以下几点:第一,要评价芯片时钟树综合的先后顺序,结合本芯片存在8路不同频率时钟的特点,评价了各路时钟进行时钟树综合的优先顺序,最终选择了把最重要的时钟放在最后综合的方案;第二,在Astro中要明确时序参数及模型的设置;第三,为时钟网络设置专门的布线规则。在此采用了2倍于正常设计规则的线宽规则作为时钟线的间距规则,以减小时钟减少毗邻连线的耦合电容及由此带来的信号间串扰;第四,选择具有相同上升及下降时间的Buffer/Inverter作为时钟树的驱动单元,便于更好地控制ClockTree上的偏斜及插入延迟;第五,考虑RC参数的优先布线原则并进行线长优化等策略。

芯片中有多种工作模式,主要的两种工作模式是DFT模式与Function模式,DFT模式的优先级低于Function模式。时钟树综合时采用先综合低优先级时钟,再综合高优先级时钟的策略,即先综合DFT模式下的时钟树,再综合Function模式下的时钟树。前端设计人员把SDC文件分成DFT模式下的SDC文件和Function模式下的SDC文件,这两个文件分别导入两种以上工作模式。时钟树综合的流程示意图如图4所示。经过这种时钟树综合策略,综合后的时钟树便能很好地满足此SoC芯片严格的时序要求。

图4 芯片时钟树综合流程

4.4 时序优化策略

在时钟树综合阶段,Astro为达到上述时钟树综合的主要目标,一定程度上会通过移动其他单元的位置等途径来优化时钟树,从而影响了芯片的时序。事实上,通过反复的分析,我们已经发现了这个必然,在完成CTS之后,芯片的时序一定会出现一定程度的恶化现象,所以必须在CTS之后再针对芯片时序完成进一步的时序优化。在其他一些阶段也会出现同样的问题,所以在该芯片时序优化过程中拟定了以下几个关键阶段,在完成这些阶段任务后,必须进行时序的分析,如果出现不能满足要求的情况,则进行针对性的时序优化。在每一次进行和时序相关的操作步骤之前都要进行时序参数设置,时钟树插入前在时序检查时使用的是理想时钟,在时钟树插入后使用的是实际时钟,因此时钟树综合前的参数设置为选择Ignore Propagated Clock和Enable Ideal Network Delay。结合该电路的特点,拟采用以下的时序优化流程,具体流程如图5所示。

4.5 门控时钟实现策略

集成电路研究资料显示,当时钟树发生翻转时,芯片约产生30%的功耗[4]。出于低功耗设计考虑,该芯片在前端综合时加入了一千多个门控时钟单元。门控时钟单元的加入,可以控制不工作的D触发器,从而可以大幅度减少整个芯片的功耗。但是无约束的时钟门控信号将引入毛刺,导致时钟被破坏,所以在后端设计时针对门控时钟作了以下考虑。

(1)通过控制门控时钟单元与时钟树连线的连线权重,使放置门控单元时可以将与门和锁存器紧密地放在一起,在布局及时钟树综合时工具将根据连线权重来使连线尽量短,达到控制目的;(2)将门控时钟单元,即与门和锁存器设计成一个标准单元(standed cell),放入标准单元库中,在插入门控单元时整体插入;(3)设置门控时钟信号的约束;(4)完成时钟树综合后进行GATING_CLOCK_GROUP的时序检查,确认门控时钟信号已满足时序要求。

图5 时序优化流程图

4.6 复位信号的平衡

在芯片后端设计中,复位信号也是一个关键的信号。因为它和时钟信号一样,直接连到了触发器上。若复位信号的skew过大,也会造成电路不能正常工作。芯片内部复位信号工作示意图和复位信号波形图分别如图6和图7所示。图中rst1与rst2都是低电平有效,当rst1由低变高的下一个clk的上升沿时,Q1取data1的值,而这时rst2为0,Q2不能取到data2的值;当下一个clk的上升沿来时,这时rst2为1,Q2才能取到data2的值,但这时Q1的值可能已经改变,这样会使传入下一级逻辑电路的信号错误,而使芯片工作异常。

图6 复位信号示意图

为了防止芯片工作中出现以上错误,在时钟树综合之前要先解决复位信号skew过大的问题。复位信号的约束设置与时钟树约束设置类似。经过平衡复位信号这一过程,可以使芯片的时序保证一致,从而保证整个芯片正常工作。

4.7 时钟树综合结果

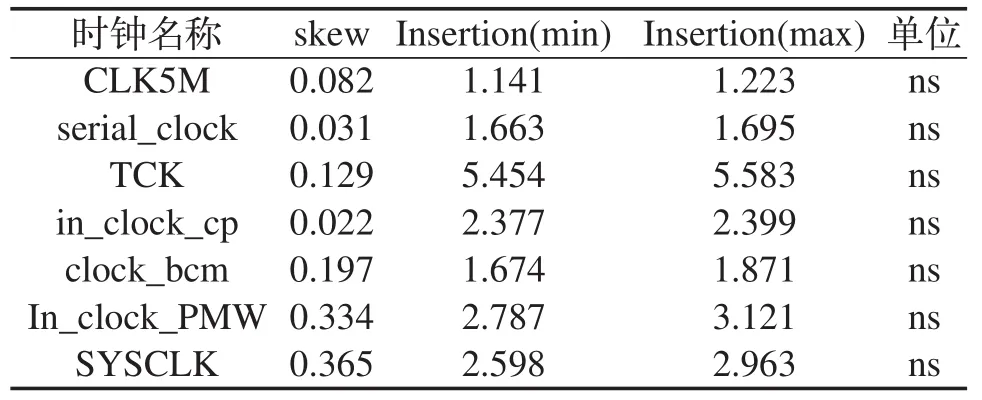

经过了时钟树综合、复位信号的平衡和时序优化等过程后,该芯片的时钟树综合工作已全部结束,时钟树的综合结果如表1所示。该芯片综合后的时钟结果能满足前端逻辑人员的设计要求。

图7 复位信号波形图

表1 时钟树综合结果表

5 结束语

本文介绍了采用Synopsys公司Astro后端工具对一款百万门级SoC芯片进行时钟树综合的过程,是笔者后端设计实践工作的一些经验总结。首先介绍了时钟树综合的设置,阐述了时钟树综合的基本策略,以及复位信号平衡和门控时钟的使用等基本实现。然后鉴于建立时间的优化考虑,引入了有效时钟偏移的时钟树综合方案,给出了有效时钟偏移的应用和实践结果分析。该芯片已成功流片,芯片的各项功能和时序都符合预期要求,证明了本文时钟树的综合方法起到了积极的作用,为以后大规模SoC电路的时钟树综合积累了经验。

[1] 陈春章,艾霞,王国雄,编著. 数字集成电路物理设计[M]. 北京:科学出版社,2005.

[2] Weste NHE, Harris D. CMOS VLSI Design:A Circuit and Systems Perspective(3rdEd. )[M]. 2005.

[3] Weste N H E, Harris D.CMOS VLSI Design:A Circuit and Systems Perspective.3rdEd[M]. Pearson, 2005.

[4] Synopsys User Manual [P]. Astro User Guide.