一种降低LTE信号高峰均比算法的FPGA实现

2014-11-22张敏娟魏亚辉

张敏娟,魏亚辉,李 晓

(1.中北大学 山西省光电信息与仪器工程技术研究中心,山西 太原 030051;2.驻马店职业技术学院 机械电子工程系,河南 驻马店 463000)

在LTE(Long Term Evolution)通信系统中,通常采用正交频分复用技术(Orthogonal Fre-quency Division Multiplexing,OFDM)作为下行传输方法,它具有抗多径效应、频带利用率高等优点[1-2],然而却引入了高峰均比(Peak to Average Power Ratio,PAPR),降低了功率放大器的效率.因此,有必要对削峰技术(Crest Factor Reduction,CFR)进行研究[3-4].CFR 是以牺牲相邻频道泄露比(Adjacent Channel Power Ratio,ACPR)和恶化误差向量幅度(Error Vector Magnitude,EVM)来降低系统峰均比,因此在削峰技术中是以三个指标来综合评价系统性能的.

目前,实现消峰的方法主要有时域限幅,噪声成型波峰因子降低(NS_CFR),峰值对削波峰因子降低(PC_CFR)三种方法[5-7].PC-CFR 算法是建立在NS-CFR 基础之上的,为了克服NSCFR 占用大量乘法器资源的缺点,PC-CFR 利用冲激响应的特性,在每一个过削峰门限的峰值区间内,仅针对该区间内的最大值进行消峰,这样仅需要很少乘法器资源就可实现对噪声过滤,使得FPGA 实现削峰技术具有可行性[8].

本文结合PC-CFR的特点及FPGA 的资源特性,对PC-CFR 算法进行了进一步改进,用查找表结构代替复杂的正余弦运算,实现了峰值削减系数的计算,用并行多削峰滤波器通道达到更强的削峰能力;根据时钟数据速率关系对乘法器进行复用,基于FPGA 搭建了LTE信号消峰处理平台,达到了比较好的性能指标.

1 PC CFR消峰技术

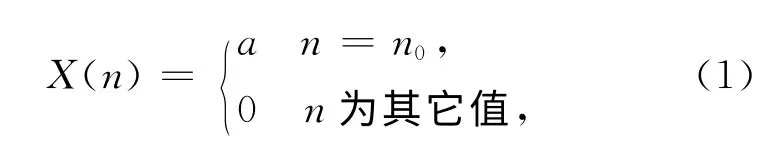

对于一个单脉冲信号

经过一个系数为h(n)={h0,h1,h2,…,hn}的N阶滤波器,其滤波器输出为

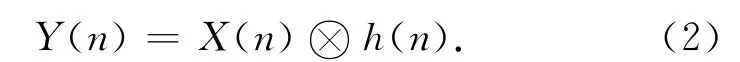

由于单脉冲信号X(n)仅在n=n0时等于a,其它时刻为0,因此卷积结果为

由式(3)可知,仅需用一个乘法器即可实现单脉冲信号X(n)经过N阶滤波器h(n)的滤波输出Y(n),提高了系统硬件实现的可行性.PC-CFR就是基于冲激响应的这种特性,对每一个超过消峰门限的峰值区间仅对该区间内的最大值进行消峰,大大节省了乘法器资源[9-11].

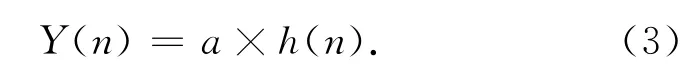

对于每一个峰值削减点,首先计算出该峰值削减系数

式中:c为复数;A是最大峰值点,且A=I+jQ;Ath是削峰门限.

通过削峰滤波器得到的削峰噪声,实际为一个复数乘法运算,即

在最大峰值点A与削峰噪声N(n)做复数减法,推导得出削峰后最大峰值点的峰值,即为削峰门限Ath.

对于多峰值情况,通过并行的削峰滤波器同时工作,把各个削峰滤波器的削峰信号累加,并与延迟后的原削峰数据相减完成削峰,各个峰值点削峰采用流水线结构操作.

削峰滤波器的系数对于单载波而言,是一个窄带滤波器;对于不同频点的多载波而言,可以用单载波窄带低通滤波器得到,其计算公式如下:

式中:M为载波数;N为滤波器长度;g(k)为单载波窄带低通滤波器系数;fs为信号采样率;fi表示第i个载波的中心频率.

2 基于FPGA 的LTE 信号的削峰系统设计与实现

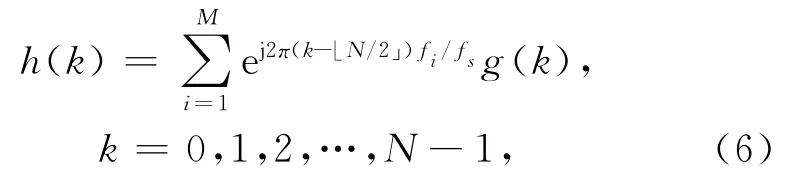

基于FPGA 实现LTE信号的削峰架构如图1所示,其主要包括峰值检测,峰值削减系数计算,削峰滤波器分配,多个并行的削峰滤波器,数据延迟等.在系统设计中,高峰均比数据首先经过峰值检测模块把超过门限的峰值点检测出来,然后进行峰值削减系数计算.在进行峰值消减系数计算时,采用查找表结构代替正余弦运算,得出峰值削减系数;而峰值滤波器分配模块是根据峰值的大小决定峰值点采用不同的削峰滤波器进行处理.同时,要保证同一削峰滤波器通道相邻两个待处理的峰值间距大于削峰滤波器系数的阶数,否则转到下一削峰滤波器处理;经过削峰滤波器处理后的数据经过复数累加计算,并与经双端口的RAM,即Dpram(dual-port RAM)延迟后的原削峰数据做复数减法,实现削峰.对于峰值密度比较高的LTE信号,或经过一级削峰后有再生峰值出现的信号,可能需要经过多级削峰才能达到要求的指标.

图1 FPGA 实现削峰架构Fig.1 Clipping peak scheme based on FPGA

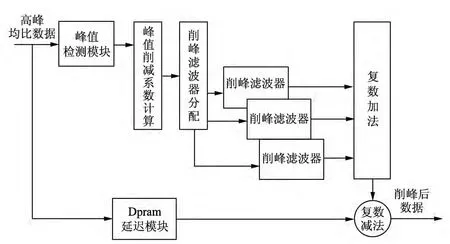

在削峰系统设计中,峰值检测是通过对输入信号I,Q进行计算,求其功率I2+Q2,然后与削峰门限进行比较.当该点功率大于削峰门限时,该峰值点才被认为是一个真正的峰值点,如图2的A,B,C,D,E点.

图2 有效峰值点检测示意图Fig.2 The schematic cheme of the detected available peaks

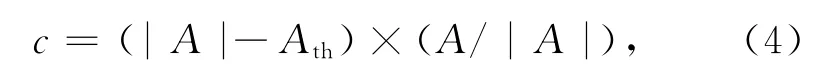

峰值削减系数的计算是削峰系统的关键环节,由式(4)可知,若直接计算峰值削减系数,需要一个除法或正余弦运算.由于FPGA 自身的特点,要实现除法或正余弦运算是比较困难的,因此有必要对峰值削减系数算法进行研究和改进.

经过研究,对式(3)做进一步的简化,有

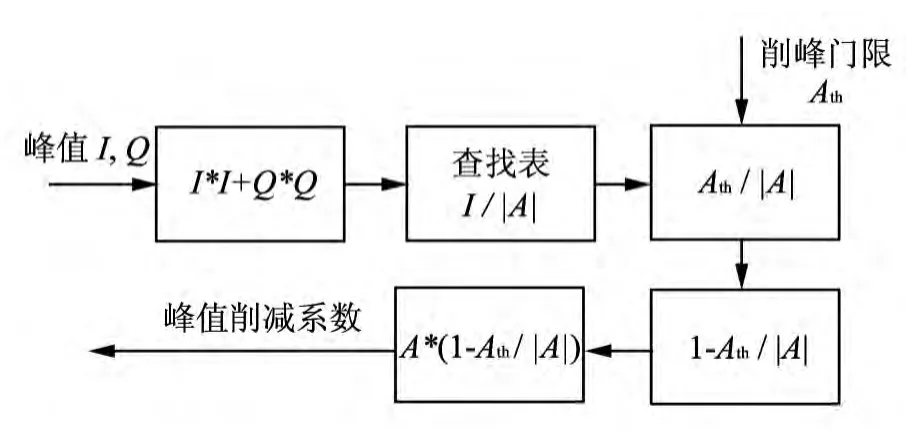

在FPGA 中实现峰值削减系数的计算,由式(7)可知,Ath/|A|可以通过查找表实现,查找表的地址用I2+Q2表示,这时峰值削减系数计算可通过一个Rom 查找表和乘法器实现,其具体算法流程如图3 所示.其中查找表的深度和宽度决定该系数的精度,在I和Q数据均为16bits的情况下,通过实验仿真,在FPGA 中当ROM 查找表深度为2 048个单元,宽度为24bit时,可满足精度要求.

一般情况下,每级削峰需要有多个削峰滤波器,通过削峰滤波器分配模块决定每个峰值具体通过哪个削峰滤波器进行数据处理,并产生与该通道相对应的峰值标志信号.峰值分配从通道0往后依次分配.在峰值分配时要保证同一个通道的相邻两个待处理的峰值距离必须要大于削峰滤波器系数的阶数.如果在各削峰滤波器通道处于忙状态时,要舍弃相应的峰值点,等下一级削峰进行处理.因此,对于峰值密度较高的信号,一级削峰往往不能得到理想的CCDF 特性,需要多级削峰迭代处理,但会导致EVM 恶化,需要综合折中考虑.

图3 峰值削减系数计算流程图Fig.3 The flow chart of the peak clipping coefficient calculation

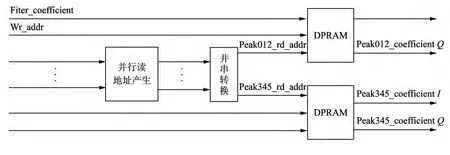

削峰滤波器主要实现复数乘法运算,对于FPGA 而言,硬件乘法器资源十分宝贵.因此,在FPGA 中,利用时钟数据速率倍数关系对硬件乘法器进行复用,以减小硬件资源的消耗.如在3倍时钟数据速率下,每级削峰模块采用6路削峰滤波器,可通过2个复数乘法器和2个Dpram 便可完成6路削峰滤波器的处理.为了满足不同带宽、不同制式的需求,削峰滤波器系数存储在双端口的RAM,即Dpram(dual-port RAM)中,由外围处理器控制,灵活可配.Dpram 复用处理过程如图4所示.

图4 基于FPGA 的Dpram 复用流程Fig.4 The float chart of Dpram multiplexing based on FPGA

削峰滤波器系数的设计直接影响输出信号的相邻信道功率比(ACPR)和误差向量幅度(EVM).在一般情况下,削峰滤波器保证邻道内衰减超过60dB,对ACPR 没有太大影响;同时,为了达到更好的削峰效果,减少对EVM 的影响,在设计滤波器时要尽可能保证冲激响应的主瓣宽度接近信号的过门限区间宽度和减少削峰滤波器的阶数,但这些指标互相矛盾,需找一个平衡点.

经过削峰滤波器的各个通道数据相加与经过Dpram 延迟后原数据相减后便完成了整个削峰处理.一级削峰由于削峰能力有限,往往存在摆尾和再生峰值.为得到比较好的CCDF 曲线特性,需要多级削峰迭代.

3 实验结果与分析

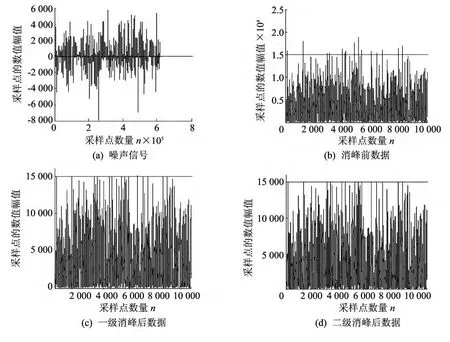

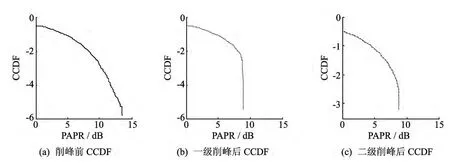

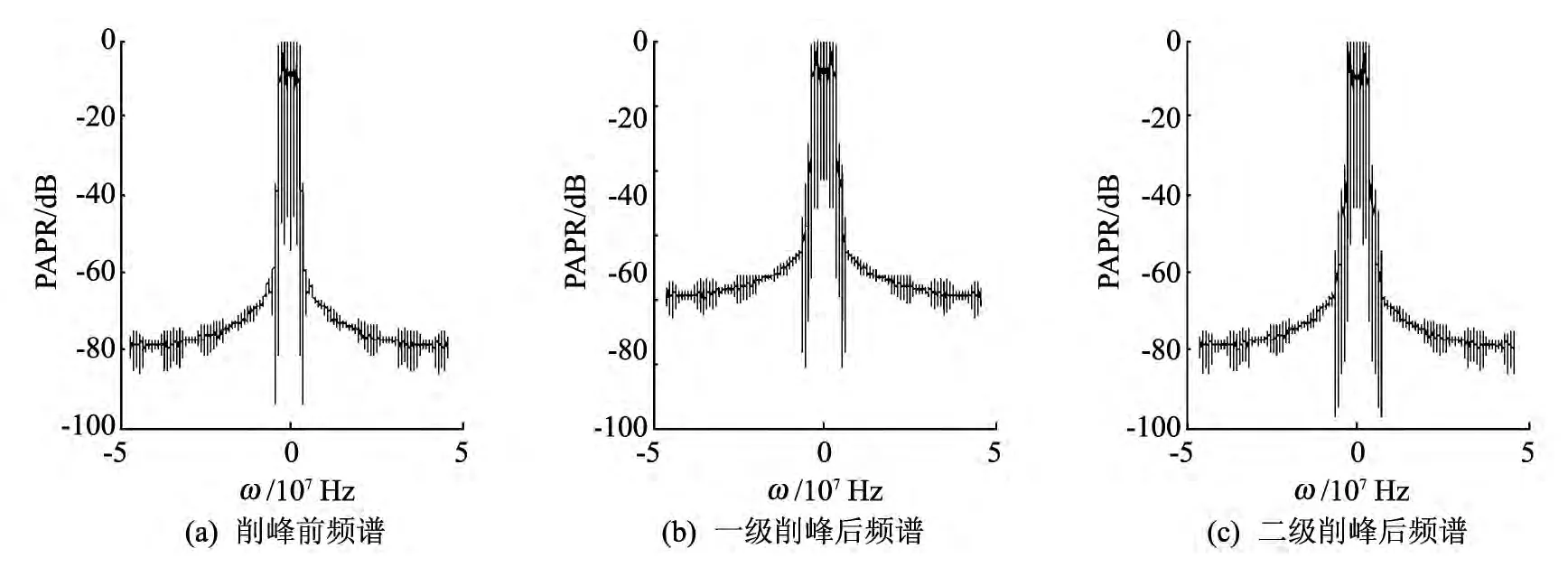

在系统带宽5 MHz,I,Q数据采样速率为61.44 MHz,原信号峰均比为13dB时,调制方式64相位正交调制(QAM),获得频分双工(FDD LTE)源数据.当 CFR系统工作时钟为122.88 MHz,CFR 两级迭代,每级6个削峰滤波器通道,削峰门限为15 000时,对获得的源数据进行一级和二级削峰处理,通过Matlab 软件仿真,其结果如图5~7 所示.

图5 削峰前后信号时域图Fig.5 The signal graph around clipping peak in time domain

图6 削峰前后CCDF的比较Fig.6 The comparison of CCDF around clipping peak

图7 削峰前后频谱对比Fig.7 The comparison of spectrums around clipping peak

由仿真结果可知,两级削峰后CCDF 曲线特性良好,削峰效果明显,输出频谱正常;同时,通过一级削峰后EVM 恶化4.2%,二级削峰后恶化到4.8%,满足LTE协议对64QAM 调制下EVM小于8%的要求.

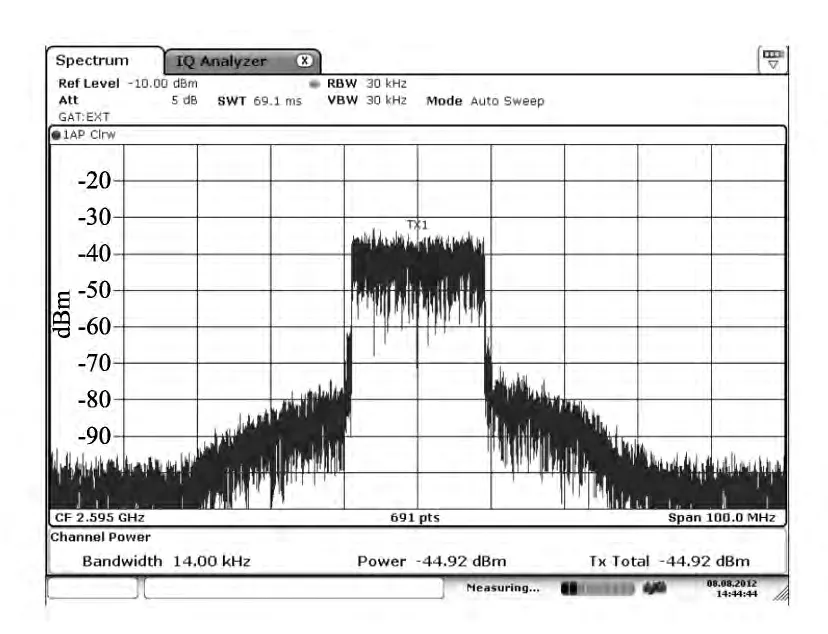

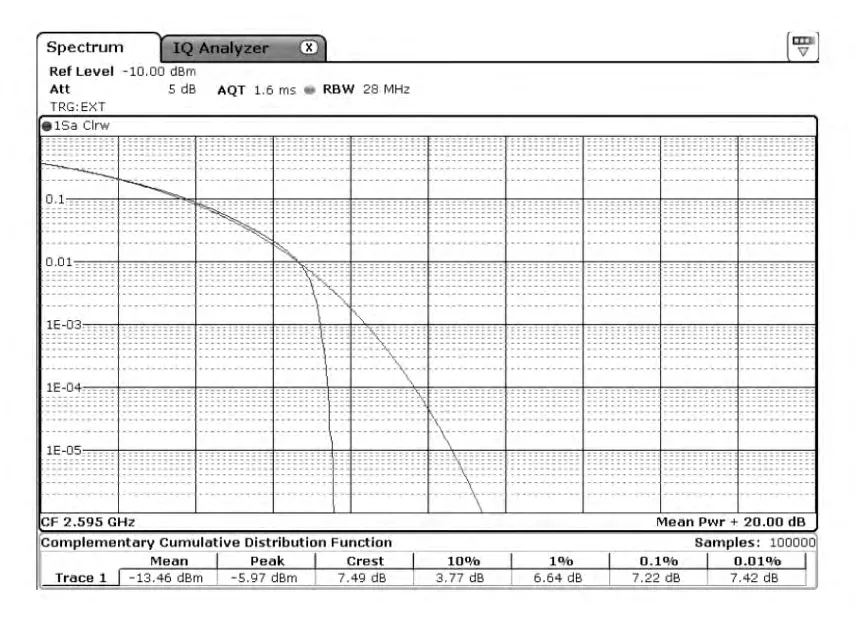

为进一步验证CFR 性能,搭建了FDD-LTE数字中频系统验证平台,系统带宽20 MHz,IQ数据采样速率为61.44 MHz,CFR 系统工作时钟采用122.88MHz,CFR 经过两级迭代,每级6个削峰滤波器通道.在不考虑DPD(数字预失真)的情况下对系统输出的中频数据进行分析,由频谱仪获得的频谱图和CCDF图如图8 和图9 所示.

图8 20 MHz时的带宽信号PAPRFig.8 PARR of 20 MHz signals

图9 7.4dB时的信号频谱、CCDF曲线Fig.9 The signal spectrum and CCDF curve at 7.4dB

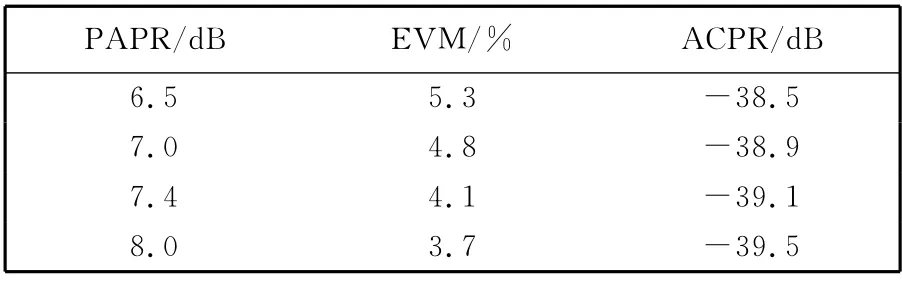

在更改削峰门限,不同峰均比时,获得的各 项指标如表1 所示.由表1可知,通过FPGA 实现削峰可以达到比较好的削峰性能.

表1 不同峰均比时的EVM,ACPRTab.1 EVM,ACPS which appeared at different PAPR

4 结论

本文基于LTE信号高峰均比的特点和削峰原理,设计了一种适合FPGA 实现的削峰方法.该方法在考虑FPGA 的硬件资源特性的基础上,通过采用ROM 查找表和乘法器实现了消峰系统的计算,并利用时钟数据速率倍数关系对硬件乘法器进行复用,减小了硬件乘法器资源.同时充分考虑了不同带宽、不同制式下的兼容问题,削峰滤波器系数可灵活可配,削峰级数可多级迭代,满足了不同的场景需求.通过实际系统验证表明,该系统削峰能力强,削峰后对EVM,ACPR 等指标恶化不大.

[1]Krongold B S,Jones D L.An active-set approach for OFDM PAR reduction via tone reservation[J].IEEE Transaction on Signal Processing,2004,52(2):495-509.

[2]Yang L,Chen R S,Siu Y M,et a1.PAPR reduction of an OFDM signal by use of PTS with low computational complexity[J].IEEE Trans.on Broadcasting,2006,52(1):83-86.

[3]Tao J,Xiang W D,Richardson P C,et a1.PAPR re-duction of OFDM signals using partial transmit sequences with low computational complexity[J].IEEE Trans.on Broadcasting,2007,53(3):719-724.

[4]Lim D W,Heo S J,No J S.A new PTSCFDM scheme with low complexity for PAPR reduction[J].IEEE Trans.on Broadcasting,2006,52(1):77-82.

[5]Xiao Peng,Xiong Jun.Method and device for signal peak cancellation.WO2011103809A1[P].2011-02-24.

[6]Hemphill A,Summerfield S,Wang G,et al.Peak Cancellation Crest Factor Reduction Reference Design[M].Application Note:Virtex-5and Virtex-4Family,2007.

[7]乔温蔚.OFDM 系统峰均比抑制技术研究与FPGA 实现[D].西安:西安电子科技大学,2011.

[8]Tellambura C.Use of M-sequences for OFDM peak to average power ratio reduction[J].IEEE Electronics Letters,2006,33(15):1300-1301.

[9]韩庆文,谷友方,王韬.基于联合算法的OFDM 峰均比降低技术[J].计算机工程,2011,37(4):112-115.Han Qingwen,Gu Youfang,Wang Tao.OFDM PAPR reduction technology based on union algorithm[J].Computer Engineering,2011,37(4):112-115.(in Chinese)

[10]胡海丰,赵新建.降低OFDM 系统峰均比技术的研究[J].计算机仿真,2011,28(2):151-154.Hu Haifeng,Zhao Xinjian.Research on PAPR reduction in OFDM system[J].Computer Simulation,2011,28(2):151-154.(in Chinese)

[11]王立波,王永生,王宇.利用子块时域优化组合降低OFDM 系统峰均比[J].电路与系统学报,2010,15(3):129-133.Wang Libo,Wang Yongsheng,Wang Yu.OFDM peak-to-average power ratio reduction by subblock time permutation[J].Journal of Circuit and Systems,2010,15(3):129-133.(in Chinese)