4×6 M IMO信道解码器的FPGA设计与实现

2014-11-20蔺吉顺刘东华

蔺吉顺,刘东华

(内蒙古民族大学机械工程学院,内蒙古通辽028000)

多输入多输出(MIMO)技术相对于传统的单天线系统来说,能够大大提高系统容量和频率利用率,能够在有限的无线频带下传输更高速率的数据,在现代无线移动通信系统中得到了广泛应用[1]。虽然MIMO的概念已经提出有几十年,但由于无线移动通信MIMO信道是时变非平稳系统,有大量问题需要研究。此外,由于MIMO系统的容量和信息传输速率与输入输出天线数密切相关,但天线数越多,MIMO信道估计和接收机解码就异常复杂,计算量大[2]。为实用化MIMO系统,设计了一种针对发射机天线数为4、接收机天线数为6的4×6 MIMO信道解码器并在Xilinx Vertix6系列FPGA芯片上进行了设计验证。该系统与OFDM技术结合,可以用于实现信息速率为1.485 Gbit/s的HDI高清视频的无损实时传输。

1 MIMO原理

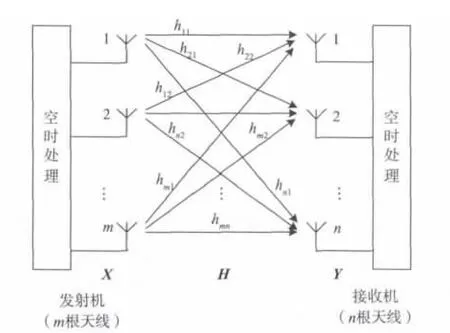

典型的MIMO系统如图1所示,包含m根发射天线和n根接收天线。

根据无线信道的特点,每根接收天线都会收到所有发射天线的内容,因此不同收发天线之间均构成信道,且具有不同的表现形式。若定义发射机和接收机各天线信号组成的矢量分别为 X=[X1,X2,…,Xm]T和 Y=[Y1,Y2,…,Yn]T,则 MIMO 无线通信模型可以表示为

式中,H是大小为m×n为信道传输矩阵,矩阵元素hij,(i=1,2,…,m;j=1,2,…,n)表示第i根发射天线和第j根接收天线之间的信道冲激响应。Z矩阵表示高斯噪声。

图1 MIMO系统

2 MIMO解码

OFDM-MIMO系统中信道估计主要有基于分散导频、正交导频和分组导频等方法,其中分散导频广泛应用于快衰落和频率选择性衰落信道中[3]。采用分散导频时,MIMO信道估计首先将接收到的导频序列与发端导频序列相乘,得到基于导频的信道频率响应(CFR)序列,然后做反傅里叶变换(IFFT),得到信道脉冲响应(CIR)序列;最后将CIR序列分成相等的m段,每段对应一对收发天线的估计CIR,补零后再进行IFFT变换即得到所有天线信道响应的估计[4]。

这里采用最小均方误差算法(MMSE)准则进行OFDM-MIMO信道估计。MMSE估计在最小二乘估计(LS)的基础上进行。最小二乘估计的代价函数为

MMSE估计的代价函数为

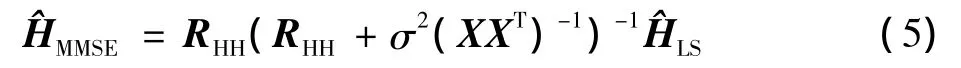

MMSE估计的信道估计值可以表示为

3 FPGA设计

3.1 设计考虑

3.1.1 数据精度

本文给出的MIMO解码器针对发射天线数为4、接收天线数为6的OFDM-MIMO系统设计,假设OFDM系统采用基于训练序列的同步方式。由于MIMO处理过程中数据动态范围较大,采用定点量化实现时会使系统性能严重降低,因此考虑采用全浮点设计,基本运算单元采用Xilinx提供的IP核实现。

3.1.2 数据缓存

另外,为保持系统的实时性和节省存储资源,应该在接收到训练序列后尽可能在较短时间内完成信道估计并计算出式(6)中的,这样才能减少接收数据序列的存储要求,如图2所示。

图2 MIMO解码时间示意图

MIMO信道估计和解码针对每一帧数据进行,在接收到训练序列后立即开始信道估计,在得到信道估计结果后才能针对每个接收数据序列计算。但是在信道估计和计算时,必须缓存数据序列,这是因为计算结果滞后于接收的第一个数据。为保证数据处理的顺序性,必须采用先入先出的FIFO进行数据缓存。

3.1.3 矩阵求逆

在OFDM-MIMO系统中信道估计和MIMO解码都涉及到矩阵求逆运算,由于信道都是浮点复数类型,因此基于初等变换的矩阵求逆的计算量很大,几乎无法在FPGA上实现。因此这里针对4×6矩阵与其转置相乘后得到的4 ×4 矩阵 A=[aij](i,j=1,2,3,4)的求逆采用如下算法分3 步计算其伴随矩阵 B=[bij](i,j=1,2,3,4)和行列式的值。

第一步,计算中间变量ci(i=1,2,…,24)

c1=a33×a44-a34×a43;c2=a11×a22-a21×a12;

c3=a23×a34-a24×a33;c4=a11×a42-a41×a12;

c5=a13×a44-a14×a43;c6=a21×a32-a31×a22;

c7=a23×a44-a24×a43;c8=a31×a12-a11×a32;

c9=a13×a24-a14×a23;c10=a31×a42-a41×a32;

c11=a13×a34-a14×a33;c12=a41×a22-a42×a42;

c13=a32×a44-a34×a42;c14=a22×a44-a24×a42;

c15=a22×a34-a24×a32;c16=a12×a44-a14×a42;

c17=a12×a34-a14×a32;c18=a12×a24-a14×a22;

c19=a32×a43-a33×a42;c20=a22×a33-a23×a32;

c21=a12×a43-a13×a42;c22=a12×a33-a13×a32;

c23=a22×a43-a23×a42;c24=a12×a23-a13×a22。

第二步,利用aij(i,j=1,2,3,4)和ci(i=1,2,…,24)计算矩阵A的伴随矩阵

b11=a22×c1-a32×c7+a42×c3;

b12=a32×c5-a12×c1-a42×c11;

b13=a12×c7-a22×c5+a42×c9;

b14=a22×c11-a12×c3-a32×c9;

b21=a31×c7-a21×c1-a41×c3;

b22=a11×c1-a31×c5+a41×c11;

b23=a21×c5-a11×c7-a41×c9;

b24=a11×c4-a21×c11+a31×c9;

b31=a21×c13-a31×c14+a41×c15;

b32=a31×c16-a11×c13-a41×c17;

b33=a11×c14-a21×c16+a41×c18;

b34=a21×c17-a11×c15-a31×c18;

b41=a31×c15-a21×c19-a41×c20;

b42=a11×c19-a31×c21-a41×c22;

b43=a21×c21-a11×c23-a41×c24;

b44=a11×c20-a21×c22+a31×c24。

第三步,利用ci(i=1,2,…,24)计算行列式的值

|A|=c1×c2+c3×c4+c5×c6+c7×c8+c9×c10+c11×c12。

在得到伴随矩阵后除以行列式的值即得到逆矩阵。

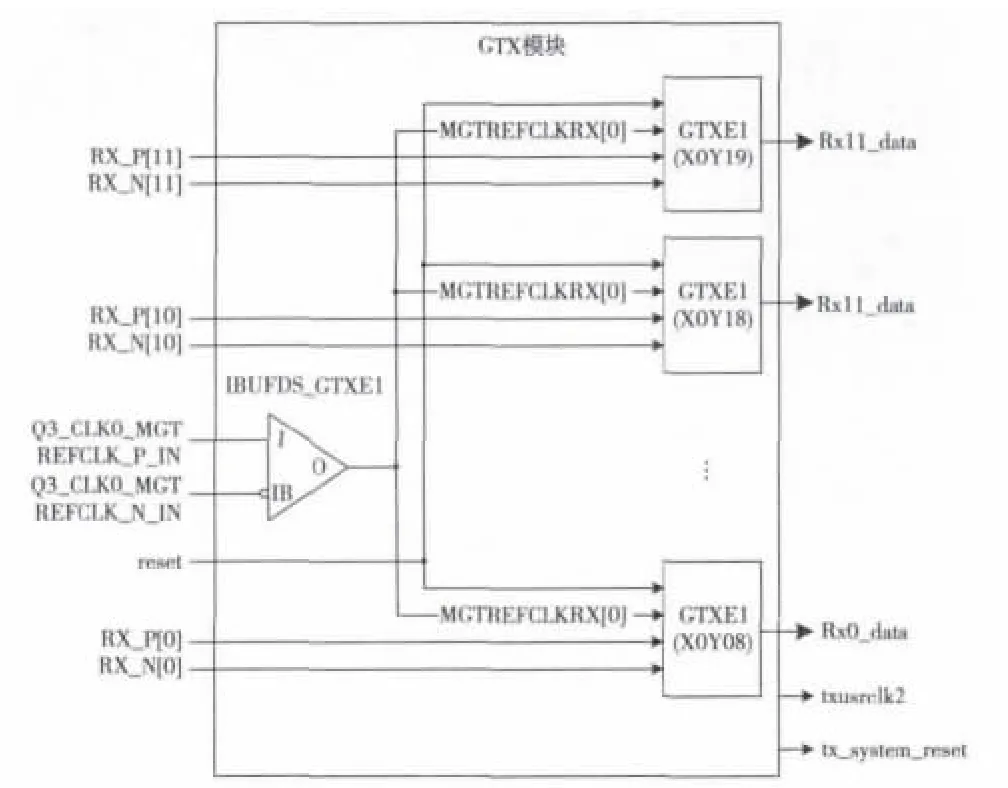

3.2 MIMO解码的FPGA设计结构

考虑到4×6信道矩阵与其转置相乘后得到的矩阵为对称矩阵,将式(6)的计算分解为如下4步:1)计算A=·;2)计算B=A*;3)计算|A|和 G=B/|A|;4)计算X=Y·G。其中G矩阵的结果需要存储,用于在时间顺序上计算X。总体设计框图如图3所示。

图3 MIMO解码的FPGA总体结构

输入数据经Xilinx FPGA高速串行端口GTX送入模块,根据图2,首先将训练序列和数据序列分离(通过标记信号实现),其中数据序列送入FIFO缓存;训练序列数据送入CSI模块(这里不做讨论)进行信道估计计算,得到的信道估计结果CH_est进入缓存,在信道估计完成后从RAM读出数据并用定点(浮点转换IP核转换成浮点数据后送入 ACal、InvBCal和 GCal模块完成上述 1)、2)、3)步运算后送入,同时从FIFO缓存中读取对应位置的输入数据(经过定点(浮点转换),在DmmseCal模块中完成步骤4)的计算;最后得到的结果经过浮点(定点转换后经IO端口输出。MMCM模块为时钟生成模块,用于实现时钟速率转换[5]。设计过程中,充分考虑芯片计算资源、存储资源和模块处理速率的关系,设计了基于流水和复用的模块实现机制。下面逐个说明各主要模块的功能和关联关系。

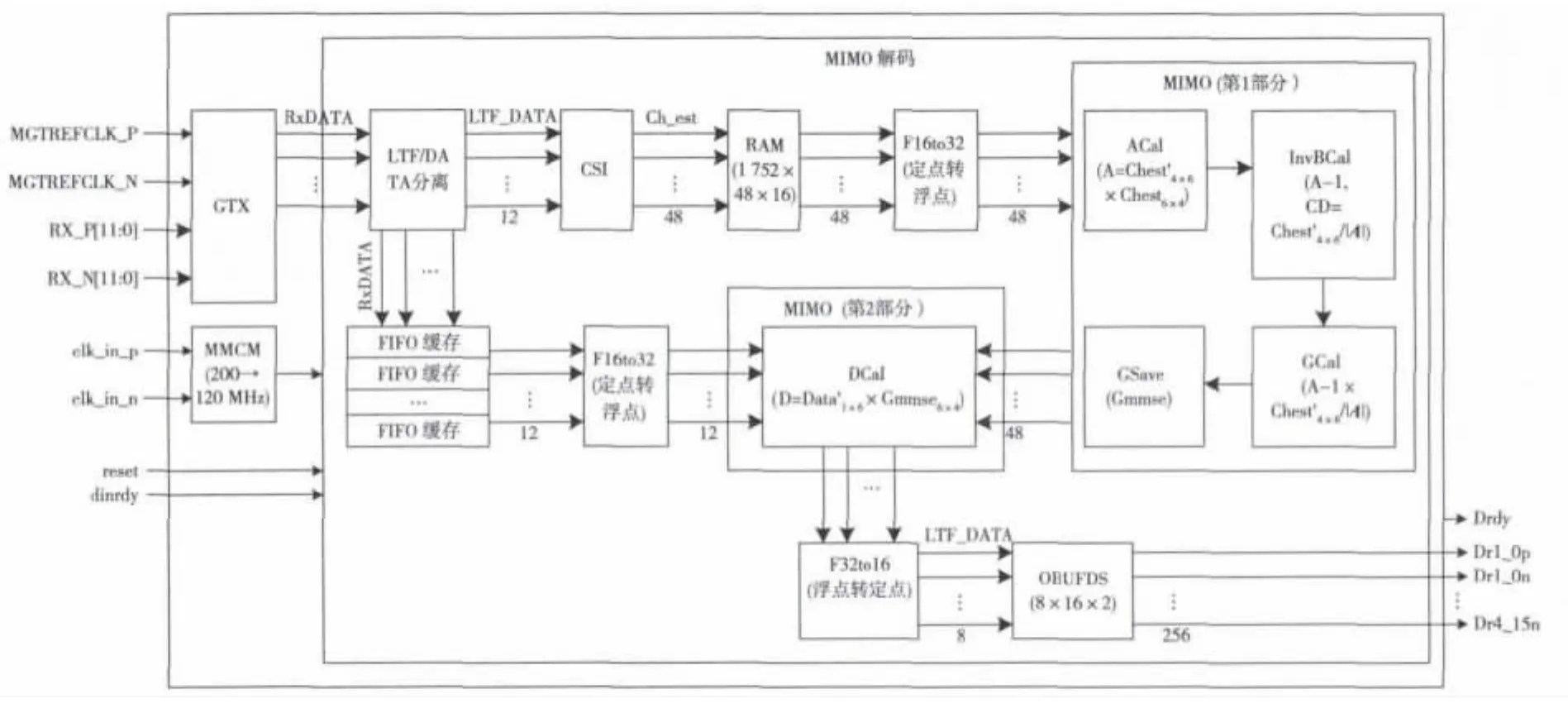

3.2.1 输入接口

模块的输入接口采用Xilinx提供的高速串行接口GTX硬核实现,Xilinx Vertix6 GTX可以达到最高6.6 Gbit/s的传输速率,满足速率为1.485 Gbit/s GDI信号的传输要求。对于6路接收复信号,实部和虚部信号分别传输,故使用12个GTX模块,输入数据为LVDS形式,以保证信号的稳定性。接口模块的设计结构如图4所示。

图4 GTX接口设计

Xilinx Vertix6 FPGA提供20个GTX模块,每4个1组,共用1组时钟,且相邻组也可以共用1组时钟,故选择第9~20个GTX模块实现。

3.2.2 计算模块

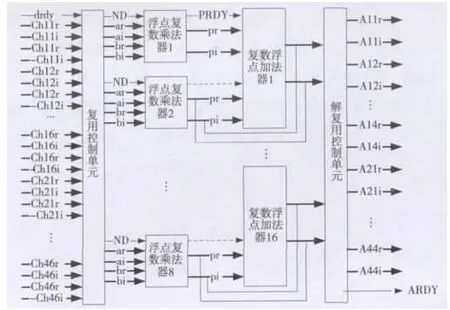

根据上述分析可以看出,在 ACal、InvBCal、GCal和GmmseCal模块中主要实现复数浮点乘法和加法。各模块的设计结构基本相同,这里以ACal计算模块为例进行说明。ACal模块用于计算A=·,设计结构如图5所示。

图5 ACal模块结构

模块输入为4×6路信号,对于k时刻的信道估计矩阵,实部和虚部分别输入,drdy为控制信号。为节省资源,对矩阵运算过程进行复用,对于有2 048个子载波的OFDM系统,共调用8个浮点复数乘法器(每个由4个复数乘法器和2个复数加法器组成)进行矩阵元素乘法运算和16个复数加法器实现累加,复用12次,延时56个时钟周期。得到结果矩阵的元素值,在输出之前还要将结果解复用。仿真结果如图6所示。

图6 ACal计算模块的仿真结果(截图)

3.2.3 FIFO 缓存模块

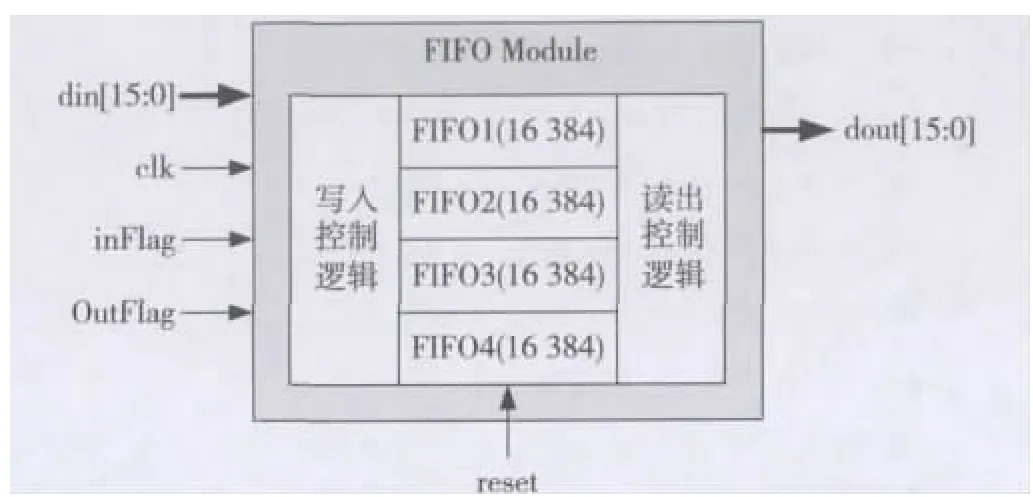

XilinxFPGA芯片提供FIFO缓存器,且缓存深度可设置。根据本设计的处理速率和信道估计与MIMO解码所需处理延时,存储的数据量较大。当FIFO深度较大时将严重影响系统处理速率,因此这里采用级联FIFO缓存机制,采用4级深度为16 384、位宽为32 bit的FIFO实现。组成结构如图7所示。

图7 FIFO级联设计结构

其中FIFO1~FIFO4由Xilinx LogiCORETM IP核生成,读写控制逻辑独立实现,数据循环写入和读出,不使用FIFO的空满信号控制,从而保证FIFO控制的灵活性。

3.3 资源统计

图8给出了在Xilinx Veritex6系列FPGA芯片Xc6vsx315tff1156-1上实现MIMO解码时占用的资源统计结果及可达到的处理速率,由PlanAhead仿真给出,与在芯片上实现的结果一致。

图8 MIMO译码的总资源和速率仿真结果(截图)

3.4 结果分析

该MIMO解码器应用于某OFDM-MIMO宽带无线传输系统中,实现了速率为1.485 Gbit/s的HDI高清视频的无压缩传输。具体参数设置为:OFDM子载波数为2 048,数据载波数为1 740,导频数为12,64QAM 调制,(710,620)RS纠错码,4路信号并行发送,每路数据速率为120 MHz,信息传输速率为1.5 Gbit/s。在步行移动速度条件下,数据准确传输距离达到了100m以上。

4 结论

MIMO作为一种在现代无线移动通信系统中最有应用前景的技术得到了广泛重视和研究。本文针对高速率视频无线传输的要求,在研究MIMO解码原理的基础上,综合考虑硬件实现的数据处理速率、系统性能和资源使用的平衡,设计了全浮点化的4×6 MIMO解码器,并在Xilinx公司的Xc6vsx315tff1156-1 FPGA芯片上实现验证,达到了120 Mbit/s以上的处理速度,有很好的参考意义和工程应用价值。

[1]罗涛,乐光新.多天线无线通信原理与应用[M].北京:北京邮电大学出版社,2006.

[2] NEE L,PRASAD R.OFDM for multimedia wireless communications[M].Boston,MA:Artech House,2000.

[3]李夏.MIMO-OFDM试验系统同步算法VLSI实现技术研究[D].成都:电子科技大学,2010.

[4]孙亮,郭金京,王亚峰,等.一种新的基于参数信道模型的MIMO信道估计算法[J].电子与信息学报,2007(5):1145-1149.

[5]武钢.多入多出无线通信中的信道模型、空时编码及关键技术研究[D].成都:电子科技大学,2004.