可重构计算平台的硬件结构设计

2014-11-20朱志宇

吴 将,朱志宇,沈 舒

(江苏科技大学电子信息学院,江苏镇江,212003)

运行在冯·诺依曼或哈佛结构[1]设计的计算机处理器上的软件都被编译成一组特定处理器指令,而这些指令都是在运行软件时加载并顺序执行[2],这样顺序处理的指令对一些数据处理要求较低的PC应用只需几个时钟周期,然而,PC也经常用来处理一些计算密集型高吞吐量的数据,特别是在科学研究工作方面,在这种情况下典型PC处理器的顺序执行性就不能有效实现,因此需要使用更快速的处理器或者一个集群或计算网络[3]。如今,更多的则是运用可重构硬件(如FPGA)处理计算密集型数据,这种硬件体系结构与典型的冯诺依曼或哈佛类型处理器完全不同,应用FPGA执行算法时,通常将算法定义为硬件描述语言并编译成信号,并将信号下载到FPGA实现。信号下载到FPGA时,硬件逻辑将重构,该过程允许数据传输和FPGA硬件处理并行执行[4]。现有多数可重构平台都是采用多片FPGA的结构,这种可重构平台可能还包含多个CPU或专用存储器,FPGA的配置往往是整片重构或者是一维重构,而且需要一块独立的开发板来提供外设并控制重构过程,这样的设计成本高、配置时间长、灵活性也受局限。为了降低可重构计算平台的配置时间,并且提高平台的灵活性,本文给出了一种基于PC机的可重构硬件平台的设计方法。

1 设计要求

为了进行硬件结构设计,首先应该了解具体的设计需求和期望的系统性能。第一,可重构计算平台是基于PC机设计的,PC机通过总线(如 PCI-33,PCI-X,FireWire或者USB)访问FPGA,要使得处理数据和FPGA重构信号传输速度足够快就必须选择合适的总线,因为PC总线接口标准是各种各样的,在PC端其他标准可用时,PC接口的核心即可切换到其他标准。第二,本文的主要工作就是开发一个能够通过PC机快速重构FPGA的系统,即以运行在PC机上的软件仿真平台[5]作为处理器,当需要时可以下载重构算法信号到FPGA。当处理算法链将结果返回给PC机之前,数据在FPGA上通过特定的算法进行处理,而且重构FPGA以待处理下一步的算法链数据,快速重构可以减少重构过程中的延迟。第三,运用尽可能少的元件设计出理想并简单的物理硬件,这将使得这个平台的开发成本较低,在同一FPGA同时运行PC机接口核心和算法实现能够实现该要求,即使FPGA存储算法和PC机接口在同一芯片上运性,但是部分FPGA存储算法应该动态可重构并且独立于PC机接口。由于软件平台允许多个硬件模块并行使用FPGA,所以为了保持硬件设计简单,不需要用多个FPGA来实现各个硬件模块。虽然已经有人开发了可重构平台结构,但是没有一个满足以上所有要求。例如,Blodget[6]等设计了一个利用内置FPGA的软处理器核心代替外部PC机的自动重构的嵌入式系统平台,Fong等[7]开发了一种采用RS-232端口传输可重构数据到FPGA的系统,但是限制该系统重构性能的一个关键因素就是传输速度低。

2 系统设计

考虑到第1节中的设计要求,运用PCI总线和自重构FPGA Xilinx VirtexⅤ来设计硬件结构。典型PC机都配备有PCI总线,而且硬件设备可以完全由总线本身进行供电,这将减少额外供电电路的设计,同时还避免了PCI信号中的电流分离问题。此外,高吞吐量的总线(32位、33 MHz的PCI总线的速度为132 Mbit/s)使得从PC机到FPGA重构信号的传输速度更快。通过SelectMap总线传输信号到可重构FPGA的最大速度是50 Mbit/s,因此PCI总线可以满足SelectMap总线的所有操作都是在它的最大速度下进行。可重构FPGA运用其部分资源来控制PCI接口,而其他部分资源用来执行下载的算法,这就不需要单独设计PCI接口芯片,从而使得硬件模块非常简单,这种方法还可以减少由物理连接点导致的系统故障的数量。同时,尽管PCI接口和算法在同一FPGA上执行,但是FPGA的模块化设计流程[8]允许两者独立开发和测试。这些功能的结合满足以下3个要求:使用同一个普通PC机总线标准、快速FPGA重构时序和一个简单的物理硬件模块,下面将详细介绍系统的结构框架。

2.1 物理硬件设计和初始启动配置

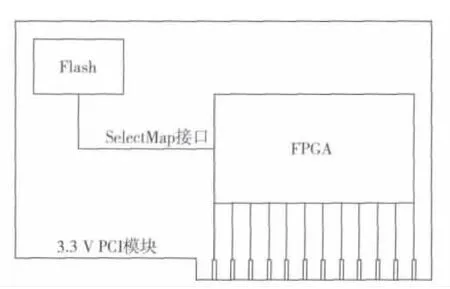

正如上文所述,物理硬件要尽可能简单,因此本文给出的硬件模块主要由FPGA和Flash RAM芯片组成,如图1所示。为了满足PCI规范对信号线路长度的要求,将FPGA放置在尽可能接近PCI接口的位置。闪存芯片中存储的是FPGA的初始配置信号,当SelectMap接口上电时将该信号下载到FPGA,基于SRAM的FPGA失电时配置信号就会丢失,所以需要通过闪存存储配置信号,初始配置信号控制PCI接口芯片和自重构控制器。一旦初始配置完成,主机PC就会根据算法需要通过PCI总线下载部分比特流到可重构FPGA。

现有的可重构硬件平台一般都是用多个FPGA设计实现,本文给出的硬件设计只用一片FPGA即可实现,但是这也会引入一些额外问题,比如:芯片内部连接、通信协议规范、任务分配等。近年来随着FPGA可用资源的增多,一片FPGA即可实现复杂算法,这种单一芯片解决方案的好处是不需要考虑FPGA各个模块设计的复杂性,而且将按线路发送的内部芯片信号线的通信限制转换为算法设计。

图1 物理硬件组成

2.2 单一芯片结构的FPGA划分

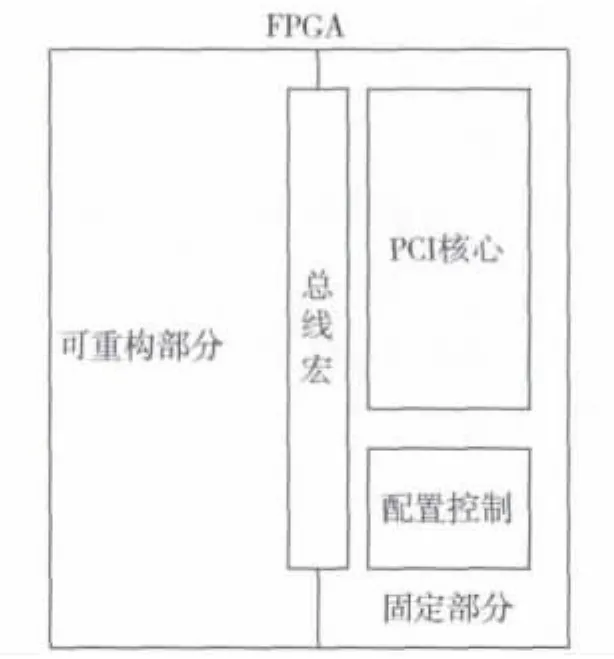

同时处理PCI总线和算法的单个FPGA芯片可以划分为以下2个部分:固定部分和可重构部分。固定部分包括PCI核心和配置控制器,而且启动时通过Flash下载到FPGA的配置比特流进行初始化,可重构部分根据算法通过PC机下载的比特流进行动态重构。运用FPGA设计部分可重构系统时,固定部分配置控制器在可重构部分内部执行动态重构操作,这两部分是通过总线宏[9]进行连接,该指令给出了物理接口信号线的定义,划分的FPGA由4个主要部分组成,如图2所示。

图2 FPGA分区图

2.3 模块化设计流程

在实现算法的可重构部分时,每次都将整个设计(包括固定部分)当作一个整体进行编译和测试,这种方法是不可取的而且也很麻烦。FPGA模块化设计流程中,每个模块(包括固定部分和可重构部分)独立进行开发、测试和调试,只有预留模块区域和总线宏接口必须保持一致,并且通过用于单一模块设计的顶端信息进行定义。模块边界是通过用于布局布线步骤模块区域进行定义的,而逻辑位置和信号路由以外的区域都是无效的。对于单个模块设计需要生成一个对单个模块配置信息的部分比特流,可重构部分根据算法生成该部分比特流,并由PC机下载FPGA动态重构相应的部分。全部比特流由顶端和固定部分设计生成并存储在闪存中用于FPGA初始启动配置。

2.4 运用内部配置访问通道(ICAP)自动重构

固定部分的配置控制器通过FPGA的ICAP执行自动重构[10],并且这一过程的执行不受主机CPU的影响。配置控制器通过PC机共享内存获得可重构数据,这可以避免FPGA芯片上的可用内存对配置比特流大小的限制。而其他可重构系统则是运用有限的片上内存来存储可重构数据,由于需要反复加载配置比特流,并逐步重构FPGA的部分区域,因此可重构过程的时间就会很长。第二个限制是发送可重构比特流线路的吞吐量,如果使用低吞吐量的传输线路就会限制可重构的速度,比如RS-232串行线。本文中PCI核的Busmaster直接使用PC机的内存来存储整个配置比特流,通过PCI总线传输到ICAP的数据是一个连续数据,这就消除了重构增量,并且高吞吐量的PCI总线使得重构速度更快,ICAP通过SelectMap总线协议将配置控制器用作为ICAP与PCI总线之间的一个桥梁。为了给各个模块提供独立的时钟,把片上双向端口的RAM模块设定为缓冲区,该方法避免了PCI接口和SelectMap接口之间共享RAM空间使用权的交换,因此最大限度地缩短了访问ICAP的时间。该模型实现使用FPGA的2个BRAMS,总的缓冲区大小为256×32 bit。配置控制器内部采用与PCI总线宽度相同的32位,为了通过8位的SelectMap总线,运用一个多路复用器将这32位分隔为4个单字节项,在这个过程中,当PCI总线不能提供足够的数据缓冲区时,控制器通过停止配置时钟暂停操作,一旦再次获得数据就会恢复操作。

2.5 固定部分设计

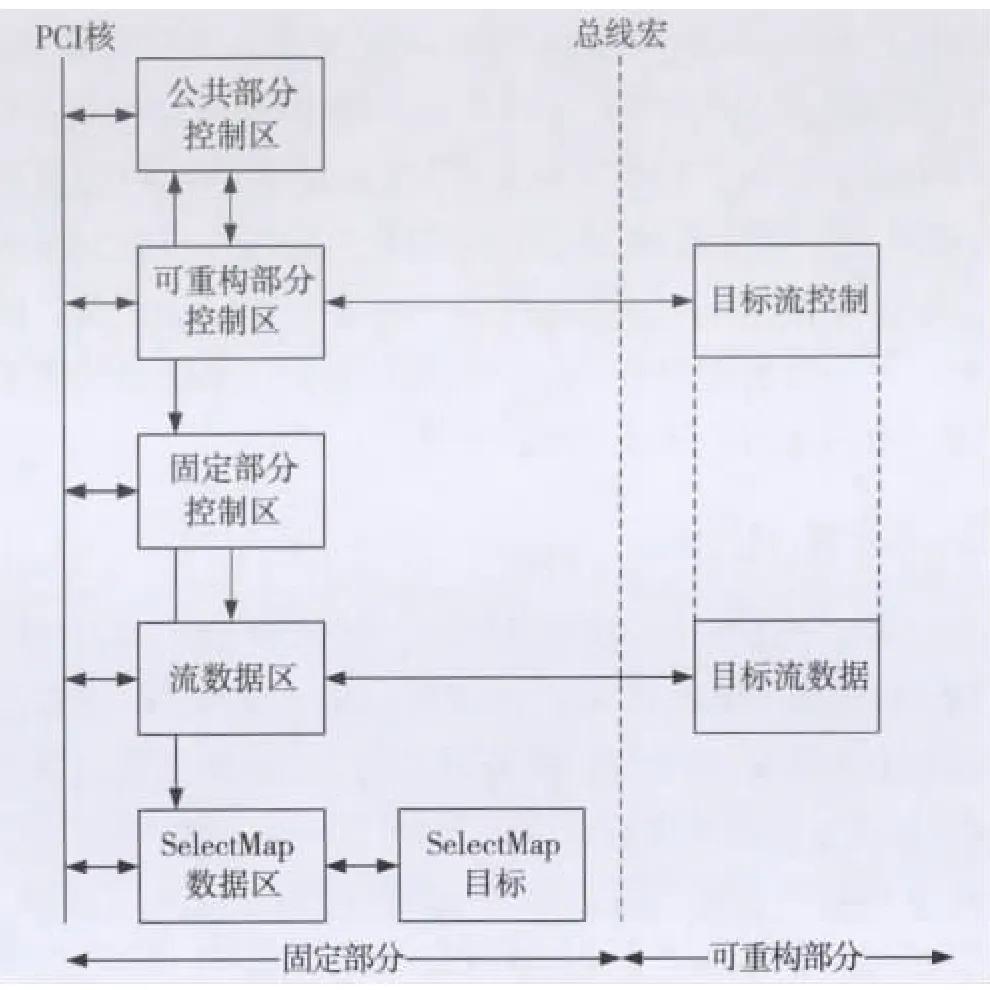

PCI接口将部分重构比特流传输到FPGA,并将算法下载到FPGA来交换数据,而这两种数据的传输都是通过PCI总线的Busmaster来完成,因为Busmaster可以直接访问PC机的共享RAM获得数据。这确保了FPGA设计片上内存小的限制,并且还为PC的直接数据传输提供了最快的速度,固定部分的设计如图3所示。固定部分主要由以下几个部分组成:固定部分控制区、可重构部分控制区、公共部分控制区、流数据区和SelectMap数据区。

固定部分访问PCI总线的Busmaster,控制所有驱动设备之间通信和从PCI总线到可重构部分(或者可重构部分到PCI总线)的数据传输。固定部分作为共享PCI总线面向数据包的传输和可重构部分连续数据流传输之间的一个桥梁。固定部分分为以下3部分控制:公共部分控制区、可重构部分控制区和固定部分控制区,而2个数据部分包括流数据和SelectMap数据。公共部分控制区有PCI的特定访问功能并且包含中断生成逻辑。可重构部分控制区使得可重构部分的静态寄存器很容易实现,该寄存器使得读取和写入单独处理,运用这些寄存器,可重构部分可以从PC机端和返回状态信息报告获得设置值,可重构部分还可以通过固定部分设计调用中断。固定部分控制区控制PCI总线和可重构部分之间的数据传输任务。数据部分控制PCI总线和可重构部分之间的从双端口RAM模块(BRAMs)到缓冲区之间的数据,双端口特性允许BRAMs访问不同时钟域的两侧,一个端口访问PCI侧并由PCI时钟驱动,而另一端口访问可重构部分并由其时钟驱动。为了满足PCI总线的访问延迟时间,缓冲区的大小设定为256×32 bit,固定部分控制区的功能模块如图4所示。

图3 固定部分设计

图4 公共部分控制区功能模块图

由图4可见固定部分控制包括一个Busmaster启动程序和Busmaster地址生成程序,其中Busmaster启动程序通过PCI总线在PC机上对RAM进行分配从而实现Busmaster的数据传输,这一过程触发内部BRAM缓冲区为满状态。Busmaster地址生成程序跟踪PCI寻址,又因为在共享PCI总线上的数据传输在任何时候都可以被中断,所以这种跟踪是必需的,当中断发生时,只有当总线再次可用才可在下一地址到来时重新启动数据传输。

数据传输中枢模块通过4个目标数据流对PCI接口进行调度,而这4个目标数据流分别是上行数据流、下行数据流、读SelectMap和写SelectMap,这4个目标在同一个PCI接口实现,因此数据传输中枢模块通过一个简单调度算法实现公平分配数据传输申请,该调度算法的具体要求是:当有多个申请在等待时,同一个目标不可以连续2次对PCI接口发出申请。每个数据流目标有一个与之相对应的控制区,该控制区生成数据传输申请并监视数据区BRAM缓冲区的状态。

3 实验结果

对于上一节中描述的固定部分设计,运用Xilinx ISE 13.2这一编译软件对型号为XC5VLX50T的FPGA进行程序编译,FPGA的区域ISE布局规划如图5所示,其中白色部分为固定部分,而灰色部分为可重构部分。图6给出了固定部分的资源使用情况,固定部分一共使用的模块数为2 211,而这一系列FPGA的总的资源数为7 200,因此约占总资源的30.71%。另外固定部分还运用了3个BRAM,而总的 BRAM数为2 340,因此约占总数的0.13%。由实验结果可以看出该设计方法能够有效实现FPGA的硬件重构,而且其物理硬件设计简单。

图5 FPGA的区域分配图(截图)

4 结论

本文提出了一种基于PC机的可重构计算平台的硬件体系结构设计方法,该系统通过PCI总线的快速重新配置FPGA,同时物理硬件设计非常简单,解决了传统可重构计算平台配置时间长、灵活性受限的缺陷。

图6 固定部分资源运用图(截图)

[1]吴冬.8086微处理器寻址方式与8051控制器工作过程探讨[J].计算机光盘软件与应用,2011(19):24-25.

[2]尧征,黄乡生,黄威,等.基于FPGA的实时多任务系统的设计[J].湖南农机,2012,39(11):46-48.

[3]乐光学,郭勇,鄢卉,等.基于Region多层结构P2P计算网络定位服务策略研究[J].微电子学与计算机,2005,22(3):110-117.

[4]夏海静,温彤,李其虎.高性能图像多级小波变换的硬件设计与实现[J].电视技术,2012,36(13):19-22.

[5]谷桂华,周端,杨延飞.基于Balsa-Xilinx FPGA的异步设计流程[J].微电子学与计算机,2012,29(6):18-27.

[6] BLODGET B,JAMES-ROXBY P,KELLER E,et al.A self-reconfiguring platform proceedings[C]//Proc.The 13th International Conference on Field Programmable Logic and Applications,2003.[S.l.]:IEEE Press,2003:565-574.

[7] FONG R,HARPER S,ATHANAS P.A versatile framework for FPGA field updates:an application of partial self-reconfiguration[C]//Proc.IEEE International Workshop on Rapid Systems Prototyping,2003.[S.l.]:IEEE Press,2003:117-121.

[8]彭晓钧,李文甫.船用OSD和双绞线传输系统的模块化设计[J].电视技术,2012,36(21):139-141.

[9]肖松,李跃华,张金林.一种DPR中总线宏的设计方法[J].电子设计工程,2011,19(1):55-57.

[10]王鹏,向厚振,张志杰.基于FPGA的动态可重构边缘检测系统设计[J].电视技术,2012,36(7):32-34.