高精度硅微谐振加速度计频率测量输出电路

2014-10-21北京航天控制仪器研究所北京100039

(北京航天控制仪器研究所,北京 100039)

(北京航天控制仪器研究所,北京 100039)

硅微谐振加速度计是一种频率输出的MEMS仪表,针对其差动频率输出的特点和对静态与动态高精度测试精度的要求,设计并实现了一种高精度频率输出电路,实现了差动频率的实时相减和静态与动态频率信号输出。对电路及仪表的精度进行了测试,测试结果表明,该电路稳定性可达到1×10-9,全温范围内(-40~+70 ℃)非线性优于1×10-7,频率分辨率可达到1×10-5,测试精度满足仪表系统精度要求,使仪表更满足工程应用的条件。根据实际工程应用要求,还对该电路提出了抗干扰设计,进一步提高了该电路的工程应用可靠性。

谐振式;频率测量;频率相减;抗干扰

微加速度计作为一种重要的硅微惯性器件,具备了MEMS仪表的众多优点。由于采用频率信号输出,在传输过程中信号不易失真,并且无需经过 A/D转换就可直接与数字系统接口,极大简化了应用系统的设计,同时还具有抗干扰和高稳定性的特点。由于硅微谐振加速度计采用差动音叉布置方案[1],双路频率信号之差与外界输入加速度成比例,这一差动过程往往会降低系统的响应时间,同时大幅降低测试效率。因此针对这类高精度频率信号输出仪表,需要研究同时具有高精度静态和动态测试精度的测试方法及测试设备,并兼顾工程应用的便利性。

目前,较为通用的频率信号测试途径主要有高精度频率信号计数器、DSP或FPGA[2]实时采样处理电路和高速信号采集卡三种。第一种测试方法的静态测试精度较高,但无法在硅微谐振加速度计输入加速度成正弦变化时,准确测量正弦交变频率信号的幅值和频率;第二种测试方法对于静态和动态频率信号均有较好的测试精度,但技术实现途较复杂,电路小型化困难,电路自身发热量对硅微敏感结构的影响较大;第三种方法适合测试动态变化较快的频率信号,但限于自身时钟缺少温控装置,同时时钟频率不高增加了同步测试误差,因此静态测试精度相对较低。

为了实现谐振类仪表的工程化进程,设计并实现一款高精度、小型化并具有双路频率信号相减功能的频率输出电路就显得极为必要。

1 差动频率输出电路原理

根据文献报道,实现频率求差的功能可采用CPLD结合单片机、DSP或者FPGA来实现,电路设计相对复杂,需要包含计数器模块、微控制器模块和串行通讯电路模块,同时与频率相关的数学运算需要编程实现。这一部分电路无疑增加谐振加速度计组件的规模,大大削弱了硅微器件重量轻体积小的优势。

谐振加速度计频率变化的机理可以表示为:

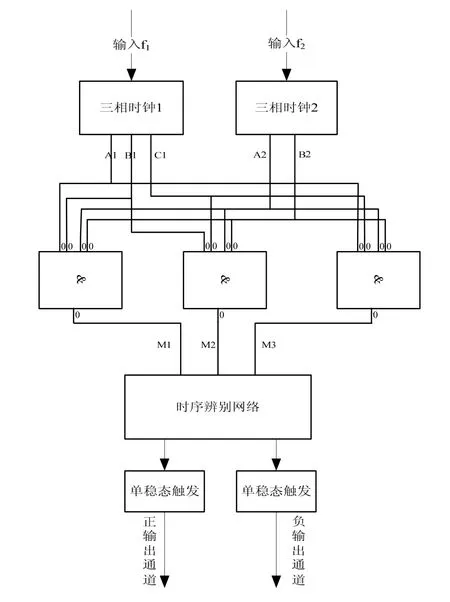

即频率是相位的微分,频率的变化等效于单位时间相位的变化。根据这一基本思想,本文提出了一种差动频率输出电路,电路由三相时钟、时序识别网络及输出级调整电路三部分构成,基本电路如图1所示。

图1 频差电路原理框图Fig.1 Schematic of differential frequency circuit

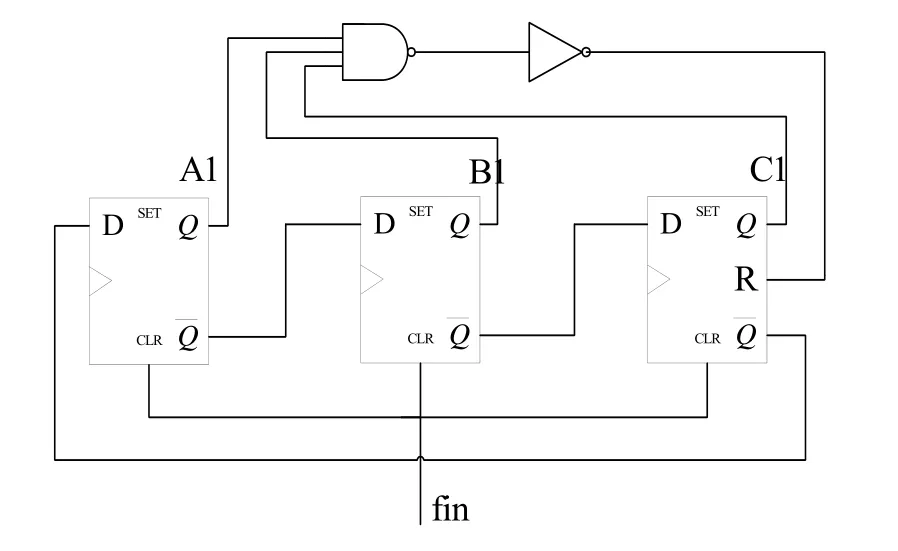

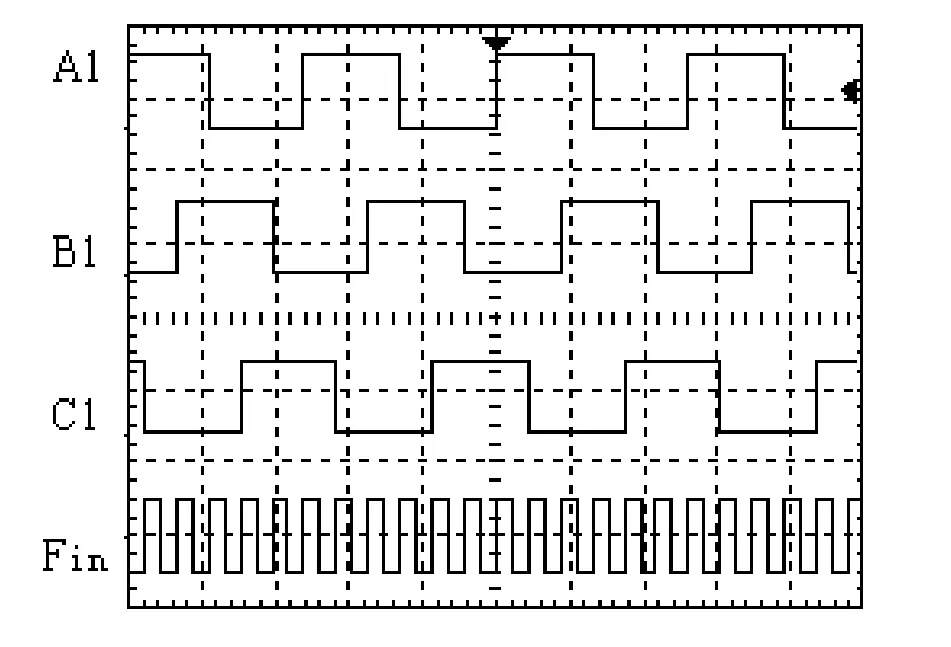

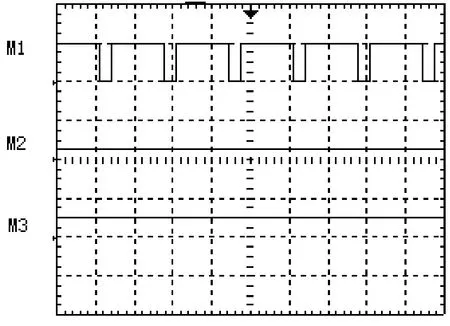

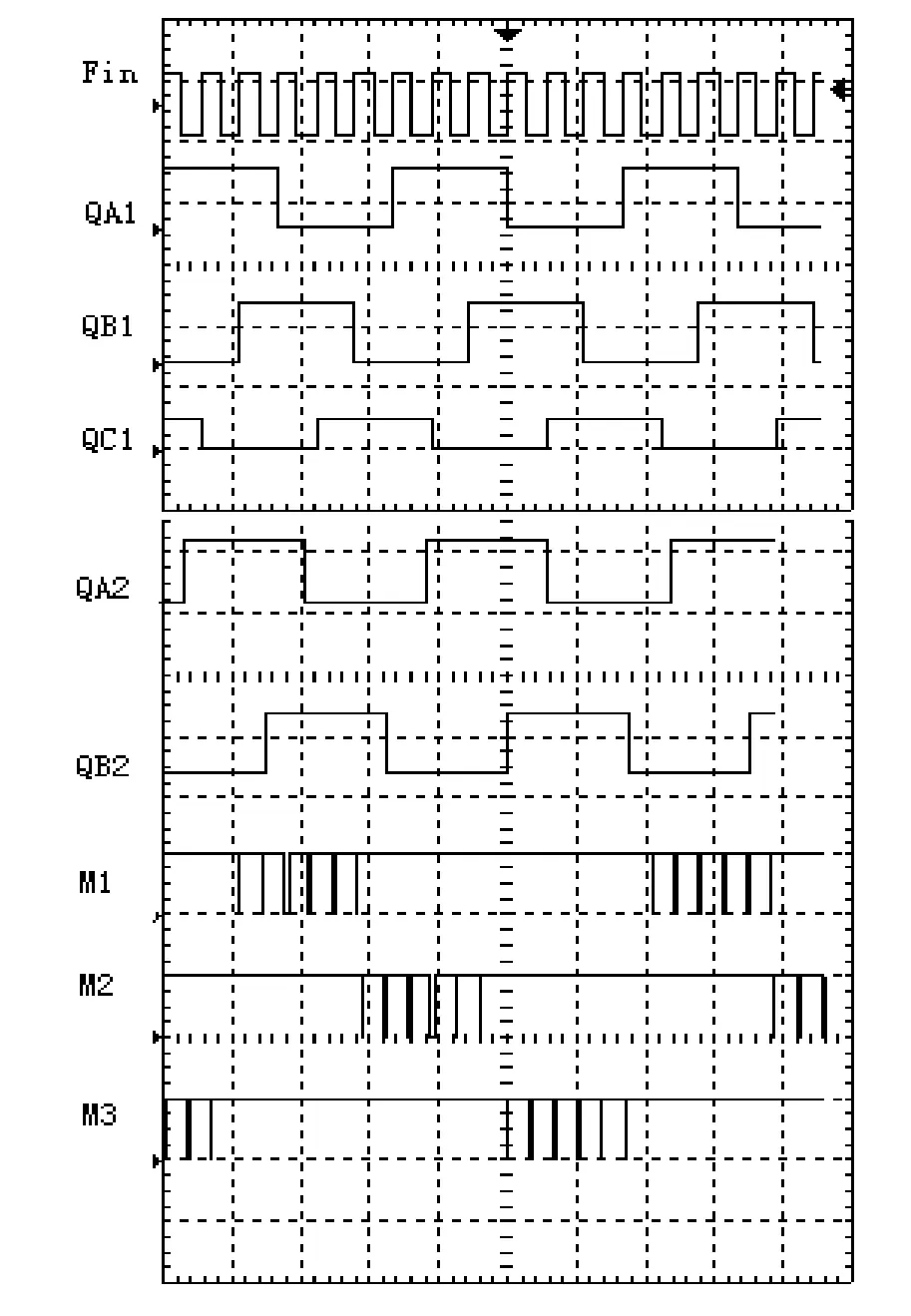

采用 D触发器级联实现三相时钟,实际上是由三相形成电路组成,其电路图如图2所示。实际上三相时钟是一个环形计数器,它把单相的fin信号分成三相方波信号,图2中三个级联的D触发器均为上升沿触发翻转,而fin被同步输入到各个D触发器的CP端。当触发器Ι翻转时,为触发器Π第二个到来的脉冲翻转创造条件,以此类推,形成了三相电路工作的波形,同时三相的相移均为120°,如图3所示。将两路输入信号分别经三相时钟分频后,以其中任意一个三相时钟输出作为时钟参考,将分频信号分别与参考信号分别进行与非运算。当两输入信号f1和f2无频差时,M1、M2、M3这三路信号中将会仅有一路输出一定频率脉冲,此脉冲的占空比由两路输入信号的初始频率决定,另两路信号置高,时序关系如图4所示。

图2 三相时钟原理图Fig.2 Schematic diagram of trinomial clock

图3 三相时钟时序图Fig.3 Scheduling of trinomial clock

图4 输入无频差时M1、M2、M3输出时序Fig.4 Output of M1, M2, and M3 when without input frequency-difference

当两路输入信号具有一定频差时,由于频率是相位的微分,两路输入信号一路为基准,另一路波形超前或者滞后。此时,M1、M2、M3三路信号将输出一定相位关系的脉冲,脉冲频率与输入信号的频差成正比。

M1、M2、M3三路信号分别携带着两路输入信号的频差关系(时序上体现为相位关系),这三路信号也是整个频差电路重要的中间信号,它们的时序关系直接决定了时序识别网络能否正确输出输入信号的频差。当两路输入信号f1和f2经过三相时钟电路,输出信号QA1、QB1、QC1、QA2、QB2、QC2按照图1送到M1、M2、M3端,得到如图5所示波形。

图5 输入有频差时时序关系图Fig.5 Sequential relationship when with input frequency-difference

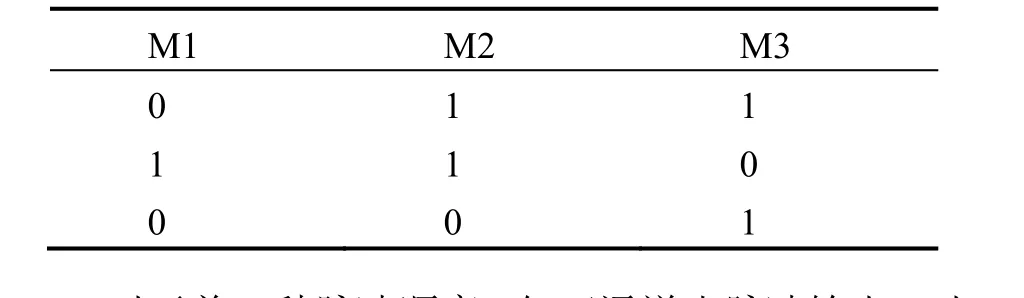

当f1>f2时,两路的时钟信号将出现相对移动,此时,M1、M2、M3出现“0”状态的次序为:M1→M2→M3→M1……,这个时序关系可用表1来表示。

同理当f1<f2时,M1、M2、M3出现“0”状态的次序为:M1→M3→M2→M1……,这个时序关系可用表2来表示。

表1 M1、M2、M3的时序关系(I)Tab.1 Sequential relationship of M1, M2, and M3 (I)

表2 M1、M2、M3的时序关系(II)Tab.2 Sequential relationship of M1, M2, and M3 (II)

对于前一种脉冲顺序,仅正通道由脉冲输出;对于后一种则仅有负通道有脉冲输出。

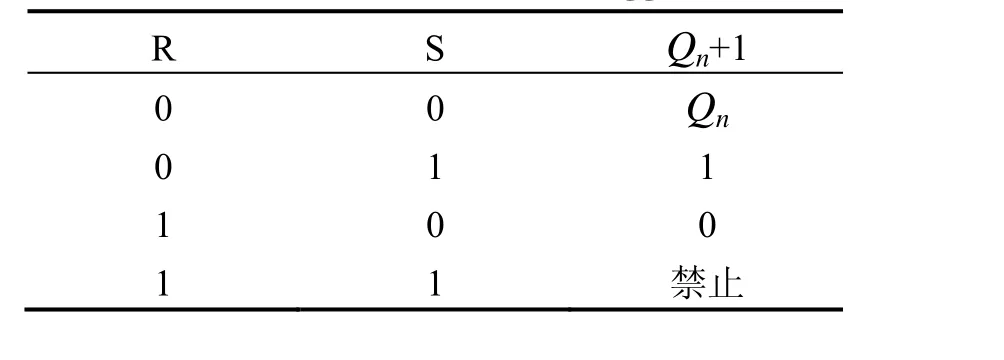

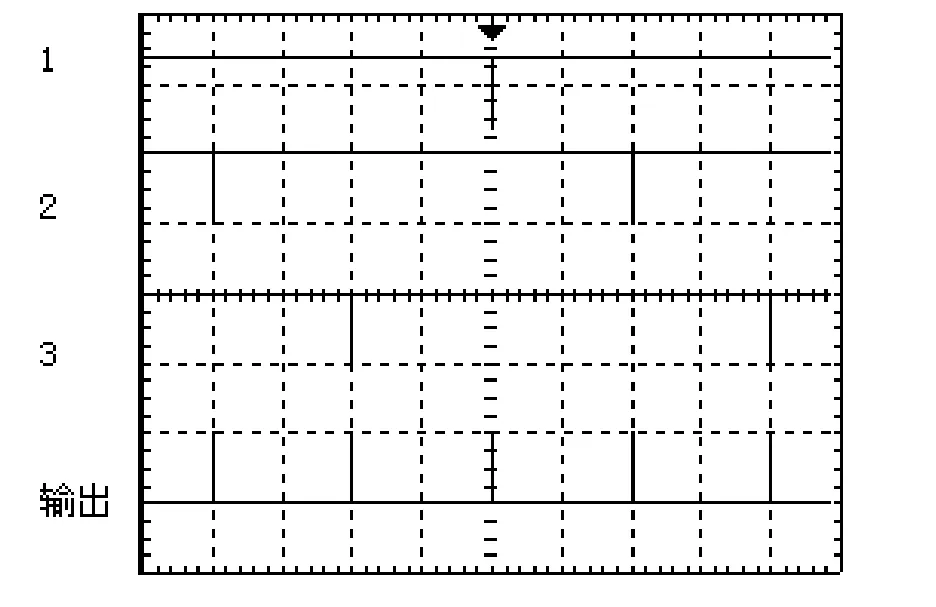

时序识别网络是该电路的主要部分,利用RS触发器的状态保持功能,根据RS触发器的特性表3可知:当R/S端无输入时,触发v器将保持上一个状态,也就是说图1中1、2、3端将根据M1、M2、M3翻转时序顺序分别保持上一个状态,且三路信号相位差恒定。当1、2、3任意一端为高时,将输出一个脉冲,该脉冲的频率就是电路输入信号的频差,如图 7所示。这样的时序关系与我们设计这款电路的基本原理依据相辅相成,两路信号的频差就是信号的相位差在单位时间的变化量,由于采用了三相时钟对输入信号进行了相位和频率的等分,也就增加了对频差信号的采样率,保证了信号的完整性。前向通路采用了三相时钟,时序识别网络采用三路RS触发器进行信号的相位的识别,如果前向通路采用4相时钟即就是4分频,则相应地采用四路RS触发器进行识别。但是分频倍数越多,分频信号相位差越小,分频精度就越高,电路就越复杂,在设计时可权衡系统需求和精度要求来进行电路设计。

图6 时序识别网络原理图Fig.6 Schematic of sequential identifying network

表3 RS触发器状态表Tab.3 States of RS trigger

图7 有频差时时序识别网络时序Fig.7 Scheduling of sequential identifying network when with frequency differences

2 差频电路抗干扰设计

在测试过程中设备通断电或较强电磁干扰产生时,将会通过地线将干扰脉冲引入至谐振加速度计电路系统中,也就是在谐振加速度输出频率信号上将会叠加某些脉冲干扰,并随有用信号一起进入差频电路部分,形成有用信号上升沿或下降沿的抖动。由于数字器件均为边缘触发,则将在输出端产生正负通道相等的脉冲输出,从而影响了电路的测量精度和稳定性。因此,需要对电路进行抗干扰能力的设计。

利用单稳态触发器外来脉冲触发下能够由稳态转到暂态,暂态维持一段时间后将自动返回到稳定状态,而暂态维持时间的长短取决于电路本身的参数这一特点,对频差电路进行抗干扰设计,改进后的原理如图8所示。

图8 采取抗干扰措施差频电路原理图Fig.8 Schematic diagram of anti-jamming design

当扰动信号频率较高时,引入到谐振加速度计输出频率信号,则这个信号的相位抖动将会很剧烈,且波动幅度较大,此时经三相时钟分频的三路信号的上升沿或下降沿就会同时产生幅度较大左右波动,根据电路的原理,当任意两路信号边缘在正常相位差以外的相位波动同时到达同电平时,将会有一个脉冲输出,而这个脉冲是我们不需要的,故通过设置单稳态触发器的保持时间。将分频后两两逻辑与非输出信号高电平持续时间缩短,使信号间边缘时间差拉大,保证信号间边缘有足够的相位差。

目前硅微谐振加速度计标度因数大概在 400 Hz/g,分辨率约为20 μg,最小分辨率下输出频差为0.008 Hz,而全量程加速度输入的频率变化约 10 kHz,频率输出电路的动态精度小于 106,这对频率输出电路的分辨率和抗干扰能力提出了较高要求。

3 差动频率输出电路性能测试

由于上述差频电路是采用数字电路原理,且选取的芯片具有较强的通用性,电路逻辑严密,经过反复调试和实验证明电路原理也很成熟可靠,因此该电路极易集成。考虑到混合集成工艺较一次集成成本低且工艺流程简单,设计、实现周期也较短,我们采用了混合集成工艺设计并生产了该电路的陶瓷封装芯片。

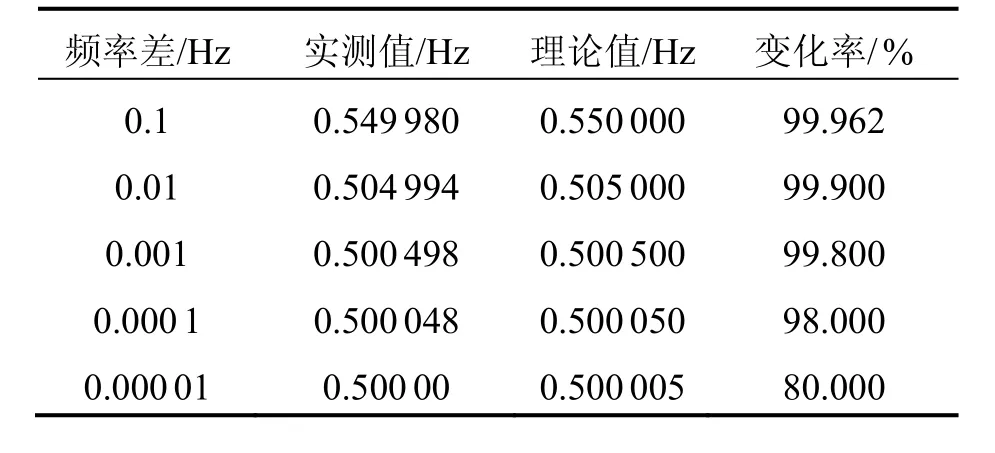

目前我们的谐振式硅微加速度计阈值可达到 25 μg,标度因数为200 Hz/g时,差频输出电路必须能够达到5×10-3的分辨率,通过测试该电路至少可以达到1×10-5的分辨率。

图9 二次集成产品外观效果Fig. 9 The appearance of integrated circuit

表4 差频输出电路分辨率测试数据Tab.4 Resolution test of differential frequency output circuit

采用信号发生器作为稳定的信号源,设定一路信号频率固定另一路频率可变,测试了该差频电路的稳定性,测试数据显示差频输出的稳定性达到 1×10-9量级。

表5 差频输出电路稳定性测试数据Tab.5 Stability test of differential frequency output circuit

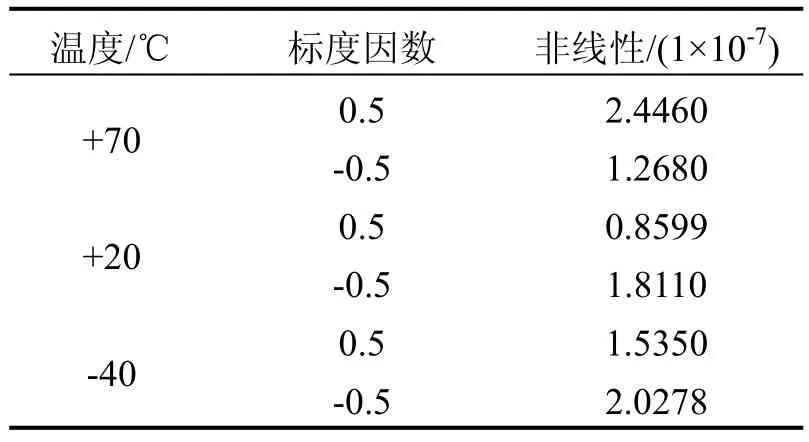

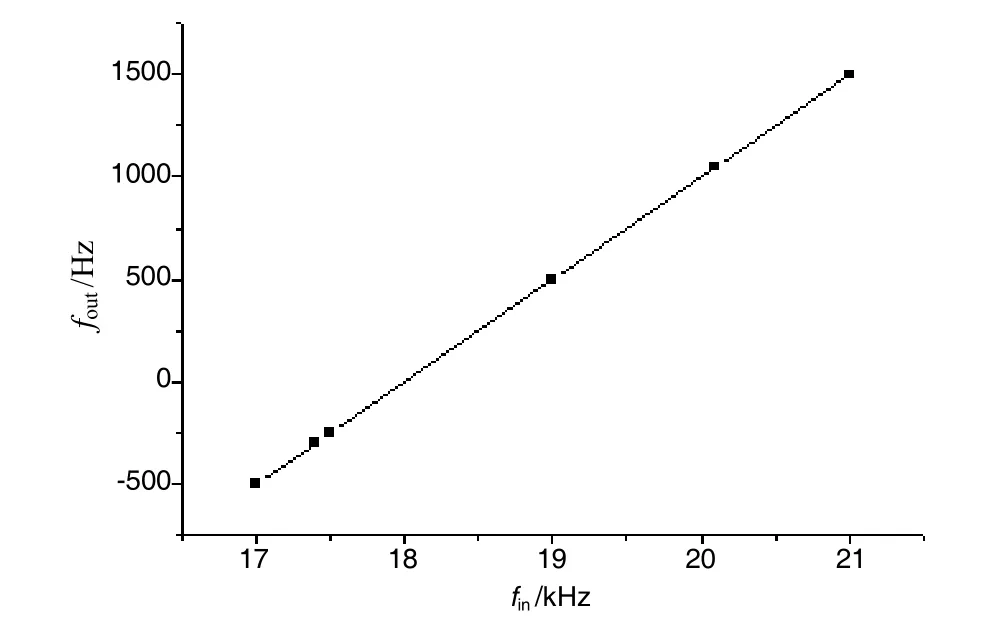

该电路作为谐振加速度计电路输出环节,它的性能会直接影响用户对仪表本身性能指标的认知,该电路的线性度决定了能否获得准确的且与输入加速度成正比的频率信号。从电路常温及高低温非线性度测试结果可知,电路非线性度达到 3.3×10-8,高低温条件下非线性度均在1×10-7以下。综合目前谐振加速度计的非线性度指标,该电路的性能指标符合谐振加速度计电路系统的要求。

表6 全温非线性测试数据Tab.6 Non-linear vs. temperature

图10 差频输出电路常温非线性Fig.10 Nonlinearity of circuit at normal temperature

4 结 论

针对谐振加速度计差动频率输出的特点,介绍了频率测量电路的设计方法及设计关键,提出了一种可实时进行双路频率差计算的电路设计思路。为了避免测试系统外加干扰对仪表测试精度的影响,文中对差频电路进行了抗干扰设计并实现。通过一系列的指标测试表明,该电路的性能满足仪表系统要求。另外,针对工程化应用要求,采用混合集成工艺设计并生产了该电路的陶瓷封装芯片,进一步为谐振加速度计满足工程化应用奠定了基础。

(References):

[1] 王巍,王岩,庄海涵,邢朝洋. 谐振式硅微加速度计闭环控制系统的分析与设计[J]. 中国惯性技术学报,2012,20(6):744-748.

WANG Wei, WANG Yan, ZHUANG Hai-han, XING Chao-yang. Analysis and design of closed-loop control system for silicon resonant accelerometer[J]. Journal of Chinese Inertial Technology, 2012, 20(6): 744-748.

[2] 朱欣华,姜智能,裘安萍,等. 硅微谐振式加速度计数据采集系统设计[J]. 中国惯性技术学报,2009,17(1):76-80.

ZHU Xin-hua, JANG Zhi-neng, QIU An-ping. Design of data acquisition system for silicon miromachined resonant accelerometer[J]. Journal of Chinese Inertial Technology, 2009, 17(1): 76-80.

[3] 石然,裘安萍,苏岩. 硅微谐振式加速度计的实现性能测试[J]. 光学紧密工程,2010,18(12):2583-2589.

SHI Ran, QIU An-ping, SU Yan. Implementation and experiment of micromechinal differential silicon resonant accelerometer[J]. Optics and Precision Energinnering, 2010, 18(12): 2583-2589.

[4] 王巍,王岩,庄海涵,邢朝洋. 硅微谐振加速度计交流检测信号解耦技术[J]. 中国惯性技术学报,2012,20(4):468-471.

WANG Wei, WANG Yan, ZHUANG Hai-han, XING Chao-yang. AC detection signal decoupling for silicon resonant accelerometer[J]. Journal of Chinese Inertial Technology, 2012, 20(4): 468-471.

[5] 毕小伟,廖波勇,严小军. 一种石英振梁加速度计驱动仿真的设计[J]. 导航与控制,2011,10(4):38-42.

BI Xiao-wei, LIAO Bo-yong, YAN Xiao-jun. Drive circuit simulation of quartz vibrating beam accelerometer [J]. Navigation and Control, 2011, 10(4): 38-42.

[6] Hopins R, Miola J, Sawyer W. The silicon oscillating accelerometer: A high-performance MEMS accelerometer for precision navigation and strategic guidance application[R]. The Charles Stark Draper Laboratory, Inc., 2005: 970-979.

[7] Qiu Anping, Su Yan, Zhu Xinhua, et al. Bulk micromachined silicon resonant accelerometer[C]// International Conference on Information and Automation. 2009: 1289-1292.

[8] Pinto D, Mercier D, Kharrat C, et al. A small and highsensitivity resonant accelerometer[C]//Proceedings of the Eurosensors XXⅢ Conference. 2009: 536-539.

[9] Tocchio A, Caspani A, Langfelder G, et al. Resolution and start-up dynamics of MEMS resonant accelerometers [C]//2011 IEEE Sensors Conference. 2011: 161-164.

[10] Vigevani G, Goericke F T, Pisano A P. Microleverage DETF aluminum nitride resonating accelerometer[C]// 2012 IEEE International Frequency Control Symposium. 2012: 754-757.

[11] Comi C, Corigliano A, Langfelder G, et al. A resonant microaccelerometer with high sensitivity operating in an oscillating circuit[J]. Journal of Microelectromechanical Systems, 2010, 19(5): 1140-1152.

高精度硅微谐振加速度计频率测量输出电路

张 玲,王 岩,邢朝洋

High-precision frequency output circuit for silicon micromechanical resonant accelerometer

ZHANG Ling, WANG Yan, XING Chao-yang

(Beijing Aerospace Control Device Institute, Beijing 100039, China)

The silicon micromechanical resonant accelerometer is an MEMS instrument with frequency output. In view of the differential frequency’s output characteristics and in order to satisfy the requirement of static and dynamic high-accuracy test, a high-accuracy frequency exportation circuit was designed, which realized the real-time subtraction of differential frequency and the output of static or dynamic frequency signal. The accuracy test of the circuit and the gauge shows that the circuit stability can reach 1×10-9, the non-linearity is better than 1×10-7in full temperature range of -40~+70 ℃, and the resolution can reach ≥1×10-5. The test accuracy satisfies the accuracy requirements of the gauge system, thus the engineering application condition be more easily satisfied. In addition, according to the requirements of engineering application, an anti-jamming design was put forward, which further improve the reliability.

resonant; frequency measurement; frequency subtraction; anti-jamming

1005-6734(2014)06-0820-05

10.13695/j.cnki.12-1222/o3.2014.06.022

文献标志码:

2014-07-17;

2014-11-07

国防基础科研项目支持(A0320110013)

张玲(1981—),女,工程师,研究方向为MEMS仪表。E-mail:lingzhang_2000@sina.com