基于FPGA的超声数据采集装置的设计与实现*

2014-09-28杜彬彬任勇峰

张 鹏,杜彬彬,任勇峰

(中北大学仪器科学与动态测试教育部重点实验室;电子测试技术国家重点实验室,太原030051)

基于FPGA的超声数据采集装置的设计与实现*

张 鹏,杜彬彬,任勇峰*

(中北大学仪器科学与动态测试教育部重点实验室;电子测试技术国家重点实验室,太原030051)

为了实现对某航天器在地面及飞行过程中的超声数据进行高精度、高速采集的功能,根据测量系统的技术要求,设计数据采集装置的硬件电路和时序控制逻辑。为了满足恶劣的环境测试要求,设计采用高速、高精度、宽温度范围的THS1408模数转换器。选取高速运放AD8028进行信号调理,以FPGA作为逻辑控制器,控制THS1408进行模数转换。经测试,采集精度优于0.5%,满足实际工程需要,具有很高的可靠性,已成功应用于该测量系统。

FPGA;数据采集;THS1408;信号调理

随着数字化技术不断深入的今天,数据采集技术已经成为信号处理过程中的重要环节。数据采集技术已经广泛应用于雷达、声纳、瞬态信号测试、无线探伤、航空、航天等诸多领域[1-2]。随着数据采集技术应用的不断加深,不仅对数据采集装置的采集精度、采集速度和数据量有了更高的要求,还要求数据采集装置能够在恶劣环境条件下可靠的工作[3]。而模数转换芯片性能的优劣对数据采集会产生最直接的影响,因此,本设计在实际应用的背景下,根据测量系统的技术要求,通过合理的选取高速、高精度、宽温度范围的THS1408模数转换器,优化数据采集装置的电路设计和时序设计,以实现超声数据采集装置的功能。

1 整体设计方案

超声数据采集装置的整体设计框图如图1所示。输入的超声信号是经过传感器转换过的电压模拟信号(0~5 V),电压信号经过传感器信号输入接口进入信号调理电路,调理后的输入信号经过THS1408前的单端转差分电路后转换为差分信号,THS1408在FPGA芯片的逻辑控制下,将差分信号进行模数转换,模数转换后的数字量经过内部程序进行数据处理后缓存入外部FIFO中,再将FIFO中的有效数据编帧、存储在16 Gflash存储阵列中。超声数据采集装置通过总线接口进行板间通信:接收上位机指令,上传数据和装置状态。

图1 超声数据采集装置的整体设计框图

2 THS1408功能简介

测量系统要求超声数据采集装置的单通道采样率为5 Msample/s,分辨率为12位,采样精度小于0.5%,保留8位有效数据位,采集装置的工作温度范围为-50℃ ~125℃,模数转换芯片功耗小于500 mW。为了满足超声数据采集装置的技术指标,设计选用了德州仪器的 THS1408模数转换器,THS1408具有以下功能特点:

(1)采样速率高:3 Msample/s~8 Msample/s采样率;

(2)工作温度范围宽:-55℃~125℃;

(3)功耗低:典型功耗为270 mW,最大功耗为360 mW;

(4)14位分辨率;

(5)差分输入接口;

(6)可编程输入增益;

(7)单电源供电;

(8)片内集成高性能的采样保持放大器和参考电压源。

THS1408在宽温带、强振动的环境下,能够满足测量系统的技术要求,且具有很好的性价比和功耗/速度比[4]。

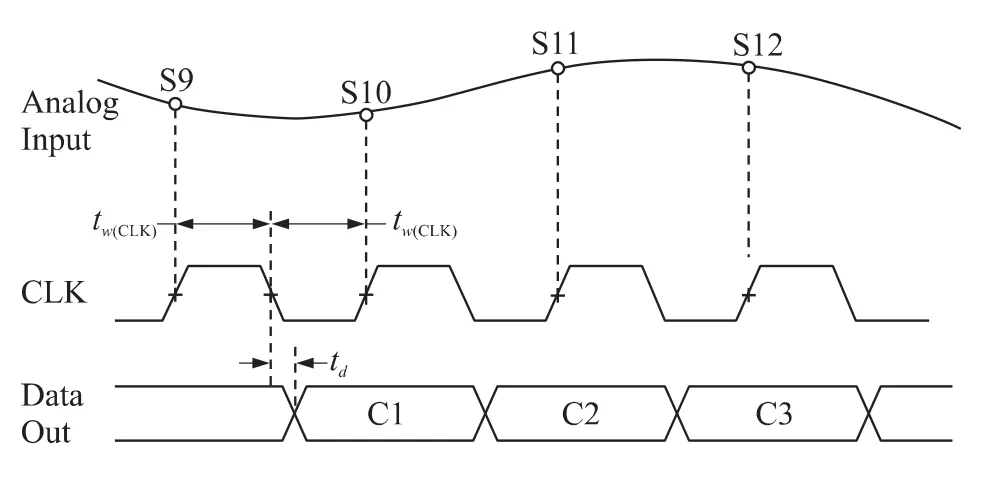

THS1408的采样内核采用的是一个延时9.5个采样周期的循环采样结构,信号开始采样后的9.5个时钟周期后,转换结果开始输出,THS1408采用具有三态缓冲的并行数据接口,可以直接连接到数据总线接口,通过驱动OE为低可以将数据输出使能,使得电路设计更加简单。采样时序如图2所示。时钟频率为5 MHz,时钟上升沿采样,下降沿输出数字量,数据输出延时td=25 ns。

图2 THS1408采样时序图

3 超声采集电路设计与分析

超声采集电路主要由两部分组成:信号调理电路、单端转差分电路和模数转换电路。电路原理图如图3所示,信号调理电路的功能是对输入信号进行运放跟随调理以及接口保护,R13为接口保护电阻,单端转差分电路将输入信号转为差分信号,满足THS1408转换的输入信号要求,模数转换电路为: FPGA芯片控制THS1408完成模数转换部分[5]。

输入的超声信号是经过传感器转换成电压量的模拟信号(0~5 V),输入信号频率不大于1.5 MHz,设计拟采用-3 dB带宽为16 MHz的AD823进行运放跟随,在电路调试的过程中,当信号频率达到500 kHz时,经过AD823运放跟随后信号出现明显失真现象,运放跟随前后波形如图4所示(通道1为跟随前波形)。为了解决高频信号经过运放跟随后波形失真的现象,设计采用低失真率、-3 dB带宽为190 MHz的AD8028替换AD823,经过AD8028进行运放前后的测试波形如图5所示(通道1为跟随前波形)。电路采用AD8028以后,当信号频率达到最大要求(1.5 MHz)时,运放跟随后的波形效果仍然很好,失真几乎可以忽略不计,大大提高了信号采样的精度[6-7]。

图3 超声采集电路原理图

由于THS1408的模拟信号输入接口采用差分形式,而输入信号为单端模拟信号,所以需要对输入信号进行单端转差分处理。THS1408芯片资料推荐了两种单端转差分的电路:变压器耦合和单端配置方式单端转差分电路。变压器耦合单端转差分电路虽然精度较高,抗干扰能力较好,但是电路比较复杂,而且功耗较高;单端配置方式单端转差分电路简单,容易实现,功耗较低,能够满足采样精度要求,综合考虑,设计采用单端配置方式的单端转差分电路,电路设计如图3中运放跟随和THS1408之间的电路。

图4 AD823运放跟随前后波形

图5 AD8028运放跟随前后波形

芯片资料推荐电路中R12为10 K,在实际电路调试过程中,AD运放的容性负载随着输入信号频率的增大不断减小,当输入信号频率达到1 MHz以上时,根据AD8028的输入电容值C=和容性负载计算公式:

可知,AD8028的容性输入阻抗与R12在同一数量级,R12将会对输入信号进行分压,使得输入信号的幅值有所衰减,影响了信号的采集的精度,通过对电路设计的调整,将R12的阻值调整为1 K时,信号幅值的衰减很小,能够满足信号采集的精度。对于THS1408电路的设计和分析:已知THS1408的内部参考电压VREF+=2.5 V,VREF-=0.5 V,根据电路可以计算出:差分争端输入VIN+=1.5 V,运放U1A的正端基准电压为1 V,输入信号与VIN-、ΔVIN之间的关系如表1所示。

表1 输入信号与V IN-、ΔVIN对应关系表

系统要求采集的有效数据位为8位,根据THS1408芯片资料可知:ΔVIN的范围为-2 V~2 V,对应的AD14位编码为0~16 383,编码方式设置为线性二进制。为了实现有效编码的全范围覆盖,即输入电压范围为0~5 V时,采集的有效对应编码为0~255,设计ΔVIN最值差为0.5 V,对应的AD14位编码差值为2 048,通过FPGA内部程序将模数转换的高11位编码进行转换处理:如果高11位编码大于“10111001100”,则有效对应编码值为255;如果高11位编码小于“10011001100”,则有效对应编码值为0;其他情况下,高 11位编码减去零位值(10011001100)后,取低8位数据为采集的有效对应编码。经过内部程序处理后,输入电压范围为0~5 V时,采集的有效对应编码为0~255,最后对采集的有效数据进行编帧、打包和储存。

4 时序逻辑设计

设计采用Xilinx公司的FPGA芯片作为时序逻辑控制器[8-9],根据THS1408的采样时序和采样率确定AD采集时序如图6所示。系统时钟CLK频率为60 MHz,AD采样时钟ad_clk为6 MHz,系统上电后,FPGA按照THS1408的写时序对THS1408的增益寄存器、偏移寄存器、控制寄存器进行初始化配置,增益设置为1,偏移校正值设置为0,THS1408工作模式设置为:普通工作模式、内部参考电压、线性二进制编码方式。当上位机下发超声数据采集命令时,采集装置进入数据采集状态,通过对系统时钟进行计数分频产生AD采样时钟ad_clk,对输入信号进行采样和数据转换,再通过控制数据输出使能out_oe输出转换的14位数字量,数字量经过内部数据处理缓存入外部FIFO中,再将FIFO中的有效数据编帧存储在16 G Flash存储阵列中[10]。当上位机下发读取超声数据命令时,超声数据采集装置将Flash中的有效数据通过总线接口上传到上位机进行数据处理。

图6 AD采集时序

5 功能验证

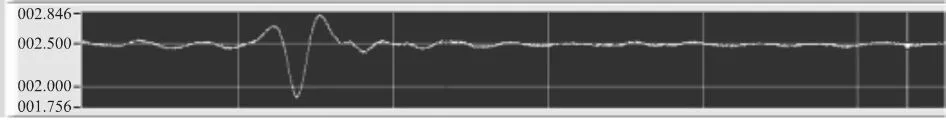

将超声数据采集装置接入测试系统,对超声数据采集装置进行功能测试。在模拟的工作环境下,通过地面测试台为采集装置提供3 V直流量,上位机软件将超声数据采集装置采回的数据进行数据处理和分析,数据的帧校验准确无误,对分解后的数据进行绘图,如图7所示(图中纵坐标表示电压量,单位为V),计算得出采样精度为0.32%。将装置与传感器联试,测得超声传感器随机敏感波形如图8所示。

图7 采样精度测试

图8 超声信号随机敏感测试

经过功能验证,超声数据采集装置满足实际工程的要求,能够可靠的对超声数据进行采集。本设计只介绍了单通道的超声数据采集,在单通道的基础上,增加多路采集电路设计和调整AD的采集时序可以实现多通道数据采集,这里就不做介绍了。

[1]郑永秋,史赟,李圣昆,等.多通道高精度数据采集电路的设计与实践[J].电测与仪表,2011(9):86-90.

[2]薛瑶.某飞行器数据记录器的优化设计[D].太原:中北大学,2009.

[3]李圣昆.高速数据采集记录装置研究[D].太原:中北大学,2006.

[4]TI.THS1408-EPData sheet[EB/OL].www.ti.com,2011.

[5]郭建平,王亮,郭正刚,等.单通道信号处理的前端信号调理模块的设计[J].仪表技术与传感器,2008(9):99-101.

[6]杜文志,谭维炽.中国航天专用集成电路实现途径研究[J].中国空间科学技术,2002,22:31-37.

[7]赛尔吉欧·弗朗哥.基于运算放大器和模拟集成电路的电路设计[M].西安:西安交通大学出版社,2004.

[8]任勇峰.VHDL与硬件实现速成[M].北京:国防工业出版社,2005.

[9]王杰,王诚,谢龙汉.Xilinx FPGA/CPLD设计手册[M].北京:人民邮电出版社,2011.

[10]沈伟,王军政,汪首坤.基于FIFO的高速高精度数据采集技术研究[J].电子器件,2007,30:1673-1676.

Design and Implement Of Ultrasound Data Acquisition Device Based on FPGA*

ZHANG Peng,DU Binbin,REN Yongfeng*

(TheMinistry of Education Key Laboratory for Instrument Scienceand Dynamic Test;National key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

In order to achieve high-precision,high-speed acquisition ultrasound data of a spacecraft in the ground and during the flight,according to the technical requirements of the measurement system,hardware circuit of data acquisition device and its timing control logic are designed.In order tomeet the harsh environmental testing requirements,the design uses a high-speed,high-precision,wide temperature range THS1408 analog-to-digital converter. Selecting high speed Op AMP AD8028 for signal conditioning and making FPGA as logic controller,THS1408 is used to control analogue to digital conversion.From testing,acquisition accuracy is better than 0.5%to meet the needs of practical engineering,with high reliability,has been successfully applied to themeasurement system.

FPGA;data acquisition;THS1408;signal conditioning

10.3969/j.issn.1005-9490.2014.01.020

TP274.2 文献标识码:A 文章编号:1005-9490(2014)01-0081-04

项目来源:太原华纳方盛科技有限公司项目

2013-05-18修改日期:2013-06-14

EEACC:7210G

张 鹏(1988-),男,汉族,黑龙江省林口县人,现为中北大学在读硕士研究生,主要研究方向为测试计量技术与仪器研究,251105939@qq.com;

任勇峰(1968-),男,汉族,山西中阳人,教授,中北大学硕士生导师,主要研究方向为微电路系统、电路系统检测与诊断技术,renyongfeng@nuc.edu.cn。