Kinetis系列MCU时钟系统结构与配置研究*

2014-09-06蒋建武王宜怀

蒋建武,王宜怀

(苏州大学计算机科学与技术学院,江苏 苏州 215006;泰州职业技术学院信息工程学院,江苏 泰州 225300)

Kinetis系列MCU时钟系统结构与配置研究*

蒋建武1,2,王宜怀1*

(苏州大学计算机科学与技术学院,江苏 苏州 215006;泰州职业技术学院信息工程学院,江苏 泰州 225300)

内嵌ARM®CortexTM-M核的Kinetis系列微控制器具有复杂的时钟系统,时钟系统中多功能时钟发生器、锁相环、锁频环、晶振系统等功能模块协调工作时能为应用系统提供稳定的时钟源。通过对K60时钟系统的结构和配置方法的剖析,以及对多功能时钟发生器运行机制的梳理,提出了时钟源性能的测试方法以及芯片系统各功能模块时钟源的选择方法,为Kinetis相关芯片应用设计过程中的时钟系统配置以及时钟源选择提供了借鉴与参考。

微控制器;时钟系统;运行机制;多功能时钟发生器

自2010年Freescale公司推出了基于ARM®CortexTM-M4内核的Kinetis K系列芯片[1]后又推出多款ARM核的32位MCU,2014年又将推出ARM®CortexTM-M4内核与RF收发器相结合应用于无线传感网的W系列芯片。芯片的功能越强大对其时钟系统的要求也越高,合理而高效地配置时钟系统可极大提升嵌入式系统的实时性与稳定性,并在低功耗模式下有效地降低系统功耗。Kinetis系列芯片的时钟系统具有内外参考时钟接受宽泛的频率输入[1-2],内置多功能的时钟发生器提供多种的时钟源备选,强大的门控功能启停各功能模块时钟。复杂而有效的时钟系统为实现低功耗、高性能、多功能等优异特性提供保证,但其复杂的结构和缜密的配置过程使得掌握并灵活应用时钟系统为应用系统的开发提供稳定而高效的时钟具有一定的难度。针对Kinetis系列芯片课题组做了深入的研究,在《嵌入式系统原理与实践-ARM Cortex-M4 Kinetis微控制器》一书中对MK60DN512ZVMD10(以下简称K60)时钟系统做了阐述[3],很多读者在应用过程中仍然对时钟系统的结构与配置有很多困惑;在《FreescalKinetis L系列MCU的时钟运行机制分析与编程方法》一文中同课题组的朱仕浪分析了MKL25Z128VLK4(以下简称KL25)时钟系统的配置与使用[4]。以下将以K60为例剖析Kinetis系列MCU时钟系统的结构及其运行机制,给出内外参考时钟选择依据与其配置方法,分析MCG模块各运行模式的特性和模式状态迁移过程,最后提出各时钟源性能分析方法并归纳系统模块对时钟源的选择配置方法。

1 K60时钟系统

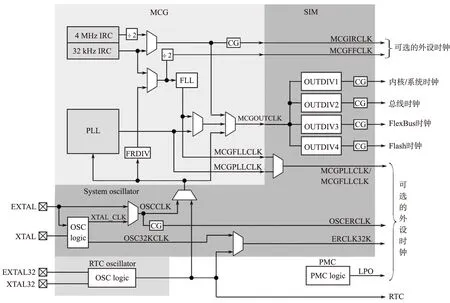

1.1 内部与外部参考时钟

K60芯片的时钟系统包含2路内部参考时钟和2路外部参考时钟。内部参考时钟分为高频4 MHz和低频32 kHz,可作为MCU的时钟源或可选外设时钟MCGIRCLK。1路外部参考时钟通过系统振荡器利用外部引脚XTAL与EXTAL接入时钟系统,支持低频32 kHz或高频3 MHz~8 MHz和8 MHz~32 MHz,其可作为MCU的时钟源或可选外设时钟OSCERCLK和ERCLK32K[5]。另一路外部参考时钟通过实时时钟专用振荡器RTC OSC(Real Time Clock Oscillator)利用外部引脚XTAL32与EXTAL32接入时钟系统,该路通常接入32.768 kHz晶振,为RTC模块提供稳定的RTC时钟源并为其他外设模块提供ERCLK32K时钟源。

图1 K60时钟系统

1.2 多功能时钟发生器

时钟系统的内部参考时钟和外部参考时钟均接入多功能时钟发生器MCG(Multipurpose Clock Generator),通过MCG模块通过内部包含的一个锁频环FLL(Frequency-Locked Loop)和一个锁相环PLL(Phase-Locked Loop)实现对相应参考时钟倍频,前者可接收内外参考时钟作为时钟源,后者仅能使用外部参考时钟。时钟系统可选择PLL输出(MCGPLLCLK),FLL输出(MCGFLLCLK),外部参考时钟和内部参考时钟4个时钟源之一作为当前时钟输出MCGOUTCLK[6]。

1.3 电源管理器

电源管理器PMC(Power Management Controller)作为独立的模块可产生1 kHz的信号作为系统外设时钟LPO。

1.4 系统集成模块

以上所产生的多个时钟信号通过系统集成模块SIM(System Integration Module)分配到各个指定的系统功能模块上,例如:WatchDog、USB、Ethernet、SHDC、I2S等[7],时钟产生电路CG(Clock Generator)也实现了模块专用的时钟门控逻辑,允许通过停止供应时钟信号关闭模块的功能。同时CG模块还提供了4个时钟分频器(OUTDIV1~OUTDIV4),通过不同分频使得在同一个MCGOUTCLK时钟源驱动的情况下4个系统模块时钟,即内核/系统时钟、总线时钟、FlexBus时钟和Flash存储器时钟可运行在不同的频率上由此实现各模块以较低的频率工作以便降低功耗[8]。

2 时钟系统配置

2.1 内部与外部参考时钟选择

MCG_C1[CLKS]用于选择内部与外部参考时钟源,CLKS=01选择内部参考时钟,CLKS=10选择外部参考时钟;MCG_C2[IRCS]用于选择内部快慢参考时钟,IRCS=0,选择慢内部参考时钟32 kHz晶振,IRCS=1,选择快内部参考时钟4M晶振;SIM_SOPT2[MCGCLKSEL]用于选择外部参考时钟,MCGCLKSEL=0选择系统振荡器OSC,MCGCLKSEL=1选择实时时钟振荡器RTC OSC。

2.2 锁相环与锁频环选择

MCG_C6[PLLS]用于选择锁相环FLL和锁频环PLL,PLLS=0,选择FLL,PLLS=1,选择PLL。MCG_C1[FRDIV]为FLL外部参考时钟分频因子,与MCG_C2[RANGE]共同决定取值范围从1至1 024;MCG_C5[PRDIV]为PLL外部参考时钟分频因子,取值范围从1至25;MCG_C6[VDIV]为PLL压控晶振(VCO)倍频因子,取值范围从24至55。

3 MCG运行机制分析

3.1 MCG时钟运行模式

时钟运行模式根据MCG的锁频环(FLL)或锁相环(PLL)工作情况,选用的参考时钟以及输出的时钟是否供给MCGOUTCLK进行定义和分类[9]。例如,PLL工作时,选用外部参考时钟,并将锁频输出时钟MCGPLLCLK提供给MCGOUTCLK,此时MCG时钟模式称为PEE(PLL外部忙碌);若PLL输出的时钟不提供给MCGOUTCLK,而是由外部参考OSCCLK时钟送到MCGOUTCLK,此时MCG时钟模式称为PBE(PLL外部旁路),其它时钟模式的含义以此类推。MCG共有9种时钟运行模式:FEI、FEE、FBI、FBE、PBE、PEE、PEE、BLPI、BLPE和STOP,模式切换需要遵守图2所示的MCG转换规则,图中任一状态可转换到停止态(STOP),图示箭头表明允许的MCG模式转换方向。9种时钟运行模式可分为4种工作状态,即初始态:复位后初始状态,中间态:MCGOUTCLK时钟源不是由FLL/PLL输出提供,而是由相应参考时钟提供,工作态:MCGOUTCLK时钟源正常工作时由FLL/PLL输出,低功耗时由内外参考时钟提供,停止态:MCG停止工作,表1给出了各种模式与工作状态的关系[10]。

表1 时钟运行模式与工作状态关系

表2 时钟配置推荐值

3.2 MCG运行状态切换编程方法

由图2 MCG模式状态图可知系统复位后首先进入默认FEI运行模式,该模式使用内部32 kHz慢参考时钟,640倍倍频后可得20.97 MHz时钟信号,可满足系统基本运行的需求。当需要更高的频率(例如配置为100 M网卡,系统时钟至少50 MHz,K60数据手册5.3.1节[2]),必须使用FLL或PLL倍频。与FLL相比,PLL具有防噪声、防抖动的功能,具有更高的精度;所以系统启动后一般配置切换到PEE(PLL外部忙碌)模式。以下将以表2中给出的常用推荐时钟配置为例介绍MCG时钟模式FEI->FBE->PBE->PEE的状态切换过程[11]。

图2 MCG模式状态图

对K60芯片MCG进行状态切换时需要满足以下基本条件[1]:

(1)Core/system bus≤100 MHz;(2)bus clock≤50 MHz,且必须是Core/systembus的整数分频;(3)Flash bus≤25 MHz,且必须是bus clock的整数分频;(4)FlexBus≤bus clock。

对时钟源的配置按照以下步骤完成:

(1)将外部时钟分频为2 MHz~4 MHz之间的一个频率,输入给PLL,该分频因子由MCG_C5寄存器的PRDIV决定。(2)PLL内部的压控振荡器VCO(Voltage-Controlled Oscillator)将输入的时钟倍频,倍频后即得到MCGOUTCLK[12]。(3)通过SIM模块的SIM_CLKDIV1寄存器,将MCGOUTCLK时钟分频成不同的时钟域,供内核、系统、总线、FlexBux和Flash使用。

图3给出了一个PLL初始化FEI->FBE->PBE->PEE状态切换的执行实例。关于MCG模式状态切换路径的选择是一个比较复杂的过程,对此研究将另文分析,在此不再赘述。

图3 PLL初始化执行流程

4 时钟源性能分析

4.1 时钟源频率测量方法

外部参考时钟可直接测量外部接入引脚XTAL和XTAL32;在K60芯片中PTA6可以配置为TRACE_CLKOUT功能用于输出当前时钟MCGOUTCLK和内核时钟Core/System CLK;FlexBus时钟可通过将PTC3配置为FB_CLKOUT输出;RTC实时时钟RTCCLK可将PTE26配置为RTC_CLKOUT输出。在Kinetis L系列MCU芯片中PTC3可配置为CLKOUT功能,用于输出总线时钟Bus Clock、LPO、内部参考时钟MCGIRCLK、外部参考时钟OSCERCLK;RTC_CLKOUT输出功能通过配置PTE0实现[13]。

4.2 实验数据分析

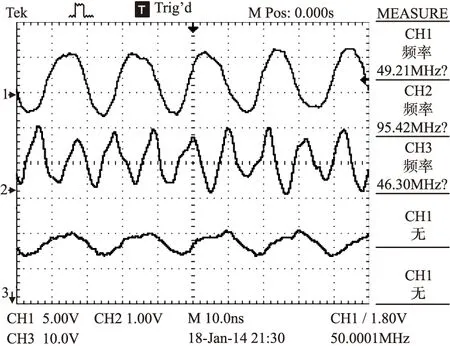

实验数据在苏州大学飞思卡尔嵌入式中心SD-FSL-K60-C评估板上完成,利用TEK TDS2024B示波器测量。实验中通道1(CH1)测量外部参考输入ETAL,通道2利用SIM_SOPT2[TRACECLKSEL]将TRACE_CLKOUT分别配置成MCGOUTCLK和Core/System CLK,通道3测量系统FlexBus信号FB_CLK;图4中外部参考时钟50 MHz,MCGOUTCLK以PLL为时钟源,配置为96 MHz,MCGOUTCLK∶Core/SystemCLK∶BusCLK∶FlexBus∶FlashBus=4∶2∶2∶2∶1;图5中外部参考时钟50MHz,MCGOUTCLK以PLL为时钟源,配置为192.3MHz,MCGOUTCLK∶Core/SystemCLK∶BusCLK∶FlexBus∶FlashBus=4∶2∶2∶2∶1。

图4 时钟源测试数据1

图5 时钟源测试数据2

5 系统功能模块时钟源选择分析

K60时钟系统为系统功能模块和外设模块提供了10多个内部时钟源供各功能模块使用,各时钟源具体含义可参见表3。

各模块根据系统设计的要求可通过表4所示的配置寄存器设置各自的时钟源。除了以上通用的时钟源,为了满足一些特殊模块(Ethernet、USB、SDHC和I2S)的时钟要求,还为其各自设置了一个独立的时钟源接口,可直接外接信号供相应模块使用,各时钟源的配置方法详见表3[10]。串行通信模块UART0和UART1使用Core/system clock时钟源,其他串口模块使用Bus clock时钟源[14]。

表3 K60内部时钟源

6 总结语

Kinetis系列MCU的时钟系统可以通过内外参考时钟将频率信号源接入芯片,由多功能时钟发生器MCG为各功能模块提供多个时钟源,利用门控模块启停系统功能模块时钟和时钟分配机制为各功能模块在满足要求的前提下选择较低的工作频率,用以保证其能稳定工作且功耗降低。关于MCG运行模式迁移选择以及时钟的有效性与电源模式(即低功耗模式)的关系等问题将在后继的工作中进一步分析研究。

[1]Freescale. K60 Sub-Family Reference Manual Rev.6,2011[EB/OL]. http://www.Freescale.com.

[2]Freescale. K60 Sub-Family Data Sheet Rev.6,2011[EB/OL]. http://www.Freescale.com.

[3]王宜怀,吴瑾,蒋银珍. 嵌入式系统原理与实践-ARM Cortex-M4 Kinetis微控制器[M]. 北京:电子工业出版社,2012:3.

[4]Freescale. KL25 Sub-Family Reference Manual Rev.3,September 2012[EB/OL]. http://www.Freescale.com.

[5]徐毅,陈书明. 一种低功耗的混合谐振时钟分布机制[J]. 微电子学与计算机,2010,10:87-90,95.

[6]张艳,韩雁,霍明旭,等. 基于EPA协议的精确时钟同步方法[J]. 传感技术学报,2009,22(7):978-982.

[7]蒋善锋,王丽芳,蒋泽军. Windows时钟机制的实时扩展研究[J]. 微电子学与计算机,2013(8):116-119,123.

[8]许剑新,冯冬芹. 基于本地时钟自校正的无线传感器网络同步方法[J]. 传感技术学报,2008,21(8):1448-1452.

[9]苗汇静,孙桂华,王立新. 通用有源滤波器设计[J]. 电子器件,2012,25(5):549-553.

[10]张海龙,马铁华,谢锐,等. 基于MCU和CPLD的微型动态应力存储测试系统[J]. 电子器件,2014,37(1):123-126.

[11]陈大峰,白瑞林,邹骏宇. 嵌入式设备的精确时钟同步技术的研究与实现[J]. 计算机工程与应用,2013(4):82-86.

[12]朱小冬,王世明. 多时钟域处理器构架的性能和功耗分析[J]. 计算机工程,2005,31(24):75-77.

[13]Freescale. KL25 Sub-Family Data Sheet Rev.3,September 2012[EB/OL]. http://www.Freescale.com.

[14]杨剑新,胡向东,李媛. 一种分布控制双时钟FIFO的设计与实现[J]. 计算机工程与科学,2013(5):1-8.

蒋建武(1979-),男,高级工程师,苏州大学在读博士。主要研究方向为嵌入式系统、物联网技术,47955024@qq.com;

王宜怀(1962-),男,博士、博导,苏州大学计算机科学与技术学院教授,苏州大学嵌入式仿生智能研究所副所长,苏州市政协委员,中国软件行业协会嵌入式系统分会理事。主要研究方向为嵌入式系统、传感网与智能控制技术,Yihuaiw@suda.edu.cn。

ResearchonClockSystemStructureandConfigurationofKinetisSeriesMCU*

JIANGJianwu1,2,WANGYihuai1*

(1.School of Computer Science and Technology,Soochow University,Suzhou Jiangsu 215006,China;2.Department of Electronic and Information Engineering,Taizhou Polytechnic College,Taizhou Jiangsu 225300,China)

Kinetis series of MCUs embedded the core of ARM®CortexTM-M contains a complex clock system. At the time of each functional module in the clock system which includs multi-function clock generator,phase-locked loop,frequency-locked loopand crystal vibration system,coordinated work,the clock system can provide a stable clock source for the application system. Based on the analysis of the structure and configuration method of K60 clock system and the MCG operating mechanism,the testing method of clock source performance and the clock source selection method of each function modules are proposed. All of above provides references for Kinetis related chips clock system configuration in the process of application design as well as the clock source selection.

MCU(Micro Control Unit);clock system;MCG(Multiple Clock Generator)

项目来源:国家自然科学基金项目(61070169);泰州职业技术学院硕博基金项目(TZYBS-14-5)

2014-08-27修改日期:2014-09-28

TP368.1

:A

:1005-9490(2014)06-1172-05

10.3969/j.issn.1005-9490.2014.06.033