高速图像采集卡设计

2014-08-19刘丹于淳

刘丹 于淳

【摘 要】传统的图像采集卡速度慢、处理功能简单,不能很好地满足特殊要求,因此,我们构建了高速图像采集系统,在FPGA中利用VHDL编程实现,主要包括图像采集模块、图像低级处理模块以及总线接口模块等。

【关键词】图像采集 FPGA VHDL

中图分类号:G4 文献标识码:A DOI:10.3969/j.issn.1672-0407.2014.07.204

一、系统设计

本系统中专用视频处理器采用Philips公司的可编程视频输入处理芯片SAA7111A。它通过简洁的I2C总线与其它器件和设备连接可以将视频信号转换为多种格式的数字号。

最复杂的信号莫过于视频信号。视频信号中除了包含图像信号之外,还包括了行同步信号、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等。因而,对视频信号进行A/D转换的电路也非常复杂。Philips公司将这些非常复杂的视频A/D转换电路集成到了一块芯片内,从而生产出功能强大的视频输入处理芯片SAA7111A,为视频信号的数字化应用提供了极大的方便。

SAA7111A采用CMOS工艺。该器件通过简洁的I2C总线与PC机进行连接可方便地构成SAA7111A的开发系统。SAA7111A内部包含两路模拟处理通道,可以选择视频源并可抗混叠滤波,同时还可以进行模数变换、自动嵌位、自动增益控制、时钟产生、多制式解码等,另外还可对亮度、对比度和饱和度进行控制。SAA7111A芯片中的场同步信号VREF、行同步信号HREF、奇偶场信号RES1、 像素时钟信号LLC2都由管脚直接引出,省去了以往时钟同步电路的设计。系统内部锁相环技术的集成使得可靠性有了很大的提高,并降低了设计复杂度。

二、工作原理

系统复位完成FPGA程序加载后,先由FPGA的I2C总线模块对SAA7111初始化,本系统中SAA7111A的初始设定为:一路模拟视频信号输入、自动增益控制、625行50Hz 、PAL制式、YUV422 16bits数字视频信号输出、设置默认的图像对比度、亮度及饱和度。之后等待采集图像的命令。初始化成功后,SAA7111实时处理模拟视频信号,输出亮度和色度信号,同时输出点时钟信号,行、场同步信号,行、场参考信号,奇偶场标志信号等。

系统采集图像的命令由计算机发出,启动FPGA的采集同步模块。采集同步模块发出采集标志信号,采集一帧图像,通过写数据模块产生写地址和写信号将数据存储到SRAM中。采集结束时,采集标志信号撤消,采集同步模块复位,等待下一次采集命令。FPGA处理完1帧图像数据后,通过读数据模块生产读地址和读信号来实现将SRAM中的图像信息读出并通过PCI总线传送到计算机中。

在图像采集过程中,我们使用的是512×512的图像,即一帧图像采集512行,奇数场和偶数场各采集256行,每一行采集512个像素。因此,需要通过行延时模块进行行选择,滤掉无效行,通过像素延时模块进行像素选择,以选择需要的像素。

三、用VHDL硬件描述语言完成采集控制模块的行为描述

采集控制模块又包括几个子模块。因为SAA7111采用的是I2C总线,所以采集控制模块应包括:模拟I2C总线模块、采集同步模块、SRAM读写模块。

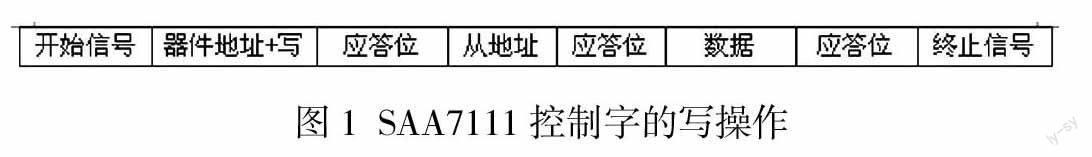

使用FPGA模拟的I2C接口可以对SAA7111提供的多个控制字进行读写,从而完全控制SAA7111的运行。对SAA7111的控制字的写过程如图1所示。

I2C协议中器件地址是7位,加上读写位构成一个完整的字节。SAA7111的器件地址是0100,101,加上读写位后:器件地址+写=0100 1010即4AH;器件地址+读=0100 1011,即4BH。从地址是器件内部分配的地址。SAA7111提供了00~1F、40~62共43个控制字。SAA7111读控制字的过程如图2所示。

I2C协议中的读操作比写操作复杂:首先完成对器件地址和从地址的写操作;然后发送4BH,可以开始接收数据;数据传输结束时发送终止信号。

整个图像采集部分是一个VHDL语言文件。FPGA采用串行主模式,从SPROM中读取配置数据,完成自身配置。当采集图像信号引脚再现大于等于场周期(20ms)的低电平信号时,可以确保该模块处于触发状态,在下一个奇数场出现时,根据SAA7111的场参考信号产生具有两场时宽的采集同步信号。该信号有效时为图像采集阶段,对SRAM1写入数据;该信号撤消时采集同步模块自动复位,等待下一次采集命令,同时FPGA1开始读取SRAM1中数据进行处理。采集同步信号有效的同时输出采集同步场参考信号,用于采集图像数据。