CMOS器件SEL效应电路级防护设计及试验验证

2014-08-07余永涛上官士鹏封国强马英起韩建伟

陈 睿,冯 颖,余永涛,上官士鹏,封国强,朱 翔,马英起,韩建伟

(1.中国科学院 国家空间科学中心,北京 100190;2.中国科学院大学,北京 100049;

3.北京电子工程总体研究所,北京 100854)

单粒子闭锁(SEL)效应[1-3]是体硅CMOS电路中的寄生4层PNPN结构的可控硅被触发导通,在电源与地之间形成低阻抗大电流通路,导致器件无法正常工作,甚至烧毁器件的现象。CMOS器件和电路具有功耗低、噪声容限大、温度稳定性高等优点,在现代卫星中有着不可替代的地位,而随着微电子特征尺寸的不断缩小,其中很多CMOS电路(特别是大规模和超大规模CMOS电路)的SEL敏感性也会随之显著增加[4],因此SEL效应的防护显得尤为重要。在空间飞行任务实施时常会遇到没有抗辐射加固产品供选用或条件不允许选用的情况,此时必须采取一定的SEL效应防护设计实现空间抗辐射加固的需求。

本文以IDT71V416S和K6R4016V1D两种CMOS SRAM器件为例,基于CMOS器件SEL效应机理及触发条件,在电阻限流防护技术基础上,设计恒流源限流SEL效应防护电路。利用脉冲激光模拟单粒子效应和重离子辐照试验方法,验证两种SEL防护电路的防护效果。

1 CMOS 器件闩锁效应电路级防护设计

CMOS器件闩锁效应触发条件的分析是进行其闩锁效应电路级防护设计的前提。大量研究[5-6]表明,CMOS器件SEL效应触发条件包括3个要素:1) 外界因素使寄生晶体管处于充分的正向偏置状态;2) 两个寄生晶体管电流增益积足够大,并形成正反馈,相应I-V区形成负阻特性,使内部电流迅速上升到更大;3) 外部电路提供足够的电源电流,使电路的闩锁状态得以维持。

由对CMOS器件SEL效应触发原理的分析可知,只要SEL效应触发条件中的任一条件不具备,器件便不会出现SEL现象。CMOS器件SEL效应电路级防护设计依据第3个要素展开,即控制外部电路提供电流小于其闩锁维持电流,避免寄生的PNPN结构持续闩锁,实现SEL效应的电路级防护。

1.1 电阻限流方法

传统的CMOS电路限流方法是在电源输入端串联电阻[7-8],达到限制器件输入电流的目的,如图1所示。其中,VDD为外部供应电压,I为器件工作电流,RL为限流电阻,VB为器件两端电压。

图1 传统CMOS电路电阻限流方法

当器件刚进入闩锁状态时,CMOS器件出现大电流通路可视为短路,此时VB≈0,VDD几乎全部施加在限流电阻上,即RL=VDD/IL。其中,IL为器件闩锁维持电流。

由CMOS器件工作特性可知,串联电阻对器件输入电压的影响不应超过器件额定电压容差ΔV(输入电源电压为5 V时器件的ΔV一般为0.5 V;3.3 V时器件的ΔV一般为0.3 V;2.5 V时器件的ΔV一般为0.25 V),否则,器件不能正常工作。由此可得到,串联电阻的取值范围在VDD/IL和ΔV/I之间时能较好地减缓SEL效应,此时IL≥IVDD/ΔV。

1.2 恒流源限流方法

SEL效应的恒流源防护方法是利用恒流源对器件输入电流进行限流控制,确保器件发生闩锁效应时,恒流源电流小于闩锁维持电流,导致器件不能维持闩锁状态。

图2所示的恒流源限流电路主要由恒流源电路、稳压管、电容、电阻构成,其中恒流源电流输出主要由三端稳压器控制,同时稳压器还可分流多余的电流;电容用于旁路器件的高频电流。在进行防护设计时,将恒流源电路的输出电流值设计成略大于器件的工作电流(器件手册允许的输入电流峰值),而小于器件的闩锁维持电流。当电路出现闩锁效应时,限定的器件输入电流小于闩锁维持电流,从而解除闩锁状态。

图2 恒流源防护设计电路示意图

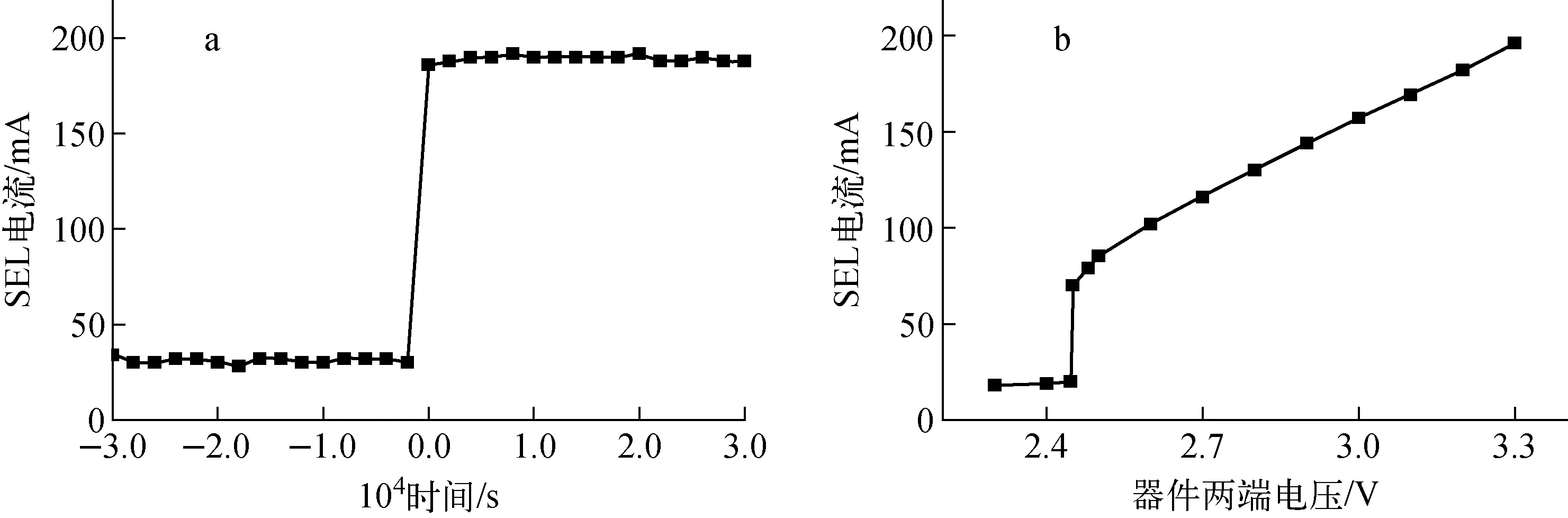

当器件工作电流略小于闩锁维持电流(I 利用中国科学院国家空间科学中心的脉冲激光单粒子效应试验装置[9],开展了CMOS器件SEL效应的试验研究。脉冲激光的主要技术参数为:激光波长1.064 μm;脉宽25 ns;光斑直径3~4 μm;脉冲重复频率1~50 kHz;等效LET值0.1~200 MeV·cm2/mg。试验样品分别选用同一批次SAMSUNG公司的0.18 μm K6R4016V1D和IDT公司的0.13 μm IDT71V416S各3片,工作电压均为3.3 V。两种SRAM器件均采用塑料封装,正面有金属层。由于激光无法穿透塑料封装和金属层,所以在进行SEL效应激光试验前,先对器件进行开背部封装处理,以露出背部的硅衬底层进行背部辐照。脉冲激光诱发SEL效应后,减小器件两端电压,记录SEL闩锁电流随器件两端电压的变化关系,器件退出闩锁状态时的电压(电流)即为闩锁维持电压(电流)。 图3、4分别为脉冲激光诱发IDT71V416S和K6R4016V1D器件发生SEL效应时闩锁电流的变化特性。当激光入射能量为20 nJ(等效LET值为6 MeV·cm2·mg-1)时[10],IDT71V416S出现SEL效应,器件工作电流从35 mA迅速增大至202 mA,如图3a所示。图3b为SEL电流与器件两端电压的关系。可发现,SEL电流随器件两端电压的减小而减小,当器件两端电压为2.45 V时,SEL电流瞬间从70 mA降至20 mA,器件退出闩锁状态。此时,70 mA即为器件的闩锁维持电流。从图4可看出,当激光入射能量为2 nJ(等效LET值为1 MeV·cm2·mg-1)时[10],K6R4016V1D出现闩锁现象,工作电流从3 mA迅速增大到闩锁电流268 mA;当器件两端电压为1.32 V,SEL电流为8 mA时,器件退出闩锁状态。 图3 IDT71V416S SEL电流随时间的变化(a)及SEL电流与器件两端电压的关系(b) 图4 K6R4016V1D SEL电流随时间的变化(a)及SEL电流与器件两端电压的关系(b) 结合CMOS SRAM器件IDT71V416S和K6R4016V1D的SEL效应特性,采用上述两种SEL效应防护方法分别进行电路级辐射加固,并通过脉冲激光和重离子辐照试验,验证SEL效应防护电路的效果,防护加固电路与未防护加固电路的辐照条件相同。图5、6分别为IDT71V416S和K6R4016V1D进行SEL防护设计后,在脉冲激光辐照下,SEL电流的变化曲线。 从图5a和图6a可看到,两种CMOS器件的SEL电流随限流电阻的增大均不断减小。图5a中,当限流电阻增加到10 Ω时,IDT71V416S的锁定电流从196 mA减小至94 mA,此时,限流电阻对器件输入电压的分压为0.35 V,其超出了器件电压允许的容差范围,因此限流电阻只能选取8 Ω。图6a中,限流电阻为150 Ω时,SEL电流减小的幅度最大,但其对器件输入电压的影响也最大,在器件电压允许的容差范围内,限流电阻最大只能选取100 Ω。采用电阻限流防护设计后,两种CMOS器件的闩锁电流均明显减小,有效延长了器件闩锁到失效的时间,实现了闩锁效应的加固,但其仍未退出闩锁状态。 图5 电阻限流防护(a)和恒流源防护(b)后IDT71V416S SEL电流随时间的变化 图6 电阻限流防护(a)和恒流源防护(b)后K6R4016V1D SEL电流随时间的变化 进行恒流源限流SEL效应防护加固后,两种CMOS器件SEL电流的变化曲线示于图5b、6b。IDT71V416S和K6R4016V1D器件的SEL电流较防护设计前的小,且在很短的时间内可恢复到正常工作时的电流值,此时器件工作正常。这表明在进行恒流源限流防护设计后,在相同辐照条件下,虽然器件此时形成了闩锁通道,但由于限制了电路电流的变化,使得器件闩锁状态不能保持,最终退出了闩锁状态。 图7为采用重离子辐照时,采用限流电路防护方法前、后IDT71V416S器件SEL电流的变化趋势。辐照试验采用北京大学重离子物理研究所25 MeV、束流强度108cm-2·s-1的12C离子。被测器件经正面开封装处理。由图7可见,未采用SEL效应防护时,器件出现闩锁效应,SEL电流瞬间增大至200 mA。进行恒流源限流防护设计后,在相同的辐照条件下,器件未出现闩锁效应。这表明恒流源限流防护电路对SEL效应起到了较好的防护作用。 图7 IDT71V416S SEL电流随辐照时间的变化 体硅CMOS器件中固有的寄生双极性晶体管结构是导致SEL效应的根源,图8为CMOS器件中寄生的NPN和PNP双极晶体管。离子入射触发寄生双极晶体管导通,形成正反馈电流回路,进而导致SEL效应。不同规模的CMOS电路其SEL效应产生的机制是相同的,主要的区别在于器件工作电流与闩锁维持电流不同(通常大规模CMOS器件的工作电流可达100 mA,中小规模的CMOS器件工作电流为几mA至几十mA)。因此,本文基于CMOS器件SEL效应触发条件,以两种CMOS SRAM器件为例进行防护电路设计及试验验证,所设计的CMOS器件电路级闩锁防护电路具有普适性。 图8 CMOS器件寄生双极晶体管剖面图 由两种CMOS SRAM器件SEL的响应特性可知,CMOS器件SEL响应特性与外部供应电源、器件的电路设计及制造工艺等相关。大量研究[11-12]表明,器件的闩锁电流随外部供应电压和器件工艺尺寸的增大而增大,这可能是在外部供应电压同为3.3 V时,造成0.18 μm K6R4016V1D的闩锁电流幅值较0.13 μm IDT71V416S大的主要原因。而CMOS器件闩锁维持电流(电压)主要受器件内部工艺设计(阱电阻率和阱接触到源漏区的距离)的影响,阱电阻率越大,阱接触离源漏的距离越远,器件对闩锁越敏感,相应退出闩锁状态的电压就越低。 通过两种SEL效应防护电路的辐照验证试验可发现,在CMOS器件I/O端串联大阻值限流电阻虽能更好地降低SEL电流的幅值,但其影响了器件的正常工作。选择合适的限流电阻能有效降低SEL阈值,但不能避免进入闩锁状态。相关研究[12]表明,现代CMOS工艺器件通常具有电压转换电路和片上电容,在I/O 端串联电阻的限流效果受到器件内部转换电路和片上电容充放电的影响,这亦是电阻限流方法不能避免器件进入闩锁状态的主要原因。 与电阻限流SEL效应防护方法相比,恒流源限流防护电路通过独立的电路控制电源供应电流的大小,受器件内部电压转换电路的影响较小,其不但降低了SEL电流的幅值,而且自动退出了闩锁状态,能有效对CMOS电路闩锁效应进行防护。在实际工程应用中,器件I/O 端串联电阻还会带来发热问题,因此,选取串联电阻时应考虑其引入的发热是否对电路有影响。恒流源限流电路的设计应尽量选用电阻、电容及晶体管等对SEL效应不敏感的元件,避免恒流源限流防护电路自身引入的闩锁问题。 通过本文的研究,可得出以下结论。 1) 器件工作电流I与闩锁维持电流IL是设计限流电阻阻值和恒流源电流大小的关键。 2) 电阻限流防护电路中串联电阻的取值范围在VDD/IL和ΔV/I之间时能较好地减缓SEL效应。 3) 当器件工作电流和闩锁维持电流相差不大时,在电源输入端串联限流电阻易影响器件的正常工作。 4) 与电阻限流SEL效应防护方法相比,恒流源限流防护电路不但降低了SEL电流的幅值,而且自动退出了闩锁状态,能有效实现CMOS器件电路级闩锁效应的防护。 5) 实际工程应用中,恒流源限流防护电路尽量选用电阻、电容及晶体管等对SEL效应不敏感的元件,以增加恒流源限流防护电路自身的抗SEL性能。 参考文献: [1] SCHWANK J R, SHANEYFELT M R, DODD P E. Radiation hardness assurance testing of microelectronic devices and integrated circuits: Test guideline for proton and heavy ion single-event effects[R]. Albuquerque, New Mexico: Sandia National Laboratories, 2008. [2] FELIX J A, SCHWANK J R, SHANEYFELT M R, et al. Test procedures for proton-induced single event latch-up in space environments[J]. IEEE, 2008, 55(4): 2 161-2 165. [3] BECKER H N, MIYAHIRA T F, JOHNSTON A H. Latent damage in CMOS devices from single-event latch-up[J]. IEEE Trans Nucl Sci, 2002, 49(6): 3 009-3 015. [4] THOMAS P E, BENEDETTO J M. Extreme latch-up susceptibility in modern commercial-off-the-shelf (COTS) monolithic 1M and 4M CMOS static random-access memory (SRAM) devices[C]∥IEEE Radiation Effects Data Workshop. [S. l.]: IEEE, 2005: 1-7. [5] JOHNSTON A H, BAZE M P. Experimental methods for determining latch-up paths in integrated circuits[J]. IEEE Trans Nucl Sci, 1990, NS-32(6): 4 260-4 265. [6] BRUGUIER G, PALAU J M. Single particle induced latch-up[J]. IEEE Trans Nucl Sci, 1996, 43(2): 522-532. [7] PUCHNER H, KAPRE R, SHARIFZADEH S, et al. Elimination of single event latch-up in 90 nm SRAM technologies[C]∥IEEE 44th Annual International Reliability Physics Symposium. San Jose: IEEE, 2005: 721-722. [8] SCHROEDER J, OCHOA E, DRESENDORFER P V. Latch-up elimination in bulk CMOS LSI circuits[J]. IEEE Trans Nucl Sci, 1980, NS-27(6): 1 735-1 738. [9] 韩建伟,张振龙,封国强,等. 利用脉冲激光开展的卫星用器件和电路单粒子效应试验[J]. 航天器环境工程,2009,26(2):125-129. HAN Jianwei, ZHANG Zhenlong, FENG Guoqiang, et al. Single event effect experiment for devices and circuits aboard on satellite using pulsed laser[J]. Spacecraft Environment Engineering, 2009, 26(2): 125-129(in Chinese). [10] 黄建国,韩建伟. 脉冲激光模拟单粒子效应的等效LET计算[J]. 中国科学:G辑,2004,34(6):601-609. HUANG Jianguo, HAN Jianwei. Calculation of LET in SEE simulation by pulsed laser[J]. Science in China: Series G, 2004, 34(6): 601-609(in Chinese). [11] HARGROVE M J, VOLDMAN S, BROWN I, et al. Latchup in CMOS technology[C]∥IEEE 36th Annual International Reliability Physics Symposium. Reno: IEEE, 1998: 269-278. [12] STEVEN H V. CMOS latch-up[M]. England: John Wiley & Sons Inc., 2008.2 CMOS器件闩锁防护技术的试验研究

2.1 CMOS器件SEL效应试验

2.2 CMOS器件闩锁防护技术验证试验

2.3 试验结果分析

3 结论