基于WSAR-ADC的降压型DC-DC控制器设计

2014-05-15田登尧冯全源

田登尧,冯全源

西南交通大学微电子研究所,四川成都 610031

基于WSAR-ADC的降压型DC-DC控制器设计

田登尧,冯全源

西南交通大学微电子研究所,四川成都 610031

设计了一种基于加窗逐次逼近寄存器(WSAR)模拟数字转换器(ADC)的降压型DC-DC控制器,这种WSAR-ADC适用于数字电源系统,通过对输入电压进行加窗处理,能有效地降低芯片的复杂度;并利用蚁群算法,对该DC-DC控制器的比例积分微分(PID)参数进行了整定,使得整个系统能够稳定工作。电路使用BCD(Bipolar/CMOS/DMOS)0.5 μm工艺,输入电压3.3 V,输出电压1 V,设计最大负载电流2 A,纹波小于9 mV,开关频率500 kHz。经过验证,该降压型DC-DC控制器能满足数字电源的采样需求。

加窗;逐次逼近寄存器型;模数转换器;数字电源;PID;DC-DC控制器;buck电路

随着集成电路技术的发展,高性能电子系统不断涌现,既为电源的设计提供了可靠的工艺保证,同时也对电源系统的性能提出了苛刻的要求[1-6]。数字电源技术因为其应用灵活、可编程、可移植、较高的可靠性等特性[7-8],得到了人们的关注。在有些文献中,提出了限流和时间控制的观念,来解决环路控制问题[9]。另一些文献中,通过在线频响测量解决了PID(proportion integration differentiation)参数的自适应问题[10]。这些都是为了使环路能有更好的瞬态响应。然而数字控制虽然在板级电源中得到了大量应用,却在IC级电源中未能大量实施,制约其发展的核心就是低复杂度的ADC的设计。

在数字电源中,ADC的性能对整个数字电源系统的影响比较大。而ADC中比较重要的就是分辨率和采样率这2个参数。ADC的分辨率制约着输出电压的精度,而采样率则是制约着数字电源系统的开关频率的提高。ADC已经成为DC-DC芯片由传统模拟控制朝向数字控制的核心制约因素。

文中针对数字电源中的ADC,从众多ADC类型中选用了逐次逼近寄存器型ADC,这种ADC相对于其他ADC来说具有较低的复杂度。而基于DC-DC反馈控制信号在稳态工作时具有较小波动性的特点,故对这种传统的SAR(successive approximation register)-ADC进行了加窗处理,进一步降低了该ADC的复杂度。在数字电源这种特定的环境中,该WSAR(window successive approximation register)-ADC的时钟频率得以降低,但完成了较高频率SAR-ADC的功能。在此基础上,使用蚁群算法对该数字电源的PID参数进行了整定,使得整个的数字电源的设计周期能够大大地减少。

1 系统设计

如图1所示,文中的数字电源采用的buck结构,由于文中所采用的输入电压不高于5 V,故高端管采用了低压PMOS管M1,低端管采用了低压NMOS管M2,其中还设置了电感等效电阻RL和电容等效电阻RC,以便于在仿真中能够更好地接近实际,加快电路的验证过程。

图1 数字电源整体结构

在整个环路中,WSAR-ADC将输出电压信号Vout变成数字信号,然后用PID数字补偿器使整个环路有足够的相位裕度来保证整个环路能够稳定工作,最后将控制信号转变为PWM信号,来控制电压的输出。

2 WSAR-ADC设计

在当前众多的ADC中,表1中所示的几种ADC比较常见。

表1 常见类型ADC比较

从表1的统计分析可以看出,SAR从精度、转化速率上来说,都能够满足开关电源的要求,尤其是在功耗和面积上,是所有ADC类型中最小的,能够大大降低开关电源芯片的成本和提高开关电源芯片的整体效率。

在文中,实际上采用的是5位的SAR-ADC,如果换成了FLASH的ADC,需要用2×5-1=9个比较器。而SAR-ADC只需要1个比较器,这样能大大降低功耗和面积。在当前众多的开关电源中,无论模拟还是数字,多数开关频率都在1 MHz以下,这不仅是为了降低功耗,还为了能够有更低的设计成本,所以在本中,采用了500 kHz采样率来验证WSAR-ADC的正确性,以便于今后设计出更适合的开关电源ADC。

2.1 传统SAR-ADC工作原理

传统电荷再分配型SAR-ADC如图2所示,它由4部分组成:开关网络、电容阵列、比较器、SAR逻辑控制。它的工作主要分为4个阶段。

图2 传统电荷再分配型SAR-ADC电路结构

1)放电阶段。

该阶段中,S1闭合,b0~b5端接到地端。即将电容阵列的两端短接起来。将电容两端的电荷放掉。

2)预充阶段。

该阶段中,S1继续闭合,S2接到Vin,b0~b5接到S2开关,将6个电容充电充到Vin。

3)保持阶段。

S1断开,b0~b5接到地,此时进入电荷保持阶段,比较器负端此时电平为-Vin。

4)判定阶段。

S2接入到Vref,b5接到S2端,将比较器的输出记录到SAR寄存器中,若比较器输出为低,则将b5接到地,否则b5保持到S2端。接下来,按上述规律,依次将b4到b1接到S2端,并将b4到b1记录到SAR寄存器中,则将b5到b1记录的5个数字信号输出为D4~D0,此时,即将Vin转化为数字信号。

式(1)表征了输出数据与Vin和Vref的关系。

2.2 WSAR-ADC的设计

在文中使用了加窗的SAR-ADC,即WSAR-ADC,该ADC采用了一个动态的参考电压来减少整体功耗。由于在数字电源应用中,大多数时间里误差信号变化都很小,往往只有几十毫伏,那么在数字电源中就没有必要采用满量程的ADC。这也是因为除了瞬态变化之外,输出电压基本保持不变;甚至在负载或者输出电压变化时,输出电压也会被限制在所设计的范围内。因此,输入电压可以被设置在上限制Vupper和下限制Vlower,如图3所示。WSAR-ADC就是在图2传统的SAR-ADC基本结构通过加窗而来,Vupper和Vlower被设置在图2中的Vref附近。

图3 WSAR-ADC结构

由以上分析可以得出在WSAR-ADC结构中,Vin、Vlower、Vupper和数字输出D4~D0的关系。

这个WSAR-ADC需要8个时钟周期来进行数据转化。在第1个时钟周期中,数据被采样到输入引脚。第2个时钟周期,数据被保持。接下来5个时钟周期输出数据从高位到低位依次被判定。最后,这个数据就被转化出来了。在文中,ADC的时钟频率为4 MHz,那么该WSAR-ADC的转化速率就是500 kHz。选择该转化速率,可以在保证低功耗的情况下减少影响频率响应的相位滞后的延时。

在文中,该ADC能够达到4 mV的分辨电压,而传统的SAR-ADC在3.3 V下只能达到约100 mV的分辨电压。从该分析中可以看出,相对于用传统的SAR-ADC来实现,WSAR-ADC可以利用较低的时钟频率和更少的模拟开关、电容等器件,实现较高的采样率和分辨率,大大减少了ADC设计的复杂度。

3 DPWM和数字PID的实现

3.1 数字脉宽调制电路

脉宽调制电路(pulse width modulation,PWM)实现系统中数模转换的功能。由于不连续的量化将导致输出电压值的不连续,因此,一个分辨率较低的PWM将引起极限环(limit-cycle)的出现,进而增加输出电压纹波,影响系统的稳定性。这就需要一个高分辨率的PWM电路来满足性能要求[11]。PWM的分辨率必须要大于ADC的分辨率,才能保证不影响其环路稳定性。

文中设计了一个DPWM电路,用来产生PWM信号,其中DAC是在Cadence环境下,采用Verilog-A编写的理想12位的数模转化器。在3.3 V输入电压时,其最小分辨电压为0.8 mV,完全满足系统要求。

如图4所示,该DPWM由3部分组成,锯齿波产生器、DAC和比较器。锯齿波产生器产生频率为开关频率的锯齿波,与DAC输出的电压进行比较,从而输出频率为开关频率的PWM信号。

图4 DPWM结构

3.2 数字PID参数的整定

PID控制系统的原理框图如图5,系统主要由PID控制器和被控对象两部分组成。

图5 PID控制系统原理

根据给定的输入量r(n)和输出量y(n),构成控制偏差e(n)=r(n)-y(n),将偏差按比例、积分和微分通过线性组合构成控制量,对被控对象进行控制,其控制规则为

式中:u(n)为本次控制量,e(n)为本次偏差,KP为比例因数,KI为积分因数,KD为微分因数,Ts为采样周期。PID控制器S域的传输函数如下:

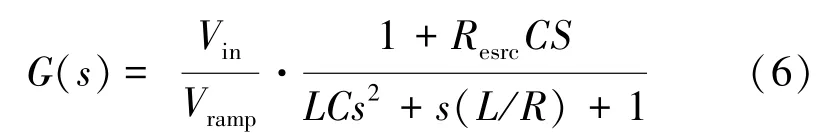

从式(5)可以看出,如果在被控对象模型和采样周期TS给定的情况下。PID控制器只有KP,KI和KD这3个参数需要确定。因此,PID控制系统的设计问题实际上就是控制参数的整定优化问题。同时,考虑斜坡电压和Resrc(等效电容串联电阻),可得约简后降压型的传输函数[12]:

式(6)为一般的buck型的传输函数,对于模拟电路较为适用。但在数字型buck电路中,必须考虑到延时对系统的影响。本电路是在每个开关周期的一半进行采样,并在半个周期后改变PWM的占空比,即延时0.5个开关周期,其修正公式如下:

式中:Td为延时,文中Td=0.5Ts。

在文中,采用了蚁群算法[13]来对3个参数来进行优化。在MATLAB中多次运行,取其中最好值,可得KP=0.588,KI=0.658,KD=9.229。将该值和表4中的数据带入到MATLAB的sisotool工具箱中,在输出负载R=0.5 Ω和R=1 000 Ω时运行得到其波特图如图6、7所示。由图6、7可以看出,经过补偿后系统最低有63.8°的相位裕度,最高有78.1°的相位裕度,可以保证系统的稳定运行。

图6 经过PID补偿后的波特图(R=0.5 Ω)

图7 经过PID补偿后的波特图(R=1 000 Ω)

将PID的3个参数带入到在Cadence AMS环境用Verilog编写了PID模块中,其代码如下:

4 仿真结果分析

通过对数字电源整体的分析与设计,利用Ca-dence AMS数模混合仿真工具对WSAR-ADC的数字电源进行了仿真。仿真时输入电压为3.3 V,输出电压为1 V,电感4.7 μH,电容44 μF,等效串联电感为10 mΩ,等效串联电容为10 mΩ,负载为2 A时稳态输出纹波为8.5 mV,WSAR-ADC采用BCD0.5μm。经过测试,该控制器能稳定工作在1 mA~2 A。图8是对其阶跃响应做了测试。

图8 负载电流跳变

表2 DC-DC控制器芯片参数

从图8可以看出,在电流按照1~1.5~1 A来变化,控制器对电流变化快速响应,输出电压产生了128 mV的变化,并在约136 μS后电压稳定。表4给出文中设计的DC-DC控制器的参数。通过图8中的对整个系统阶跃响应测试可以看出,文中的WSAR-ADC可以很好地工作于数字电源中,并有着较好的阶跃响应特性。同时,文中的WSAR-ADC测得动态功耗为45.5 μW,其中WSAR-ADC中的比较器的动态功耗为44.2 μW。基本符合开关电源设计要求,充分验证了该WSAR-ADC在电源中应用的可行性。

5 结束语

设计了一种采用WSAR-ADC的数字DC-DC转换器。其输出电压为1 V,负载电流可达2 A。在该电源系统中,主要是对传统的SAR-ADC利用加窗的方法进行了改进。使得该ADC的整体功耗和复杂度都大大降低。针对该WSAR-ADC给出了系统级的测试方法,并开发关键的行为级代码,即对于不同应用,不同的输出电压、电流和不同的电感电容值,采用蚁群算法对PID参数进行整定,使得该控制器能够应用到更广泛的范围去,相对模拟控制的开关电源来说也具有很大的灵活性。为进一步研究数模单片全集成的数控DC-DC奠定了基础。

[1]PRODIC B J,ZIRGER A,MAKSIMOVIC A.High-frequency digital controller IC for DC/DC converters[J].IEEE Trans on Power Electronics,2003,18(1):438-446.

[2]YU Wensong,LAI Jinsheng,MA Hongbo,et al.High-effi-ciency DC-DC converter with twin bus for dimmable LED lighting[J].IEEE Trans on Power Electronics,2011,26(8):2095-2100.

[3]倪雨,许建平.基于等效控制的全局滑模控制buck变换器设计[J].西南交通大学学报,2009,44(5):654-659.

[4]秦明,许建平,牟清波.脉冲序列buck变换器的控制规律及特性[J].西南交通大学学报,2009,44(5):660-666.

[5]向乾尹,冯全源.Boost DC/DC低压启动能力研究[J].西南交通大学学报,2011,46(4):591-597.

[6]马红波,冯全源.Buck型开关变换器最优PID控制器设计[J].电机与控制学报,2008,12(6):639-643.

[7]DANCY A P,AMIRTHARAJAH R,CHANDRAKASAN A P.High-efficiency multiple-output DC-DC conversion for low-voltage systems[J].IEEE Trans Very Large Scale Integr.(VLSI)Syst,2000,8(3):252-263.

[8]WEI G,HOROWITZ M.A low power switching power supply for self-clocked system[J].Proc IEEE Int Symp Low Power Electron,1996,1(1):313-317.

[9]CORRADINI L,BABAZADEH A,BJELETIC A,et al.Cur-rent-limited time-optimal response in digitally controlled DC-DC converters[J].IEEE Trans Power Electron,2010,25(11):2869-2880.

[10]SHIRAZI M,ZANE R,MAKSIMOVIC D.An autotuning digital controller for DC-DC power converters based on on-line frequency response measurement[J].IEEE Trans Pow-er Electron,2009,24(11):2578-2588.

[11]PETERCHEV A V,SANDERS S R.Quantization resolution and limit cycling in digitally cont rolled PWM converters[J].IEEE Trans Power Electronics,2003,18(1):301-308.

[12]ERICKSON R W,MAKSIMOVIC D.Fundamentals of power electronics[M].2nd ed.Norwell:Kluwer Academ-ic Publisher,2001,1(1):354-361.

[13]DORIGO M,BLUMB C.Ant colony optimization theory:a survey[M].Theoretical Computer Science,2005,344(1):243-278.

A buck DC-DC controller based on WSAR-ADC

TIAN Dengyao,FENG Quanyuan

Institute of Microelectronics,Southwest Jiaotong University,Chengdu 610031,China

A buck DC-DC controller based on window successive approximation register(WSAR)and analog-to-digital converter(ADC)was designed.It is applicable to digital power system.The circuit complexity can be re-duced by adding the window function to process input voltage;and the PID(proportion integration differentiation)parameters setting of the DC-DC controller is completed using the ant colony algorithm,which makes the whole sys-tem work stably.The circuit is implemented under Bipolar/CMOS/DMOS(BCD)0.5 μm process,the input volt-age is 3.3 V,and the output voltage is 1 V.The designed maximum load current is 2 A,the ripple of output voltage is less than 9 mV.After verification,the switch frequency is 500 kHz.This buck DC-DC controller can meet the demand of digital power sampling.

windows;successive approximation register;ADC;digital power;PID;DC-DC controller;buck circuit

TN495

A

1009-671X(2014)05-001-05

10.3969/j.issn.1009-671X.201312013

2013-12-24.

日期:2014-09-24.

国家自然科学基金重大资助项目(60990320;60990323);国家自然科学基金面上资助项目(61271090);863计划重大资助项目(2012AA012305).

田登尧(1988-),男,博士研究生;

冯全源(1963-),男,教授,博士生导师.

冯全源,E-mail:fengquanyuan@163.com.

http://www.cnki.net/kcms/doi/10.3969/j.issn.1009-671X.201312013.html