半加成法制作30 µm精细线路及其工艺优化

2014-04-25江俊锋电子科技大学微电子与固体电子学院四川成都610054陈世金博敏电子股份有限公司广东梅州514000

江俊锋 何 为 冯 立(电子科技大学微电子与固体电子学院,四川 成都 610054)陈世金 周 华(博敏电子股份有限公司,广东 梅州 514000)

半加成法制作30 µm精细线路及其工艺优化

江俊锋 何 为 冯 立

(电子科技大学微电子与固体电子学院,四川 成都 610054)

陈世金 周 华

(博敏电子股份有限公司,广东 梅州 514000)

在公司制程能力为70μm/70μm的工艺条件下,运用半加成法探索进行线宽为30μm的挠性双面板精细线路制作工艺研究。通过正交试验法的L9(34)正交表设计对精细线路制作中的显影速度、显影压力、蚀刻速度、蚀刻压力四个因素进行工艺优化,确定了线宽为30μm的挠性双面板精细线路制作的最佳条件。结果表明,显影速度为主要影响因素。

半加成法;精细线路;正交试验法;工艺优化

1 前言

挠性印制电路板由于具有轻、薄、短、小、结构灵活的特点,在封装基板的选材上得到了广泛的运用[1]。同时,进一步在挠性基板上制作线宽/线距小50 µm/50 µm的精细线路更能满足封装基板的高密度需求。

减成法是制作挠性印制板(FPC)线路的最常用方法,但其制作的线宽/线距受到感光抗蚀层的分辨率及侧蚀等因素的制约,难以制作线宽/线距小于50 µm/50 µm的精细线路。如果要制作更加精细的线路,可采用半加成法。半加成法的主要原理[2]是利用图形电镀加厚线路区域,那些被干膜保护没有进行电镀加厚的区域在差分蚀刻过程中被很快的除去,剩下的部分被保留下来形成线路。通过控制图形电镀的时间,能够很容易调节最终线路的厚度。目前已经商品化的铜箔中,应用最多的薄铜箔为12 µm。一旦低于这个数值,当厚度进入9 µm,5 µm甚至2 µm的范围时,其价格迅速上升,导致成本居高不下。如果能自行在12 µm铜箔的基础上将其减薄后变成超薄铜箔来使用,将会大大降低成本。本实验就是先对铜箔进行减薄至3.5 µm,再考察运用半加成法制作精细线路的可行性。

精细线路的整个制作流程需要控制的因素很多,因此想要制作合格的精细线路需要注意每一个工艺流程。胡友作等[3]采用减成法工艺及正交试验设计对蚀刻速度、显影速度、曝光能量三个因素进行优化,制作出40 µm/40 µm线路。但其参考指标仅考虑线宽,对精细线路的判定标准缺乏说服力。本试验是在公司FPC厂原有制程能力为70 µm/70 µm的工艺条件下,探究半加成法制作挠性双面板30µm精细线路的工艺条件。通过L9(34)正交试验的设计,对显影速度、显影压力、蚀刻速度、蚀刻压力四个因素进行工艺优化及分析,确定制作30 µm精细线路的最佳条件。

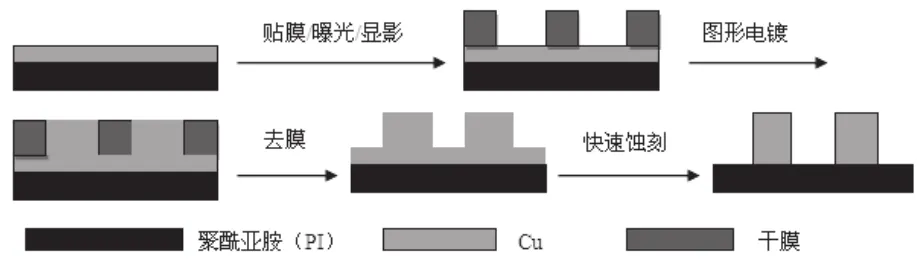

2 半加成法工艺过程

本试验采用12 µm铜箔减薄到3.5 µm,利用图形电镀将线路部分加厚到18 µm,未电镀加厚的非线路部分采用快速蚀刻工艺,最后得到线宽为30 µm的精细线路。其工艺流程图[4]如图1所示。

图1 半加成法工艺图

3 实验

3.1 实验仪器

自动贴膜机、LDI曝光机、水平显影、蚀刻、退膜(DES)线、减铜线、线宽测量仪、铜厚测试仪、金相显微镜、垂直连续电镀线(VCP线)

3.2 实验材料

台虹双面无胶电解铜箔(铜厚12 µm)、殷田AQ-20SD干膜(膜厚20 µm),碳酸钠体系显影液、盐酸氯化铜体系蚀刻液、氢氧化钠体系退膜液等

3.3 实验步骤

3.3.1 精细线路的制作过程

整个试验流程如图2所示。

选用铜箔为12 µm的挠性双面覆铜箔层压板,在硫酸双氧水体系中减铜至(3.5±0.5)µm,在不开磨刷的喷砂线上稍作处理,采用湿法贴膜工艺,热压贴覆AQ-20SD干膜。贴膜15 min后采用LDI曝光机完成曝光过程,控制曝光能量为30 mJ/cm2,至少15 min后进行显影过程。显影后在VCP垂直连续电镀线上控制电流密度为1.6 A/dm2,电镀时间为35 min,将正片线路部分加厚到18 µm。在退膜线上除去剩余保护性干膜,确保退膜干净后采用盐酸氯化铜体系蚀刻液进行快速蚀刻。

图2 试验流程图

3.3.2 试验因素的选择

电解铜箔为硫酸铜电解液直流电下阴极电沉积,铜微粒结晶结构在蚀刻时容易形成垂直的线条,有利于精细线路的制作。选用LDI曝光工序,省去了常规曝光过程中底片工序,减少因底片胀缩引发的偏差。同时图形解析度高,非常有利于精细线路的制作。

精细线路的显影过程要求很严,显影不足,未感光的干膜部分没有完全去除,会导致线路间残胶,造成蚀刻不净甚至短路;显影过度,干膜在显影液中停留时间过长,导致干膜过分溶胀,使干膜与铜面结合力下降甚至起翘、脱落,使蚀刻时断线。蚀刻时,蚀刻过慢,容易造成线路部分过度蚀刻,侧蚀严重,甚至造成线路断路;蚀刻过快,容易造成线路跨接而短路。所以本文重点考察对精细线路制作影响较大的显影速度、显影压力、蚀刻速度和蚀刻压力。

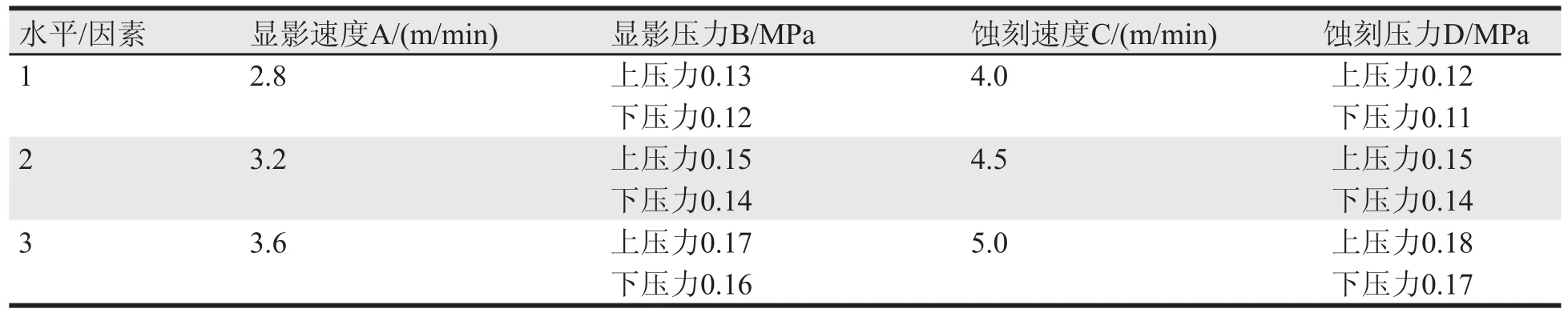

采用L9(34)正交试验[5]的设计,选取显影速度、显影压力、蚀刻速度、蚀刻压力四个因素进行工艺优化,其因素—水平表如表1所示。

4 正交试验与分析

4.1 正交试验结果

正交试验显影和蚀刻后结果如表2所示。

4.2 极差分析

根据表2,作出蚀刻后的线宽指标—因素图,如图3所示。

表1 因素—水平表

表2 正交试验安排及其结果表

图3 蚀刻后线宽指标—因素图

对图3进行分析,可以看出因素主次顺序为:A>C>D>B,即显影速度为主要决定因素,蚀刻速度和蚀刻压力为第二阶梯决定因素,而显影压力影响较小。试验安排时,查阅相关文献知显影压力为极难控制因素,显影压力只能做小范围变化。

显影过程控制显影速度A及显影压力B两个因素,通过对显影后平均线宽的分析可得:随着显影速度的增大,显影后的线宽有逐步减小的趋势。随着显影速度的增大,干膜与显影液反应的时间减小,溶解的膜也越来越少,造成线路部分逐渐变窄。而显影压力小幅度增大,使显影液与干膜接触更充分,退膜更完全,则线宽有增大趋势,但变化范围不明显。

蚀刻过程控制蚀刻速度C和蚀刻压力D两个因素,通过对蚀刻后平均线宽的分析可得:随着蚀刻速度的增大,蚀刻后的线宽有逐渐增大的趋势。因为蚀刻速度增大,蚀刻液与铜箔反应时间相应减小,使线路蚀刻程度减小。而蚀刻压力增大,使蚀刻线宽呈现出先减小再增大的趋势。

4.3 线宽均匀性分析

本试验目的是制作30 µm精细线路,所以对于试验指标,即蚀刻后线宽,要求越接近设计值越好。

根据图3,对于A因素,线宽波动较大,说明了显影速度的重要性。笔者认为在显影时,既要考虑相应膜的显影速度范围,也要结合显影线的实际显影效果。相比起来,最适合A因素的为A2。 B因素由于变化不大,在允许误差变化范围内可选很多,根据最佳效果,显影压力为B1。C因素的C1和C2变化不大,在30 µm附近变化,均可选择。D因素的D1和D2线宽均接近30 µm,但观察到蚀刻压力在D1状态时偏小,D1状态的蚀刻压力下线宽偏离度大于D2状态下的偏离度,选择D2更好。综上,可得适合制作30 µm线宽的组合有A2B1C1D2,A2B1C2D2,对其作最后探究。

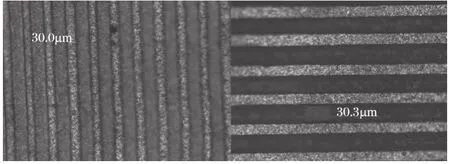

A2B1C1D2组合显影后平均线宽为30.57 µm,蚀刻后平均线宽为30.42 µm,如图4所示(注:标注值仅代表此条线宽)。

图4 A2B1C1D2组合显影及蚀刻后线宽

A2B1C2D2组合显影后平均线宽为30.93 µm,蚀刻后平均线宽为30.81 µm,如图5所示。

图5 A2B1C2D2组合显影及蚀刻后线宽

两组由于显影条件相同,故显影后线宽差别不大,观察到显影后线宽均略大于30 µm。因为后续盐酸氯化铜蚀刻液蚀刻速率较快,极易造成过度蚀刻。在工程资料设计时,将线宽设计略大于30 µm。蚀刻后线宽虽然A2B1C2D2组合略大,但在可接受误差范围内。

4.4 蚀刻因子分析

蚀刻因子是评定线路质量的重要指标,蚀刻因子(F)定义为蚀刻深度(H)与侧蚀宽度(X)之比[1]。蚀刻因子越大,表明侧蚀越轻。

根据实际蚀刻因子计算方法[6],可得A2B1C1D2组合的蚀刻因子为3.31,A2B1C2D2组合的蚀刻因子为3.63。虽然两组差别不大,但考虑到多组线条综合引起的偏差,A2B1C2D2组合是更好的选择。原因是A2B1C2D2组的蚀刻速度更快,线路边缘处与蚀刻药液接触时间变短,减小了侧蚀程度。设计时,线距设计为35 µm,但观察到下线距略大,上线距由于侧蚀偏差更大,说明盐酸氯化铜蚀刻液的蚀刻能力极强。这也进一步说明在盐酸氯化铜蚀刻液中选择相对较大的蚀刻速度是更好的选择。

4.5 正交试验小结

本试验指标线宽均匀性越接近设计值越好,蚀刻因子越大越好。对因素A分析,其对试验结果影响显著,确定优水平为A2;因素B的水平改变对试验结果影响很小,从实际常规考虑,选择B1;因素C和D的影响,根据线宽考虑,选择C2和D2。最优水平组合为A2B1C2D2,即显影速度为3.2 m/min,显影上压力为1.4 kg/m2,下压力为1.3 kg/m2,蚀刻速度为4.5 m/min,蚀刻上压力为1.6 kg/m2,下压力为1.5 kg/m2。

5 结论

本试验严格控制制作精细线路的各因素,采用硫酸双氧水体系将电解铜箔减铜至3.5 µm以及LDI曝光机来保证精细线路制作中的前期要求。特别是在显影、蚀刻线上,通过L9(34)正交试验的设计,对显影速度、显影压力、蚀刻速度、蚀刻压力四个因素进行工艺优化,并通过线宽均匀性和蚀刻因子分析了试验结果的可行性,确定了制作30 µm精细线路的最佳条件。

通过采用半加成法,结合图形电镀与快速蚀刻工艺,极大地减小了常规的减成法工艺过度蚀刻的现象。

[1]张怀武, 何为等. 现代印制电路原理与工艺[M].北京:机械工业出版, 2010.

[2]Joseph Fjelstad, Flexible Circuit Technology[M].BR Publishing, 2006.

[3]胡友作, 薛卫东等. 用正交试验法优化挠性单面板精细线路的工艺[J]. 印制电路信息, 2012, 01:49-52.

[4]崔浩. 手机用COF制造工艺关键技术研究[C]. 电子科技大学硕士学位论文. 2008,5.

[5]何为. 优化试验设计法及其在化学中的运用[M].电子科技大学出版社, 2004.

[6]田玲, 李志东. 浅谈蚀刻因子的计算方法[J]. 印制电路信息, 2007:55-56.

Semi-additive processing for 30μm fine lines and its process optimization

JIANG Jun-feng HE Wei FENG Li CHEN Shi-jin ZHOU Hua

The company has a processing capacity for 70μm/70μm lines, by using semi-additive processing we had explored how to produce the flexible double-sided 30μm fine lines. By designing a L9(34) orthogonal table test, we had a four factors process optimization on developing speed, developing pressure, etching speed and etching pressure to determine the optimum production conditions for 30μm fine lines. According to the result, developing speed is the main factors.

Semi-Additive Processing; Fine Lines; Orthogonal Test; Process Optimization

TN41

A

1009-0096(2014)03-0036-04

江俊锋,电子科技大学微电子与固体电子学院在读研究生,主要研究方向为挠性印制板新技术。