基于MPC8280的PCI驱动设计

2014-04-24王敏

王 敏

(广州海格通信集团股份有限公司网通分公司,广东广州 510663)

近年来,多媒体通信技术应用迅猛发展,对网速的要求也迅速提升。为适应这一趋势,与网络相关的终端设备和路由交换设备的性能均亟需提升[1]。在当今中国,计算机作为网络终端设备,网口的标配速率已由100 Mbit·s-1改为1000 Mbit·s-1,交换机、路由器等作为路由交换设备,交换容量量级也由原来100 Mbit·s-1上升到 1000 Mbit·s-1甚至 10 Gbit·s-1[2]。MPC8280是由Freescale公司推出的双地址总线双处理器芯片,自其推出以来,因其丰富的外围接口[3]已在航空航天、通信电子、医疗器械、交通设施等领域得到广泛应用,然而在今日迫切需求的大容量路由交换领域,却因其最高主频为450 MHz的限制,依靠运行在MPC8280上的软件扣除中断处理、系统管理等开销外,实现的交换容量仅为40 Mbit·s-1,在多路千兆交换应用中存在性能瓶颈。利用MPC8280的PCI口外接千兆交换芯片BCM56514,使得运行在MPC8280上的软件仅作路由计算和路由表的维护,而将交换控制交由BCM56514实现,可突破性能瓶颈。完成PCI驱动设计是这一方法能得以实施的先决条件,MPC8280通过PCI内存空间读写操作、配置空间读写操作和I/O空间读写操作,实现对交换芯片的配置、控制及路由表的更新,从而使MPC8280在大容量路由交换领域得到成熟应用。

1 PCI知识介绍

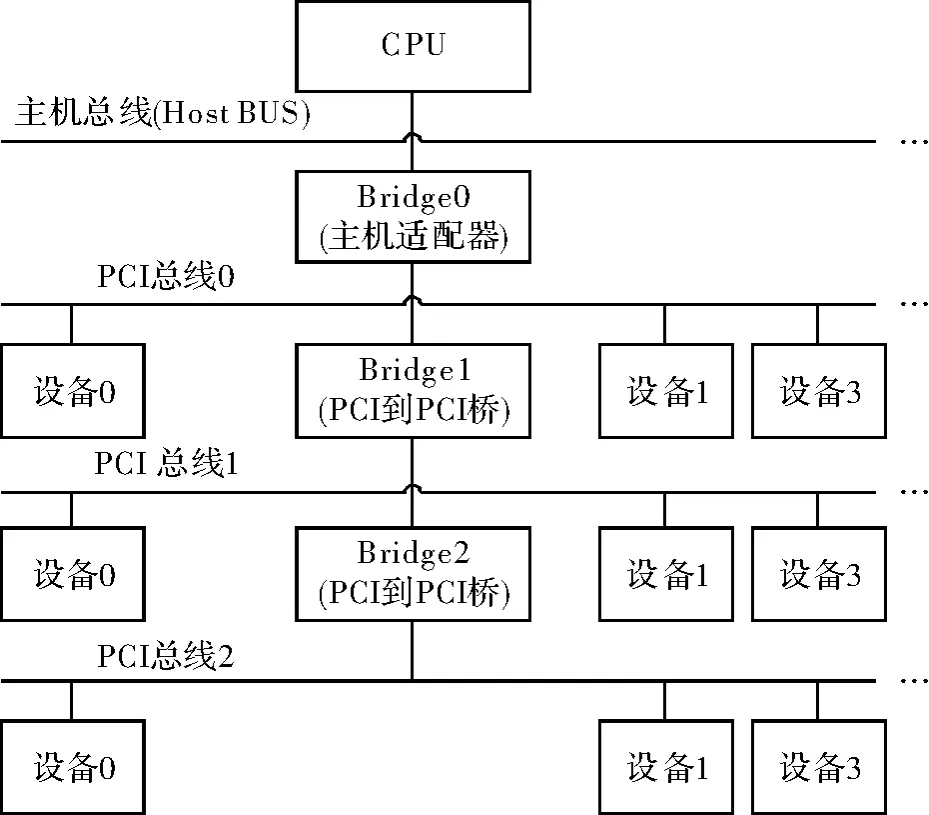

PCI为Peripheral Component Interconnect的缩写,是一种总线规范,用于外围设备互联。目前使用2.2版本的PCI规范。主要由时钟信号(PCI_CLK)、控制信 号 (FRAME、IRDY、DEVSEL、TRADY、STOP、IDSEL)、地址数据复用信号AD[31:0]及校验和错误指示信号(SERR、PERR)构成。地址和数据信号可扩展到64 bit,时钟信号常用33 MHz,可扩展到66 MHz,速率可达528 MByte/s[4]。采用分段分层结构,其总线拓扑结构如图1所示。

图1 PCI总线拓扑

2 PCI驱动设计

PCI驱动通过配置寄存器,完成总线初始化,并提供PCI配置空间读写、PCI内存空间读写、PCI I/O空间读写和中断函数接口[5]。上层应用利用这些操作接口发现外部交换芯片,并能获取交换芯片信息[6],实现对外接交换芯片的配置管理、路由表更新、状态回读等操作,最终实现PCI驱动设计。

2.1 PCI驱动流程设计

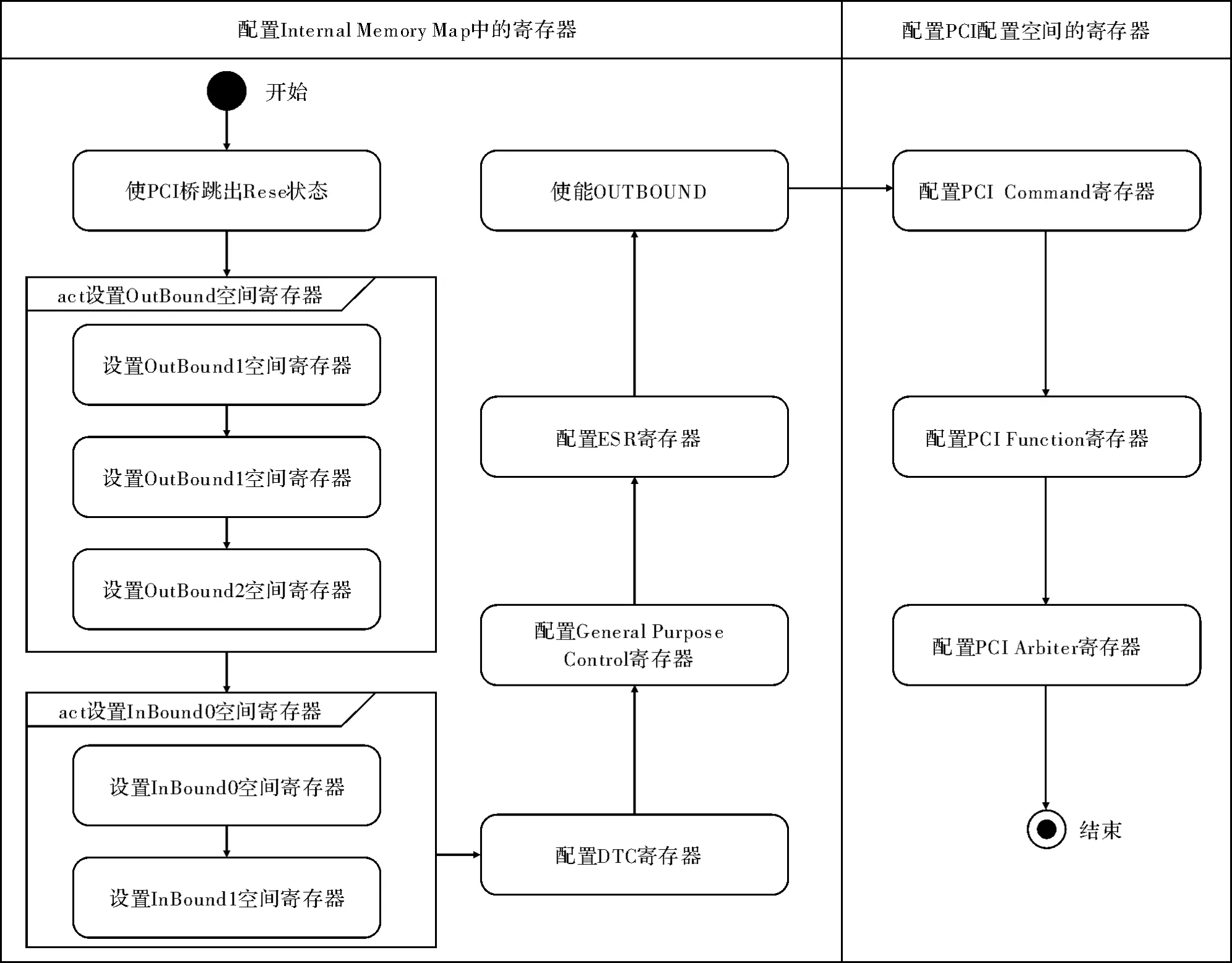

首先通过设置寄存器,使芯片跳出PCI重启状态,接着根据系统的地址分配对Outbound和Inbound寄存器组进行配置,然后对PCI使用的字节序、错误状态和Master模式进行配置,最后使能PCI内存空间读写和配置空间读写。使用UML的活动图对PCI驱动流程设计建模如图2所示。

图2 PCI驱动初始化流程

2.2 配置空间读写设计

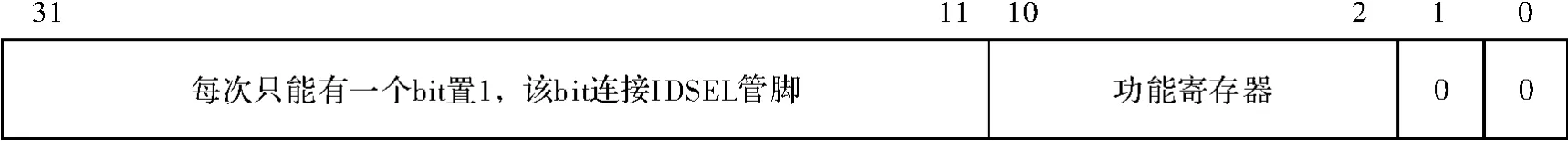

指令按照一定的数据格式优先写到CONFIG_ADDR寄存器,然后通过向CONFIG_DATA寄存器填入数据,完成写操作,或从CONFIG_DATA读出数据,完成读操作。无论CONFIG_ADDR寄存器的数据是否需要改变,每次操作都必须先对CONFIG_ADDR寄存器操作,然后才可对CONFIG_DATA寄存器操作,否则操作无效[7]。指令数据格式如图3所示。

图3 配置空间读写指令格式

配置空间操作时,地址译码过程如下:例如Device Number为0b01011时,对应的十进制数为11,则 Bit[31∶11]中的 Bit11 置 1,其他 Bit为 0,此时在硬件上将IDSEL信号连接到Bit11的PCI设备将被选中;若Device Number为0b01100时,对应的十进制数为12,则 Bit[31∶11]中的 Bit12 置 1,其他 Bit为 0,此时在硬件上将IDSEL信号连接到Bit12的PCI设备将被选中;Device Number的特殊定义如下:0b01010将选定Bit[31];0b11111将执行特别操作;0b00000将对 PCI桥自身进行操作。译码结果的格式如图4所示。

图4 Type0操作译码结果格式

共有两种操作类型:Type 0操作和Type1操作。Type 0操作适用于目标设备和PCI桥在同一总线上,PCI桥直接根据从上层总线接收到指令中的Device Number进行地址译码,并将 Bit[31∶11]数据中对应的Bit置1,Bit[1∶0]设置成 0x00,在 PCI总线配置操作的地址时段,将译码结果发送到PCI总线的AD[31∶0]上。

Type1操作适用于目标设备和PCI桥不在同一总线上,需经过PCI桥将完整的数据继续向下传递。当PCI桥在配置空间操作的地址时隙从AD[31∶0]收到指令时,判断目标设备是否在其负责的范围内,若不在,将不处理。若在,则将AD[31∶0]的数据和PCI_C/_BE完整的向下传递;若发现目标设备为本层设备,将操作变为Type0操作,选中目标设备。

2.3 内存空间读写设计

MPC8280的 PCI内存读写分为MPC8280主动发起的PCI内存空间读写和MPC8280被动引起的PCI内存空间读写。在进行PCI内存空间读写时,需地址译码[8]。

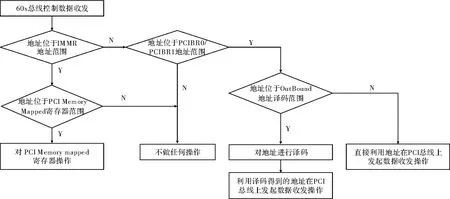

MPC8280主动发起的 PCI内存空间读写,MPC8280侧地址译码流程如图5所示。先对操作地址进行判断,若落在MPC8280的内部存储器映射寄存器(IMMR)范围内,接着就需判断是否落在PCI寄存器,根据判断结果决定是否对PCI寄存器进行操作或不做处理。若不是落在MPC8280的IMMR范围,需判读是否落在PCI OutBound空间,若落于PCI OutBound空间,则需根据寄存器的配置,对地址进行译码,并将译码后的结果在地址时隙被发送到PCI总线的地址管脚,若未落在PCI OutBound空间,却落于 PCIBR0或PCIBR1寄存器定义的范围内,则将地址直接通过地址时隙发送至PCI总线的地址管脚[3]。

图5 MPC8280主动发起的PCI内存空间读写的地址译码流程

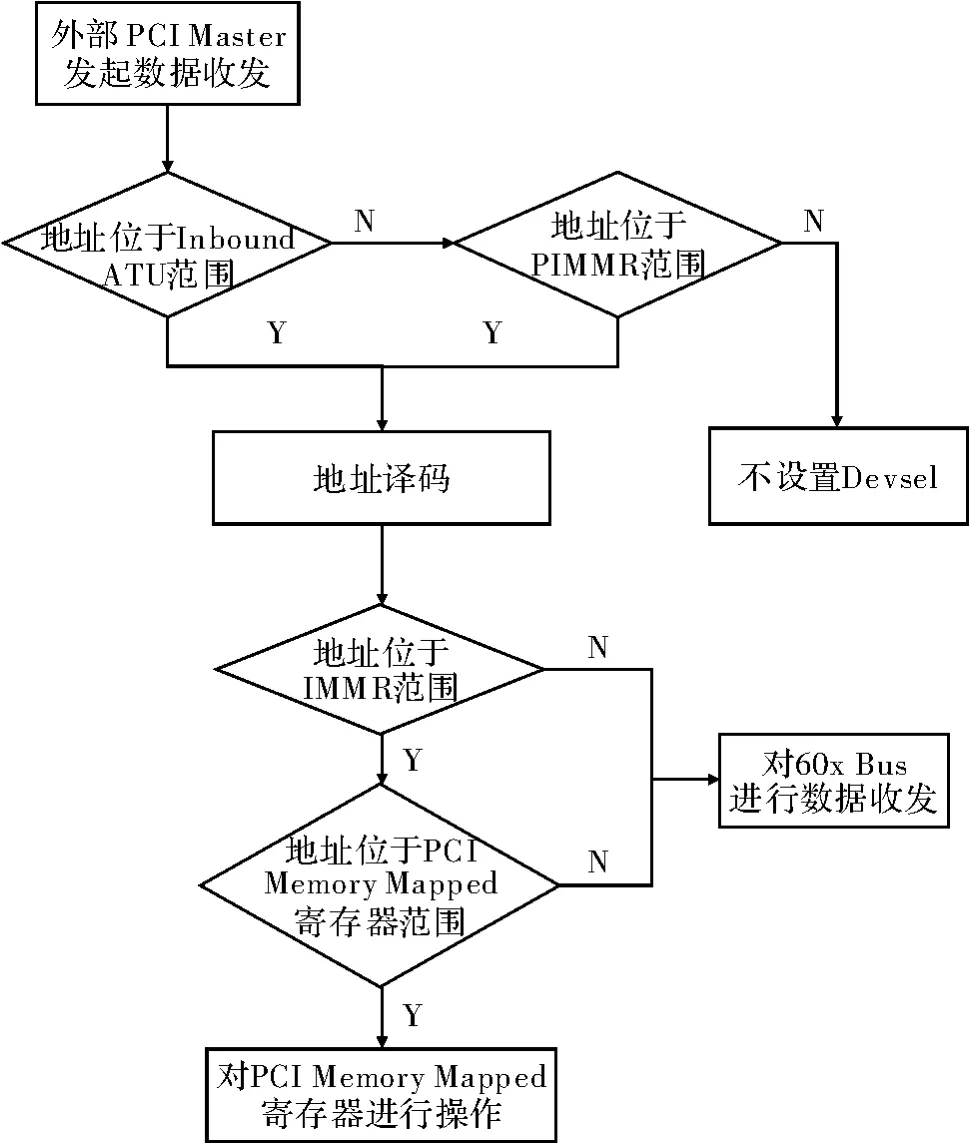

MPC8280被动引起的PCI内存空间读写,即由外部PCI主机(PCI Master)通过 PCI对 MPC8280发起PCI内存空间读写,MPC8280侧地址译码流程如图6所示。MPC8280在收到外部发起的PCI数据传输时,会判断PCI总线上的地址是否落在寄存器定义的PCI Inbound空间或是落于PIMMR空间。若是,就根据寄存器配置,对外部PCI总线上的地址进行译码,然后判断译码后的地址是否落在PCI内存空间,若落于PCI内存空间,则进行数据操作,并设置Devsel信号,否则将进行 60x 总线操作[3,9-10]。

图6 MPC8280被动引起的PCI内存空间读写的地址译码流程

2.4 I/O空间读写设计

PCI的I/O空间读写流程可参见内存空间读写流程[9],其与内存空间读写的不同在于:在配置时,对应的InBound空间和OutBound空间配置为I/O空间,AD[31∶0]中所有 bit为其提供一个完整的地址,AD[1∶0]用来产生Devsel信号和本次传输中最低有效的字节数;而内存空间地址译码只使用AD[31∶2],这说明内存空间操作时,每次操作传送4 Byte数据,操作后地址将递增4,以备进行后续传送。

3 结束语

PCI初始化配置完毕后,CPU通过线程调用PCI配置空间读写函数对外部的交换芯片进行轮询探测,正确获取了BCM56514的设备ID为B514[10],成功发现BCM56514芯片,进而对BCM56514进行了配置和管理,并通过调用PCI内存空间读写函数和I/O空间读写函数对BCM56514的内存空间和I/O空间进行了读写测试,实现了与BCM56514的数据信息交互,为实现MPC8280在大容量路由交换领域得到成熟应用提供了接口驱动支持。

[1] 刘尚麟.千兆以太网交换机软件系统的设计与实现[D].成都:西南交通大学,2004.

[2] 聂琼.千兆自适应以太网交换机的设计[D].苏州:苏州大学,2010.

[3] Freescale Semiconductor.MPC8280 PowerQUICC II family reference manual[M].Chandler:Freescale Semiconductor,2005.

[4] PCI Special Interest Group.PCI local bus specification revision 2.2[S].Hillsboro:PCI Special Interest Group,1998.

[5] 刘慧英,王军,夏天琪.基于PCI总线的视频采集卡及其WDM驱动程序设计[J].计算机测量与控制,2010,18(5):1182-1185.

[6] 杨德芳.PCI驱动程序的设计[J].电脑编程技巧与维护,2007(4):75 -77,87.

[7] 熊信璇.基于PCI总线的立体显示技术研究[D].武汉:华中师范大学,2011.

[8] 宋新超,柴恒.基于WinDriver的数字信号处理器PCI驱动开发[J].舰船电子对抗,2012,35(4):82 -85.

[9] 何文涛.基于PCI总线数据采集系统的研究与设计[D].大连:大连理工大学,2011.

[10] Broadcom Corporation.BCM56514 data sheet[M].Irvine:Broadcom Corporation,2007.