基于FPGA的三通道函数信号发生器

2014-04-24胡善伟

胡善伟

(中航工业西安航空计算技术研究所第13研究室,陕西西安 710119)

1 方案概述

该函数信号发生器能提供正弦波、锯齿波、PWM信号等输出,显示方面同时具有电压、频率、相位差、波形种类、矩形波占空比等数据的参数显示。可步进调整相位差、占空比、频率等参数[1]。

技术指标:(1)正弦波、三角波、锯齿波三相输出,频率可调范围1 Hz~30 kHz,频率步进1 Hz,并具有频率设置功能。(2)任两相间的相位差在0°~359°范围内可任意预置,相位差步进1°。(3)输出电压幅度:电压峰-峰值Vopp≥10 V。(4)数字显示电压、频率、相位差、波形种类和矩形波占空比等,电压有效值精度5%,频率精度0.1%。(5)在1 Hz~30 kHz频率范围内,增加矩形波输出信号,频率可任意预置,频率步进1 Hz,频率精度0.1%;矩形波信号的占空比可以预置,占空比步进 1/100,当占空比为 1/4时,误差≤±2/100。

2 系统实现原理

2.1 整体系统设计

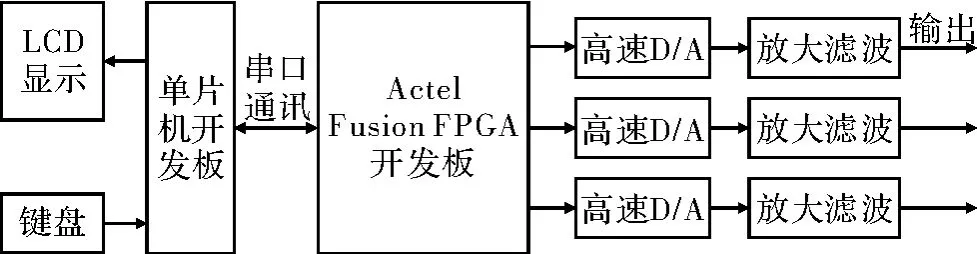

键盘输入信息给单片机,控制LCD屏幕显示相关参数,并通过串行口发送数据给FPGA,通过FPGA处理数据,将数字信号传送给高速D/A,最后通过放大滤波输出波形[2]。图1为信号发生总体框图。

图1 信号发生器总体框图

2.2 信号发生器各模块设计

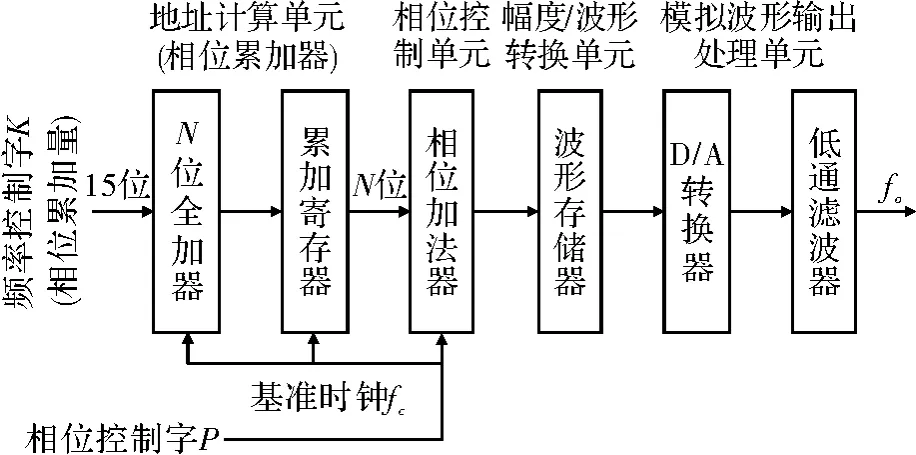

图2为DDS的总体结构[3]。

图2 DDS结构框图

在CLK的作用下,如果依次按顺序读取ROM中的数据,即从第一个数不遗漏的读到最后一个数据,设其输出的正弦信号为f01;如果每隔一个地址读一次数据,其输出信号的频率为f02,这样f02将比f01提高1倍,即 f02=2f01;依此类推[4]。

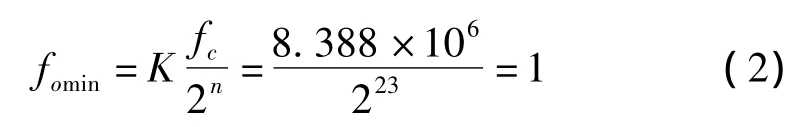

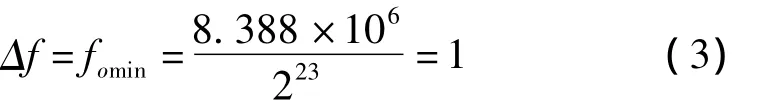

相位累加器可由N位加法器与N位寄存器级联构成。然后在输入时钟fc的控制下,对输入数据K进行累加。式(1)中,当K为1时,DDS输出最低频率fc/2n。DDS的最高频率受限于时钟频率fc和采样定理,即 fomax<fc/2。设计中,N=23,fc=8.388 MHz,则频率最大值为

频率最小值为

频率步进值为

输出信号的频率范围可调。

固定相位偏置加法器,由于波形存储器的输入为相位累加器的输出与P之和,所以,通过改变相位控制字P即可控制输出信号的相位偏移。其相位偏移量为2n。设计中,相位加法器的字长N为10,若取3个固定偏置相位分别为 P1=0,P2=120°/360°×1024=341,P3=240°/360°×1024=683,则可生成相位差为 120°的3条正弦信号的相位编码。这样,便可通过同一时钟fc控制3个通道的地址,从而使编码的输出同步。

波形存储器主要完成信号相位序列到幅度序列的转换[5]。N位的寻址ROM相当于把波形数据离散成具有2N个样值的序列。若波形ROM有D位数据位,则2N个取样值的幅值将以D位二进制数值固化在ROM中。按照设计算法,波形储存器ROM的位数应与相位累加器的位数相同,即同为23位,但是23位的数据量过大,并且没有对应的D/A。所以这里使用10位的ROM,共1024个数据,截取累加器的高10位对ROM进行寻址,输出对应的数值。

10位的高速DAC将FPGA输出的数字信号变为差动模拟信号,提供给输出端的高增益差动放大器,使信号的峰峰值达到设计要求,最终输出波形信号。

3 软件设计

本设计宏观上分为5个模块,即前端模块:串口收发模块;中间模块:DDS模块;后端模块:分时发送模块。另外还有两个锁相环PLL48M,PLL8.388M,来提供系统时钟[6]。

3.1 前端模块

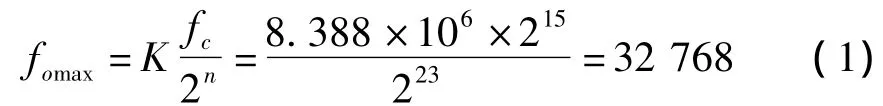

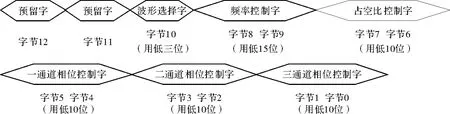

通过自定协议,实现了FPGA和单片机的串口通讯[7-8]。如图 3 所示。

图3 单片机与FPGA通讯协议

3.2 中间模块

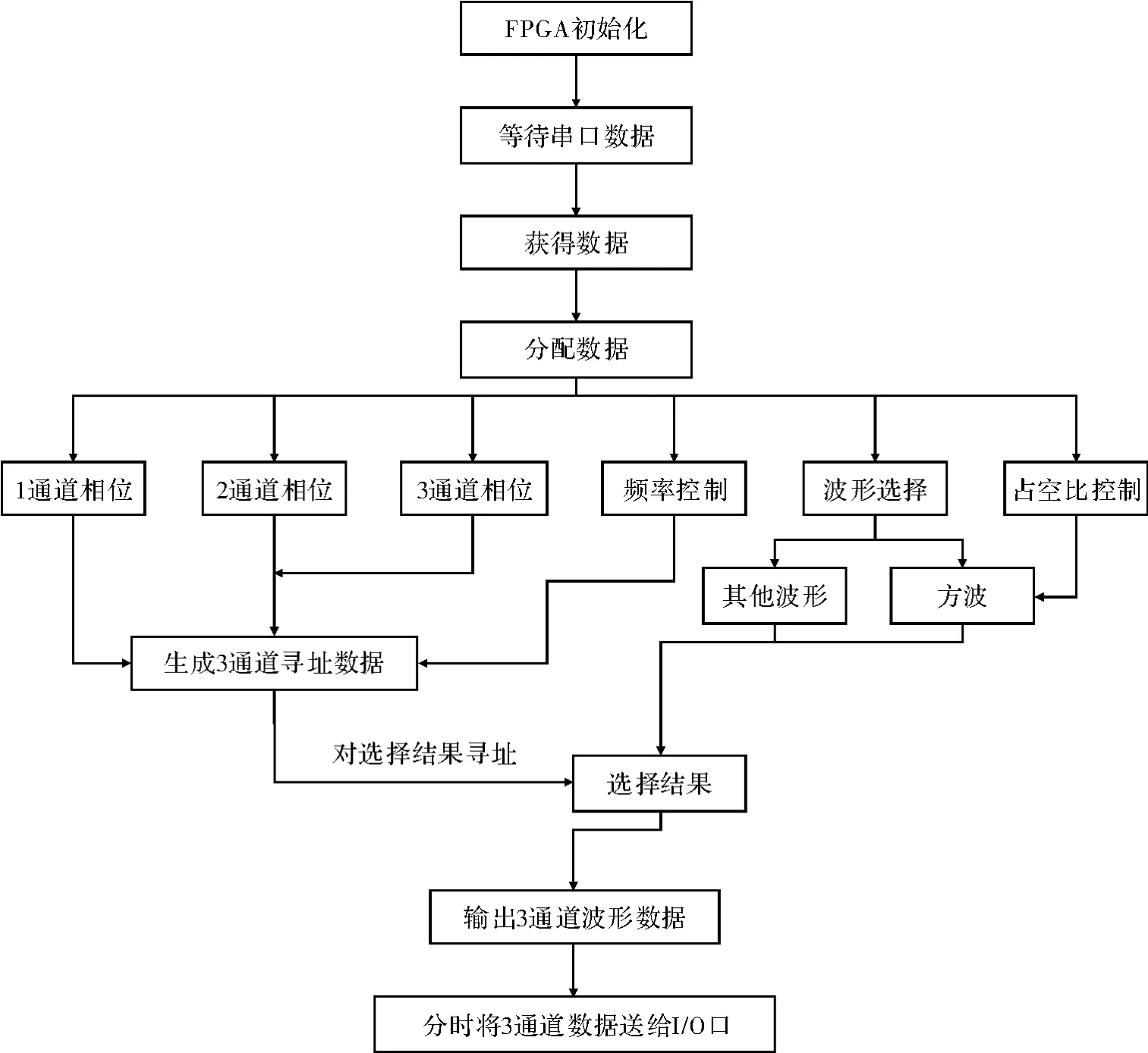

中间模块即DDS模块包含了两个子模块,分别是累加器(ACC)模块,波形选择模块(Select)。

累加器模块(ACC)中设置有3个23位的累加寄存器,复位后,先将3个通道的相位控制字P分别赋值给对应的累加寄存器的高10位。使用8.388 MHz的系统时钟,在时钟每出现一个上升沿时,累加寄存器从赋值过后的值开始对频率控制字K开始累加,并输出其高10位的数据对各个波形ROM进行寻址。

波形选择模块(Select)中实例化了4种波形,即正弦波、矩形波、三角波、锯齿波的ROM表,根据波形选择控制字,选出用户所要求的波形。00为正弦波,01为矩形波,10为三角波,11为锯齿波。在累加器高10位的寻址下,找到当前时刻点的波形幅值,进行输出。其中,矩形波需要有占空比的调整,根据前端模块中的占空比控制字,将累加器模块输出的寻址数据与其比较,若累加器输出的寻址数据小于占空比控制字,则输出1,如大于则输出0,这样就可以根据用户的设定输出占空比了。

3.3 后端模块

后端模块即分时发送模块,由于FPGA的管脚有限,如果三通道都并行输出,那将至少占用30个FPGA的I/O口,为避免此类情况发生,在FPGA内部编辑了此模块,其可分时将三通道输出的信号幅值赋值给FPGA的I/O口,在每个通道的幅值输出时,使能相应的锁存器,当三通道的锁存器更新好数据时,一起使能D/A,这样就同时输出了三通道的数据。流程如图4所示。

图4 FPGA算法流程图

4 系统测试及仿真

4.1 正弦波测试与仿真

该模块输入信号由时钟(clk)和复位信号(reset)构成,当信号发生器选择信号(sel[2..0])为4时,该模块输出端(q[7..0])对外输出。模块振幅随时钟的变化阶梯性递增,输出波形参数可以通过程序进行设定。仿真波形如图5所示。

图5 正弦波仿真测试

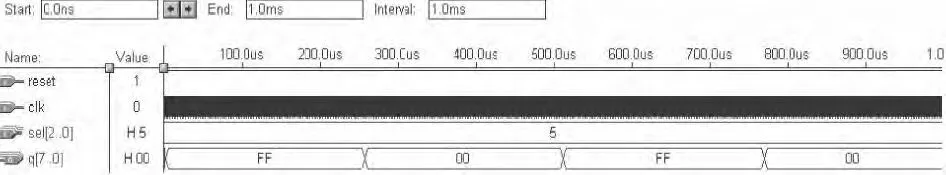

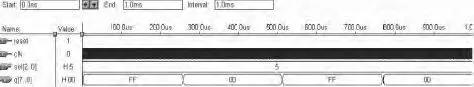

4.2 PWM测试与仿真

该模块输入信号由时钟(clk)和复位信号(r eset)构成,当信号发生器选择信号(sel[2..0])为5时,该模块输出端(q[7..0])对外输出。模块振幅随时钟的变化持续变为高电平或低电平,输出波形参数可以通过程序进行设定,仿真波形如图6所示。

图6 PWM仿真测试

4.3 三角波测试与仿真

模块输入信号由时钟(clk)和复位信号(reset)构成,当信号发生器选择信号(el[2..0])为2时,该模块输出端(q[7..0])对外输出。模块内计数器随时钟先递增后递减,波形随之先递增后递减,输出波形参数可以通过程序进行设定,仿真波形如图7所示。

图7 三角波仿真测试

4.4 锯齿波测试与仿真

该模块输入信号由时钟(clk)和复位信号(r eset)构成,当信号发生器选择信号(sel[2..0])为5时,该模块输出端(q[7..0])对外输出。模块振幅随时钟的变化持续变为高电平或低电平,输出波形参数可以通过程序进行设定,仿真波形如图8所示。

图8 锯齿波仿真测试

5 结束语

本设计能够满足3通道的设计要求,并且留有较宽的频率上限以及通道数余地,稍加改动便可大幅增加频率上线和通道数,完成更多功能。实验证明,此设计方案波形失真度小,频率、相位步进准确,可以满足工业需要。

[1] 曹远宏.Verilog HDL高级数字设计[D].武汉:武汉理工大学,2005.

[2] 王飞.基于 FPDA的三相正弦信号发生器设计[D].西安:西北工业大学,2008.

[3] 高吉祥,唐朝京.数字系统与自动控制系统设计[M].北京:电子工业出版社,2007.

[4] 毛谦敏.单片机原理及应用系统设计[M].北京:国防工业出版社,2008.

[5] 裴少俊,胥嘉佳,黄克平.一种基于AD9854的BPSK信号产生设计[J].电子科技,2013,26(1):74 -76.

[6] 王伟.Verilog HDL程序设计与应用[M].北京:人民邮电出版社,2005.

[7] 袁俊泉,孙敏琪,曹瑞.Verilog HDL数字系统设计及其应用[M].西安:西安电子科技大学出版社2002.

[8] 宋仲康,孔利东.基于VHDL语言的信号发生器的设计与实现[J].工业控制技术,2006(8):80-83.