IEEE1588在加速器实时控制系统中的应用研究

2014-03-22马明超陈建锋沈立人蒋舸扬

马明超 陈建锋 沈立人 蒋舸扬

1(中国科学院上海应用物理研究所 嘉定园区 上海 201800)

2(中国科学院大学 北京 100049)

在上海光源装置、质子治疗装置等大型加速器系统的控制中,存在有多个控制器的分布式系统架构下实现高速实时控制的需求,如上海光源的真空快泄漏联锁保护系统,其时间响应需求为1 ms。分布式实时控制系统通常需要特殊的硬件和通讯系统结构。本文所研究的时间同步,其目的是实现在常规网络系统架构上构建分布式实时控制系统。网络系统本身不是一个实时控制系统,其响应时间和时间精确度无法保证,必须采用时间同步措施保证其实时性。根据系统规模和响应时间需求计算,基于网络构建上述快联锁保护系统的时间同步需求为±200 ns。

目前时间同步协议有网络时间协议(Network Time Protocol, NTP)[1]、简单网络时间协议(Simple Network Time Protocol, SNTP)[2]和 IEEE1588精准时间协议[3]。NTP和SNTP可以实现毫秒级别的时间同步,而IEEE1588可以实现亚微秒级别的时间同步。IEEEl588定义了一个能够在测量和控制系统中实现高精度时钟同步的协议——精准时间协议(Precision Time Protocol, PTP)。PTP能够使异质系统中各类不同精确度、分辨率和稳定性的时钟同步起来,利用最小的网络和本地计算资源,使系统达到亚微秒级别的同步精度[3]。

本文采用 FPGA和千兆以太网来实现IEEE1588时间同步,充分利用VHDL硬件描述语言的并行处理,可以有效地提高时间同步的精度。针对普通晶振的频率偏差造成IEEE1588同步精度低的问题,本文提出了一种频率动态补偿的算法,使加速器实时控制系统能够实现更高的时间同步精度,并且在以上海光源控制系统采用的 FORCE10交换机所构成的网络系统中构建与测试时间同步试验系统,得到比较满意的结果。

1 IEEE1588精准时间同步原理

IEEE1588精准时间同步协议的原理是主站通过PTP报文与从站周期性地交换时间数据实现主从同步。IEEE1588主要通过 Sync、Follow_Up、Delay_Req和Delay_Resp进行主从同步,本文采用IEEE1588协议的两步模式进行主从同步,IEEE1588主从同步的工作过程如图1所示[3]。

图1 IEEE1588 主从同步过程图Fig.1 IEEE1588 master-slave synchronous process diagram.

在图1中,t1为主站发送Sync报文的时间,t2为从站收到 Sync报文的时间,t3为从站发送Delay_Req报文的时间,t4为主站收到 Delay_Req报文的时间。令 Toffset为从站与主站的时钟偏移,TdelayMS为主站到从站的报文延迟,TdelaySM为从站到主站的报文延迟,假如报文的传输路径对称(TdelayMS=TdelaySM),则

根据式(1)、式(2),可以计算出从站与主站的时钟偏移和报文的传输延迟,从而校准从站的时钟,实现从站和主站之间的时间同步。

2 硬件平台

为了实现最优的时间同步精度,目前用于时间同步的交换机大多数采用专用的IEEE1588交换机,但由于上海光源使用的交换机是FORCE10交换机,为了减少工程上的投资和对原有系统的改动,设计中采用FORCE10交换机,该交换机是常规交换机。在千兆以太网通信环境下,测试得到的 FORCE10交换机的延迟是3.432 μs,FORCE10交换机的延迟抖动是56 ns。

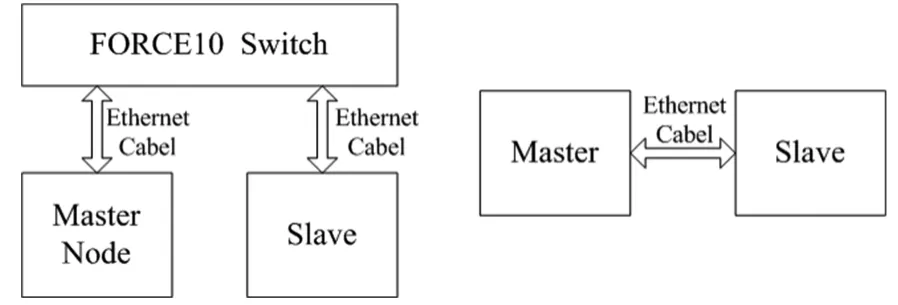

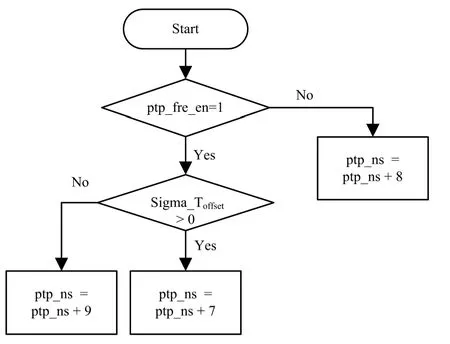

本文研究的是一个主站和一个从站的时间同步。时间同步采用两种硬件连接:主站和从站通过FORCE10交换机连接,以及主站和从站通过网线直接连接。时间同步硬件连接框图如图2所示。

图2 时间同步硬件连接框图Fig.2 Time synchronization hardware connection diagram.

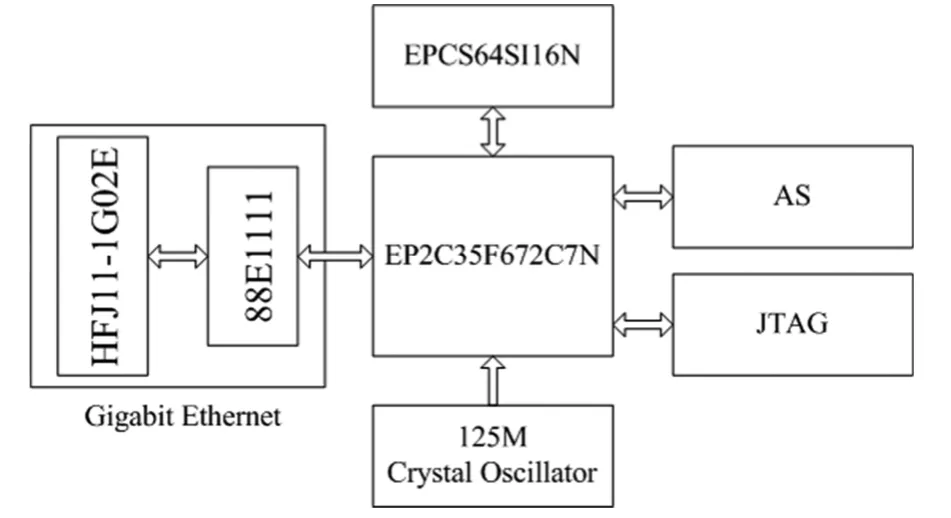

由图 2,左边代表的时间同步硬件连接是主站和从站通过FORCE10交换机连接,右边代表的时间同步硬件连接是主站和从站通过网线直接连接。主站和从站采用硬件配置相同的PTP电路板,但是FPGA内部程序不同。PTP电路板的硬件框图如图3所示。

从图3可见,PTP电路板采用Altera公司的型号为EP2C35F672C7N的FPGA。利用该FPGA芯片进行以太网数据的收发、IEEE1588协议的开发以及频率动态补偿算法的设计和验证。设计采用125M晶振给FPGA提供全局时钟信号CLK,PTP电路板的以太网数据传输部分采用88E1111千兆以太网芯片和集成网络变压器的 RJ45接口HFJ11-1G02E。采用JTAG (Joint Test Action Group)接口进行FPGA的调试,通过JTAG和 Quartus II软件中的In-System Memory Content Editor工具可以观测到FPGA片内RAM中采集到的数据并将这些数据通过JTAG存储到电脑上,这种数据存储方式为后期的MATLAB数据处理,提供了很大便利。程序加载部分采用EPCS64SI16N配置芯片,用于加电时将程序从配置芯片中加载到FPGA中;程序烧录部分采用FPGA将代码通过AS接口烧录到配置芯片中;测试部分使用SMA连接示波器,进行时间同步的测试。

图3 PTP电路板硬件框图Fig.3 Hardware diagram of PTP circuit.

3 频率动态补偿算法

判断主站和从站同步有两条标准[4]:一是从站的本地时钟是否和主站的本地时钟相同;二是从站的本地时钟递增速度是否与主站相同。假定通信链路中不存在延迟抖动,从站和主站的时钟偏移计算得非常准确,每次从站校正完本地时钟后使得从站和主站的时钟偏移为零。但由于主站和从站的晶振频率并不完全相同,两个标称频率相同的晶振实际频率的微小偏差会导致从站和主站的时钟偏移随着时间的变化逐渐增大,所以仅仅周期性地校正从站的本地时钟无法实现精确的时间同步。PTP电路板采用的晶振是泰艺公司的125M晶振,该晶振的频率精度为50×10−6。假如主站和从站1 s对时一次,在 1 s时间内从站时钟和主站时钟的偏移最大为2×50×10−6s=100 μs,同步对时精度很差。并且晶振的频率跟电压和温度有关,随着电压和温度的变化,晶振的频率也会发生变化。若要调节从站的本地时钟递增速度与主站相同,文献[5]提出了三种方法:一是使用VCO调整从站时钟,但是这种硬件代价很大;二是通过软件算法调整,带有很大的随机性;三是使用加法器调整,这种方法在FPGA内部实现相对简单,频率动态补偿算法也是通过加法器调整来实现的。

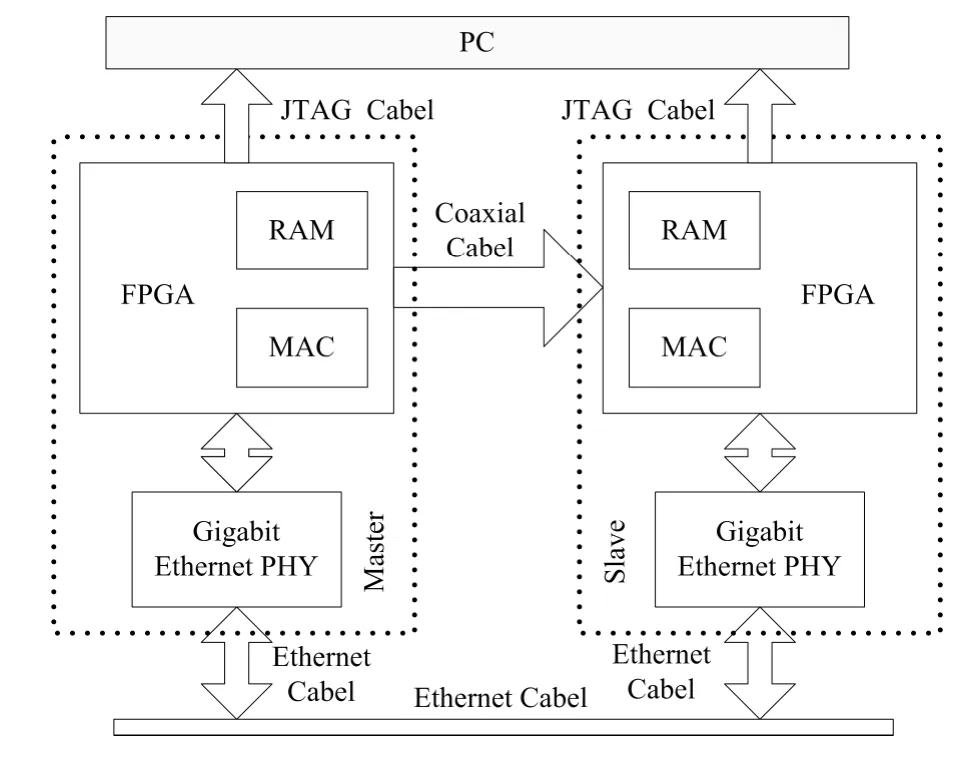

在FPGA中采用48位ptp_sec和32位ptp_ns存储本地的时钟信号,其中 ptp_sec代表本地时钟的秒值,ptp_ns代表本地时钟的纳秒值。当ptp_ns递增到109时,ptp_sec加1,ptp_ns值清零。PTP电路板采用125M晶振给FPGA提供全局时钟信号CLK,即Tclk=8 ns。FPGA利用CLK全局时钟信号驱动主站和从站本地时钟的递增。主站和从站的本地时钟框图如图4所示。

图4 主站(a)和从站(b)的本地时钟框图Fig.4 Diagram of local clock of the master (a) and the slave (b).

由图4(a),主站的本地时钟在125M全局时钟信号CLK的上升沿递增8 ns,即ptp_ns的值加8。图4(b)中,由于主站的本地时钟作为从站同步的参考,从站根据式(2)计算的主从偏移 Toffset,通过一定的调整控制,完成两个主要任务:一是根据每个同步周期计算的Toffset,调整从站的本地时钟,使从站的本地时钟与主站相同;二是根据每个同步周期计算的Toffset,调整从站的本地时钟在125M全局时钟信号CLK的上升沿递增7 ns和8 ns的比例(从钟快于主钟)或8 ns和9 ns的比例(从钟慢于主钟),使从站的本地时钟递增速度与主站相同。

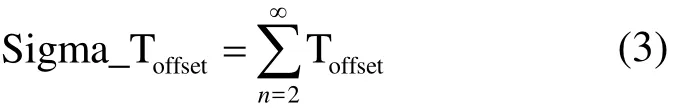

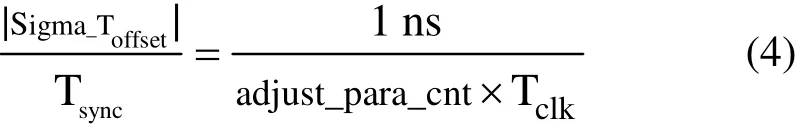

如果通信链路存在延迟抖动,根据式(1)、式(2)计算出来的结果就有一定的误差,本文提出的频率动态补偿算法是在没有延迟抖动的前提下总结出来的,也就是假定每次主从同步校正完从站的本地时钟后,从站和主站的时钟偏移为零。由于主站和从站的晶振存在频率偏差,使得从站和主站的时钟偏移随着时间的变化逐渐增大。为了实现从站和主站同频,需要把一个同步周期内由于晶振频率偏差造成的从站和主站的时钟偏移分布在一个同步周期内进行均匀地校正。假如最小时间单位为ns,若经过一个同步周期,晶振频率偏差造成从站快了X ns,需让从站时钟在该同步周期内均匀地调慢X ns,也就是每经过同步周期/X的时间,需将从站时钟调慢1 ns。频率动态补偿的公式如式(3)、式(4)所示。

式(3)、式(4)是经过多次程序验证过的频率动态补偿的经验公式。Toffset、Sigma_Toffset、Tsync、Tclk的单位都是ns,其中Tclk=8 ns。adjust_para_cnt是计数值,没有单位。

式(3)中,Sigma_Toffset是第二次主从偏移 Toffset以及频率动态补偿后的无穷个周期的 Toffset的累加和。当从站快于主站,Toffset大于0;当从站慢于主站,Toffset小于 0。第二次主从偏移 Toffset可以近似反映一个同步周期 Tsync内由于晶振频率偏差造成的从站和主站的时钟偏差,频率动态补偿后计算的Toffset相对第二次主从偏移 Toffset在数值上小很多,跟0很接近,且是动态变化的,频率动态补偿后计算的 Toffset可以动态地调整一个同步周期内由于晶振频率偏差造成的从站和主站的时钟偏差。多次实验测试,Sigma_Toffset能动态地反映一个同步周期Tsync内因晶振频率偏差造成从站和主站时钟偏差。

式(4)中,左边代表的含义是在一个同步周期Tsync内,由于晶振频率偏差造成的从站和主站的时钟偏移相对同步周期Tsync的比值。右边代表的含义是经过多久的时间,从站和主站的时钟偏移可以达到1 ns,通过调整这1个ns的时钟偏移实现从站的本地时钟递增速度与主站相同。频率动态补偿框图如图5所示。

图5 频率动态补偿算法流程图Fig.5 Flow chart of dynamic frequency compensation.

图5简要说明了频率动态补偿算法的流程,整个过程是通过多个状态机顺序执行的,并且频率动态补偿算法的流程跟下文描述的para_cnt计数器计数的流程和从站本地时钟递增的流程是并行的。在每个同步周期内,从站接收和发送进行主从同步的PTP报文,然后根据式(2)计算出从站和主站的时钟偏移Toffset,从站根据计算的Toffset调整从站的本地时钟;如果是第一次进行主从同步,就返回并等待下一次的PTP报文,如果不是第一次主从同步,就根据式(3)计算 Sigma_Toffset的值,并禁止 para_cnt计数器计数使能,即para_cnt_en=0;然后根据式(4)计算adjust_para_cnt的值,同时使能para_cnt计数器计数,即para_cnt_en=1。频率动态补偿算法计算出的 Sigma_Toffset和 adjust_para_cnt以及 para_cnt计数器计数使能信号(para_cnt_en)决定了 para_cnt计数器计数的流程和从站的本地时钟递增的流程,para_cnt计数器计数流程图和从站的本地时钟递增流程图如图6、图7所示。

图6 para_cnt计数器计数流程图Fig.6 Flow chart of para_cnt counter counting.

图7 从站本地时钟递增流程图Fig.7 Flow chart of increasing the local clock of the slave.

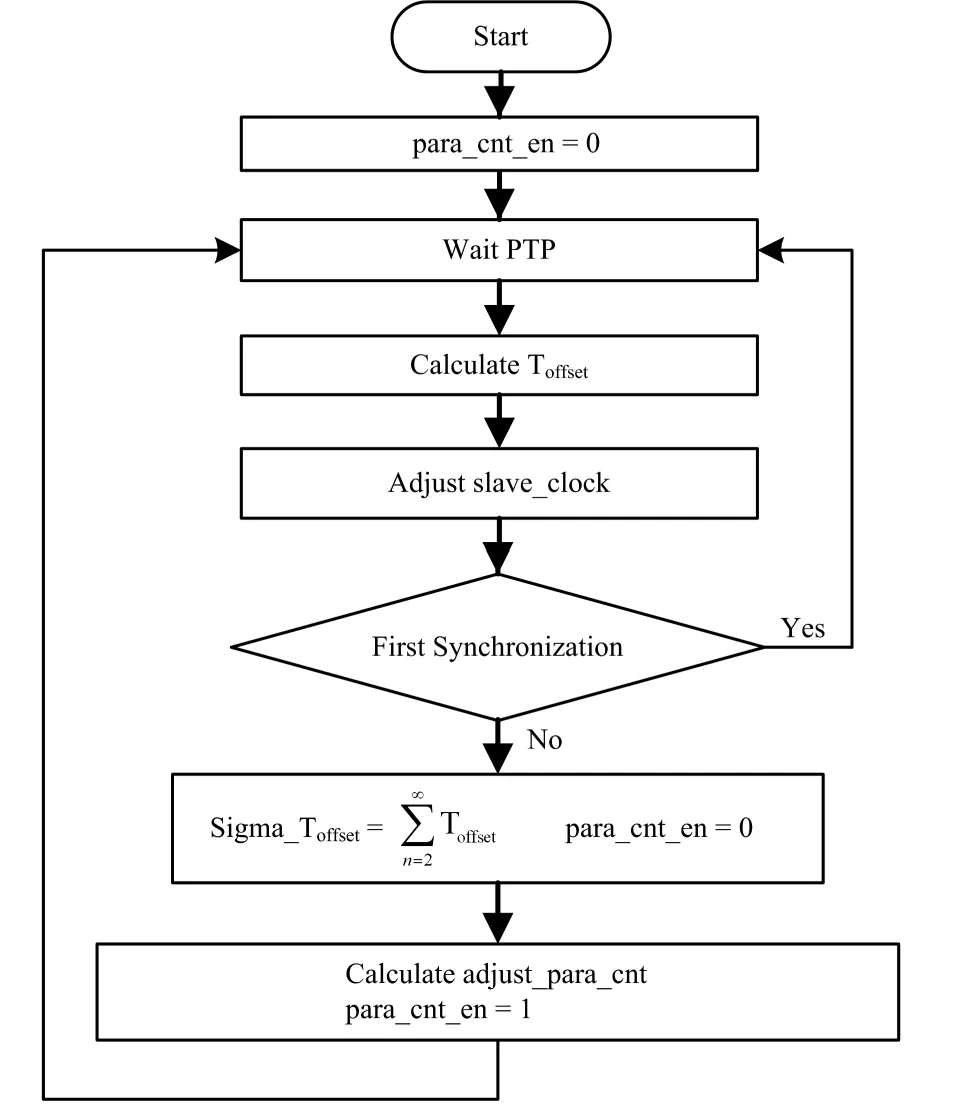

图6简要说明了para_cnt计数器计数的流程,该流程在一个全局时钟信号CLK内完成。当计数器para_cnt计数允许(para_cnt_en=1)并且para_cnt的值小于adjust_para_cnt的值,para_cnt计数器加1,同时禁止本地时钟调频(ptp_fre_en=0);当 par_cnt计数器计数禁止(para_cnt_en=0)时,计数器清零,同时禁止本地时钟调频(ptp_fre_en=0);当计数器para_cnt计数允许(para_cnt_en=1)并且para_cnt计数器的值等于adjust_par_cnt的值时,para_cnt计数器清零,同时允许本地时钟调频(ptp_fre_en=1)。

图7简要说明了从站的本地时钟递增的流程,该流程时在一个全局时钟信号CLK内完成。当本地钟调频禁止(ptp_fre_en=0)时,从站的本地时间递增8 ns,即 ptp_ns加 8;当本地时钟调频允许(ptp_fre_en=1)并且Sigma_Toffset的值大于0时,从站的本地时间递增7 ns,即ptp_ns加7;当本地时钟调频允许(ptp_fre_en=1)并且 Sigma_Toffset的值小于0时,从站的本地时间递增9 ns,即ptp_ns加9。

频率动态补偿算法在型号为EP2C35F672FC7N的FPGA中实现的,该FPGA总的逻辑资源有33216 LEs,设计中从站总共消耗了8370 LEs。该FPGA总的memory资源有483840 bits,设计中由于以太网数据接收存储和存取采集到的时间数据消耗的memory资源为76336 bits。

4 测试方案

本文给出了两种测试方案,方案一适合观察短时间的从站和主站的时钟偏移,用于说明频率动态补偿的效果;方案二适合观察长时间的从站和主站的时钟偏移,用于说明频率动态补偿后主从同步精度,以及分析同步周期和FORCE10交换机的延迟抖动对时间同步的影响。

4.1 测试方案一

测试方案一的原理是通过在 FPGA内部调用RAM核,将采集的时间数据存储到RAM中,然后利用 JTAG线和 Quartus II软件中的 In-System Memory Content Editor工具,将采集的时间数据存储到电脑上,利用MATLAB处理并画出相应的从站和主站的时钟偏移效果图。测试方案一框图如图8所示。

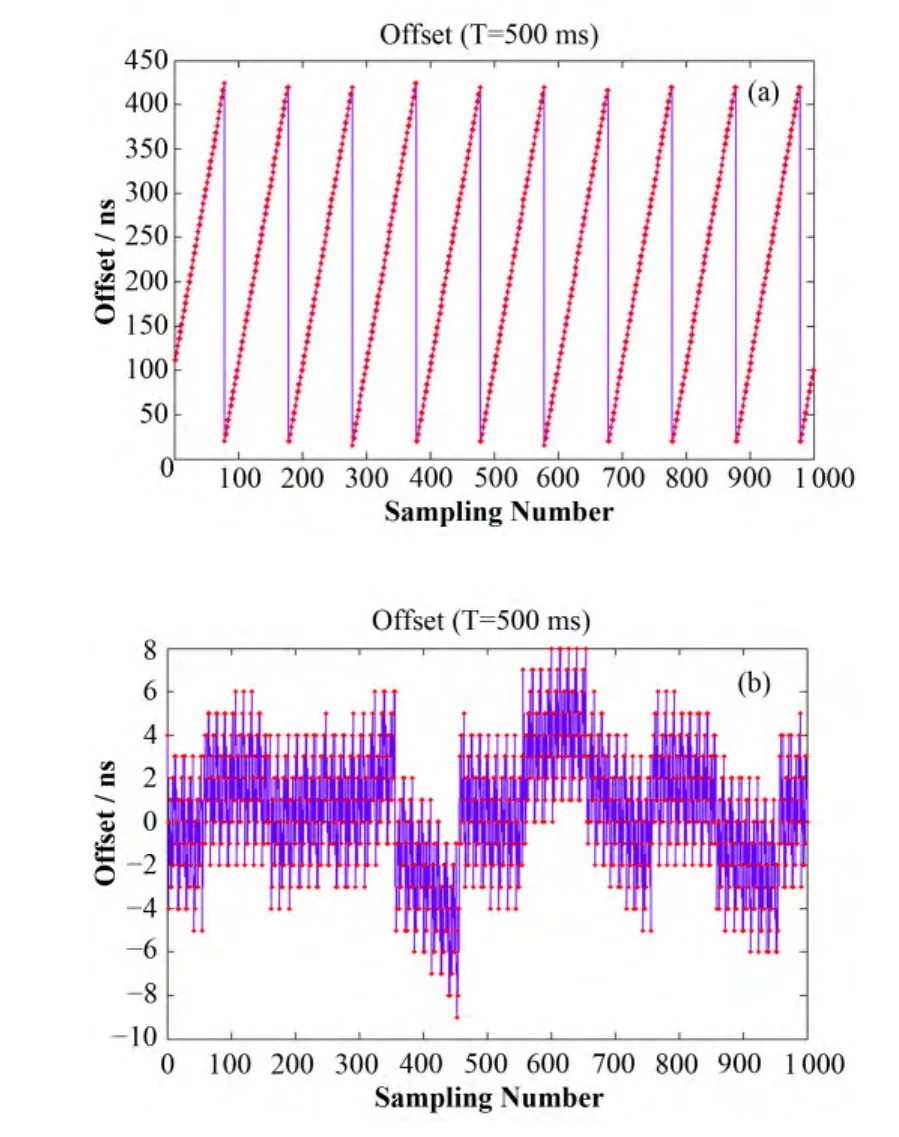

从图8中可以看出,主站和从站上的FPGA通过SMA和同轴电缆连接在一起。通过按下主站的按键,主站的 FPGA通过 SMA和同轴电缆发送1000个脉宽100 ns的脉冲给从站的FPGA,脉冲间隔5 ms。在每个脉冲的上升沿,主站和从站的FPGA将各自的时间数据存取到RAM中。在测试方案一中,千兆以太网直接通过网线连接;测试结果分别给出了未频率动态补偿和频率动态补偿后的主从偏移效果图,如图9所示。

图8 测试方案一框图Fig.8 Block diagram of test scenario one.

图9 未频率动态补偿(a)和频率动态补偿后(b)的主从偏移效果图Fig.9 Master-slave offset effect diagram without frequency and after frequency dynamic compensation (b). dynamic compensation (a)

图9(a)的主从同步精度是16−424 ns,图9(b)的主从同步精度是(−9 ns, 8 ns)。从同步效果来说,动态频率补偿算法很好地解决了普通晶振的频率偏差造成IEEE1588同步精度低的问题,但这种方法测试时间比较短,不能说明长时间的主从同步精度。

4.2 测试方案二

测试方案二是通过示波器的统计skew的功能,统计出主从偏移的最小值、最大值和标准方差。主从同步的精度介于主从偏移的最小值和最大值之间。测试方案二框图如图10所示。

图10 测试方案二框图Fig.10 Block diagram of test scenario two.

由图10,主站和从站的FPGA通过SMA和同轴电缆连接到Lecroy 104MXi示波器上,主站和从站在同一时刻分别发送脉脉宽为100 ns的脉冲给示波器,脉冲间隔为 4096 ns,通过示波器统计两个脉冲前沿对应的时间之差,即主从偏移。分别测试了同步周期为500 ms、1 s和2 s以及在特定同步周期下直接连接和FORCE10交换机连接的主从偏移,测试时间为8 h,频率动态补偿后的主从同步测试结果如表1所示。

表1 主从同步测试结果Table 1 Master-slave synchronous test results.

由表 1,在同样的同步周期下,直接连接的连接方式测得的主从同步精度更高。由于像交换机类似的网络设备存在延迟抖动,造成通信链路不对称,即TdelayMS ≠TdelaySM。当TdelayMS ≠TdelaySM时,利用式(2)计算的 Toffset就存在一定的误差,这个误差是由|TdelayMS−TdelaySM|决定的。针对通信链路的不对称性,IEEE1588 V2提出了透明时钟,硬件上需要采用专用的带透明时钟的IEEE1588交换机来消除网络设备带来的的延迟抖动,但整体硬件的代价相对比较高。从表1可以看出,尽管FORCE10交换机的延迟抖动使主从同步精度变低,但仍然满足加速器快联锁保护系统的时间同步需求。

从表1测试结果也可以看出,随着同步周期增大,主从同步精度逐渐变低,在满足条件的情况下,尽可能降低同步周期,达到更高的同步精度。

5 结语

本文针对普通晶振的频率偏差造成 IEEE1588同步精度低的问题,提出了频率动态补偿算法,在千兆以太网平台上通过测试,验证了频率动态补偿算法的可行性和实用性,且分析了FORCE10交换机的延迟抖动对时间同步精度的影响,尽管FORCE10交换机的延迟抖动使主从同步精度变低,但仍满足加速器快联锁保护系统的时间同步需求。

1 Mills D L. Network Time Protocol (Version3) Specification, Implementation and Analysis. RFCl305[Z]

2 Mills D L. Simple Network Time Protocol (SNTP) Version4 for IPv4, IPv6 and OSI, RFC4330[Z]

3 IEEE Instrumentation and Measurement Society. IEEE Std1588TM—2008 IEEE standard for a precision clock synchronization protocol for networked measurement and control systems[S]. NewYork, USA: IEEE, 2008

4 黄文君, 遇彬. 基于FPGA的精确时钟同步方法[J]. 浙江大学学报(工学版), 2007, 41(10): 1697−1700

HUANG Wenjun, YU Bin. Method for precise time synchronization based on FPGA[J]. Journal of Zhejiang University (Engineering Science), 2007, 41(10): 1697−1700

5 Wu S K, Wang J L, Zhao J. FPGA-based high-precision network time synchronization research and implementation[C]//Electronic Measurement & Instruments (ICEMI), 2011 10thInternational Conference on IEEE, 2011, 1: 329−332