高阻薄层硅外延材料研制

2014-03-22马利行王银海邓雪华谭卫东

马利行,王银海,邓雪华,骆 红,谭卫东

(南京国盛电子有限公司,南京 211111)

高阻薄层硅外延材料研制

马利行,王银海,邓雪华,骆 红,谭卫东

(南京国盛电子有限公司,南京 211111)

根据绝大多数分立器件的技术要求,常规硅外延层电阻率的数值会小于厚度的数值。介绍了一种外延层电阻率数值接近甚至大于厚度数值的高阻薄层硅外延材料的实用生产技术,即在PE-2061S桶式外延设备上,采取特殊的工艺方法,在掺砷(As)衬底上进行高阻薄层外延生长。该工艺通过控制自掺杂,改善了纵向载流子浓度分布,取得了较好的外延参数均匀性。

外延;高阻薄层;自掺杂;均匀性

1 引言

集成电路向高集成、浅结化、高性能方向迅速发展,对外延材料的要求越来越高,高阻薄层外延材料是当前一些特种器件的基础材料。解决外延生长过程中自掺杂是工艺制备高阻、薄层外延的基础。为了减少自掺杂,改善外延层纵向载流子浓度分布,提出了许多方法:如低温生长、高温烘烤、变速生长及二步外延法[1]。但对于高阻薄层外延,因外延层较薄,而电阻率相对又较高,为了形成陡峭的过渡区,本文提出了在外延过程中加入气相腐蚀的特殊步骤,获得了理想的结果。

2 分析

根据硅外延生长动力学过程的模型,气-固表面复相化学反应模型如图1,在接近衬底表面的流体中出现一个流体速度受到干扰而变化的薄层,而在薄层外的流速不受影响,称此薄层为边界层,也叫滞流层[2]。

在外延生长初期,淀积反应物穿过滞流层并与储存在滞流层中的杂质结合向衬底表面迁移,然后在衬底表面发生化学反应实现晶体生长。因升温、烘烤阶段在滞流层中储存了近80%的蒸发杂质[3],所以在外延生长的初期,自掺杂的影响最大。为了清除滞流层中储存的杂质,根据滞流层的经验公式,滞流层厚度与流速平方根成反比,所以加大气流的流速可以使滞流层减薄;另一方面,从二步本征外延的中间过程,插入氯化氢(HCl)气相腐蚀步骤,破坏滞流层,并结合大流量吹扫过程,有效降低了滞流层中的杂质浓度,生长出的外延层过渡区明显变窄,外延参数均匀性满足器件要求。

图1 气-固表面复相化学反应气流示意图

3 实验过程

图2 外延工艺流程示意图

根据外延工艺流程如图2,选用电阻率为0.002~0.004 Ω·cm的重掺砷(As)抛光片,硅片背面为600 nm的二氧化硅(SiO2),抑制背面杂质的蒸发;气相抛光(气腐)改善表面质量,减少外延过程中的缺陷;高温烘烤使硅衬底表面附近形成一杂质耗尽层,减少表面杂质的逸出速度;一次本征生长0.5 μm,覆盖硅片表面,阻止硅片表面的杂质挥发,同时包住了基座,减少了系统的杂质;通入少量氯化氢(HCl),破坏表面滞流层,同时结合大流量H2的吹扫,有效降低了滞流层中的杂质浓度,再进行二次本征生长及掺杂外延生长,从而获得了陡峭的过渡区和电阻率均匀性良好的外延层。

4 实验结果和讨论

选取相同掺砷(As)<111﹥衬底,在同一外延设备上进行常规工艺(工艺A)与在常规工艺的基础上加入通氯化氢(HCl)步骤的工艺(工艺B),进行外延比较,并对这两种方法生产的外延片进行电阻率、厚度及扩展电阻测试。

采用PE-2061S桶式外延炉如图3,其特点是产量大,分上、中、下三层,并有8~10面。

图3 PE-2061桶式外延炉结构示意图

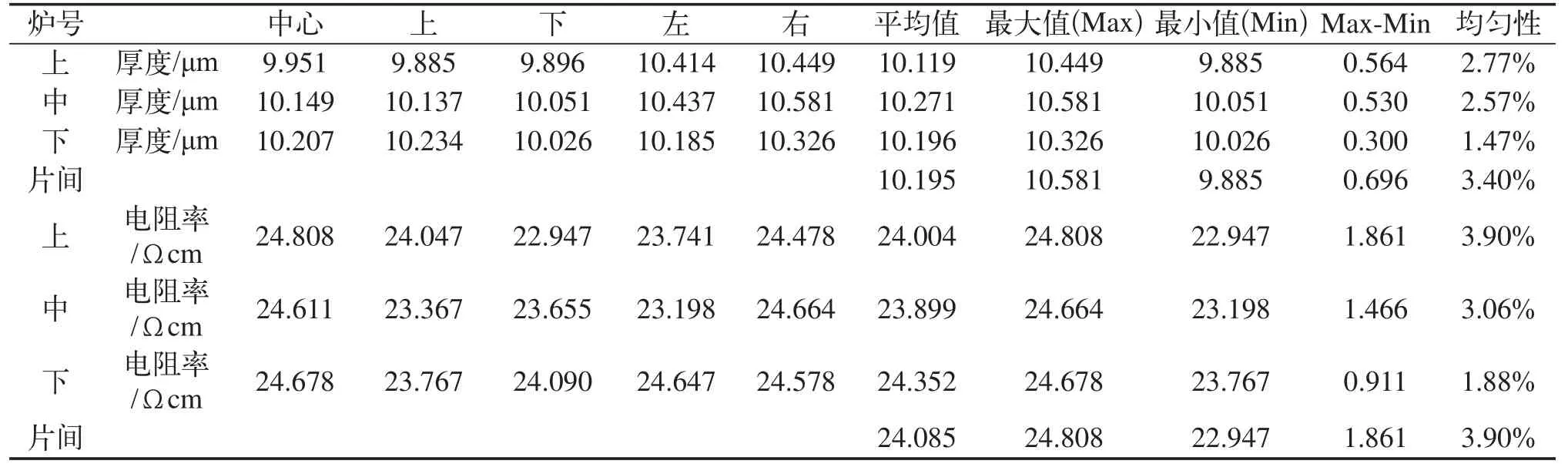

对工艺A和工艺B外延片进行电阻率、厚度均匀性测试。外延层电阻率采用SSM-CV495测试,外延层厚度采用QS2200测试,均匀性测试点为中心点和上下左右边距6 mm,计算公式为(Max-Min)/ (Max+Min)×100%,测试结果如表1。

表1 工艺A外延层厚度、电阻率均匀性

表2 工艺B外延层厚度、电阻率均匀性

通过表1与表2的数据比较,可以看出外延厚度均匀性基本保持一致,而电阻率均匀性从30%降低到4%,改善明显。说明工艺A在外延过程中自掺杂现象较严重,通过高温烘烤、一次本征生长尚不足以消除自掺杂的影响,外延参数均匀性无法满足器件要求;而工艺B通过在生长过程中增加氯化氢(HCl)气腐步骤,破坏了表面滞流层,有效降低了滞流层中的杂质浓度,从而获得了良好的外延层浓度分布,电阻率均匀性满足客户要求。

采用SSM2000扩展电阻测试仪,测得工艺A和工艺B外延片的纵向载流子浓度分布曲线(SRP)如图4所示,工艺B的SRP曲线明显优于工艺A。

图4 工艺A、B外延层纵向载流子浓度分布

5 结束语

本工艺采取二次本征外延过程中通入氯化氢(HCl)的技术方案,在重掺砷(As)衬底上实现了高阻薄层外延的生产方法,控制了自掺杂,改善了过渡区,获得了良好的电阻率均匀性。

[1] Ishii T,Takahahi K,Kondo A,et al. J Electrochem Soc,1975, 122(11):1 523.

[2] Hammond M L. Silicon Epitaxy, Solid State Technol[M]. 1978, 21: 68.

[3] 朱丽娜,闵靖. 硅外延中的杂质控制[J]. 上海有色金属,2003, 24(1).

作者简介:

王征宇(1976—),女,河南汝南人,高级工程师,现在中国电子科技集团公司第58研究所从事集成电路测试工作。

A Research on Silicon Epitaxial Material with High Resistivity Thin Thickness

MA Lixing, WANG Yinhai, DENG Xuehua, LUO Hong, TAN Weidong

(Nanjing Guosheng Electronic CO.,LTD.Nanjing211111,China)

According to the technical requirements of the vast majority of discrete devices, the resistivity of conventional silicon epitaxial layer is lower than the value of the thickness. The paper introduces the practical production technology of a kind of high resistance thin thickness silicon epitaxial material whose resistivity value is close to or even higher than the thickness, namely high resistance thin thickness silicon epitaxial growth on the substrate doped. As with the special process method on the PE-2061s barrel type equipment. Through controlling the auto-doping,the process improves the vertical distribution of carriers concentration and obtains better uniformity of epitaxial parameters.

epitaxial; high resistance thin thickness; auto-doping; uniformity

TN304.054

A

1681-1070(2014)08-0039-03

马利行(1966—),男,江苏苏州人,毕业于无锡无线电工业学校,工程师,现主要从事硅外延技术及半导体材料的研制工作。

2014-06-23