基于VLD技术的MCT器件仿真分析*

2014-03-22阮建新陈万军孙瑞泽彭朝飞

阮建新,陈万军,孙瑞泽,彭朝飞,张 波

(1. 电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054;2. 东莞电子科技大学电子信息工程研究院,东莞 523808)

基于VLD技术的MCT器件仿真分析*

阮建新1,2,陈万军1,2,孙瑞泽1,2,彭朝飞1,2,张 波1

(1. 电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054;2. 东莞电子科技大学电子信息工程研究院,东莞 523808)

针对在脉冲功率领域有一定应用的栅控晶闸管(MCT)器件,提出了一种基于VLD(横向变掺杂)技术的MCT(VMCT)器件新工艺并通过仿真比较出新工艺的优势。VLD技术是指通过调整掩模版窗口的大小调节杂质掺杂浓度,进而优化MCT中NPN晶体管的电流放大系数a,通过仿真确定了新工艺的杂质注入剂量。仿真结果表明采用新工艺的VMCT器件比采用常规工艺MCT(CMCT)电流能力更强,是CMCT的2倍;和CMCT相比,VMCT器件的耐压和关断电压都保持不变,但是VMCT在工艺流程中比MCT节省一张掩模版。

MCT;VLD;击穿电压;电流能力

1 引言

在功率电子器件领域,MCT(MOS Control Thyristor)器件兼备MOS和双极器件的特点,具有高压、大电流、低导通压降、可控性、快开关速度和负温度反馈等一系列优点,使得它有一定的应用潜力[1]。由于电流不饱和特性[2]使得MCT在应用时需要复杂的外部匹配电路,导致了MCT的应用受到了一定的限制;但是随着脉冲功率技术的发展,MCT在脉冲功率领域应用重新[3]吸引了人们对它的研究。从MCT(图1)阴极(Cathode)看,由于P+、N-well和P-well三个阱对杂质浓度要求不同,采用三重扩散[4]形成这三个阱成为了常规MCT(CMCT)的核心工艺。考虑到三重扩散工艺的容宽较小,工艺控制困难,如何优化形成这三个阱的工艺成为关键。本文基于VLD(横向变掺杂)技术对CMCT的三重扩散工艺进行优化,使得新MCT(VMCT)器件相对于CMCT器件在节省一张掩模版的同时也具有较低的导通电阻,并且使用VLD技术可以扩大工艺控制能力。

2 器件结构及工作原理

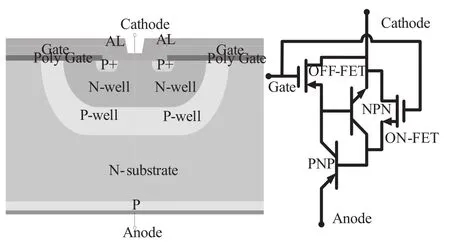

图1是MCT器件结构和等效电路图,从图1中可以看出MCT器件是由MOS控制的PNPN结构组成,它包含了一个寄生的PNPN晶闸管和两个MOSFET;两个MOSFET为等效电路图中的ON-FET和OFFFET,分别起到了开启和关断MCT的作用。当门极[5](Gate)相对阴极施加正电压时,P-well表面出现反型层,提供了电子通道,电子进入漂移区;由于阳极(Anode)和阴极存在电势差,大量空穴从阳极注入到漂移区使PNP晶体管导通;PNP晶体管的集电极电流提供了NPN晶体管的基极电流使NPN晶体管导通,而NPN晶体管的集电极电流又作为了PNP晶体管的基极电流,这样在NPN和PNP晶体管之间形成了正反馈;若满足aNPN+aPNP≥1时,MCT便迅速由截止状态转为导通状态。当门极相对于阴极施加负电压时,寄生NPN晶体管的基极-发射极被短路,使NPN晶体管截止,破坏了晶闸管的擎住条件,使MCT关断。

图1 MCT器件结构和等效电路图

3 器件的工艺分析

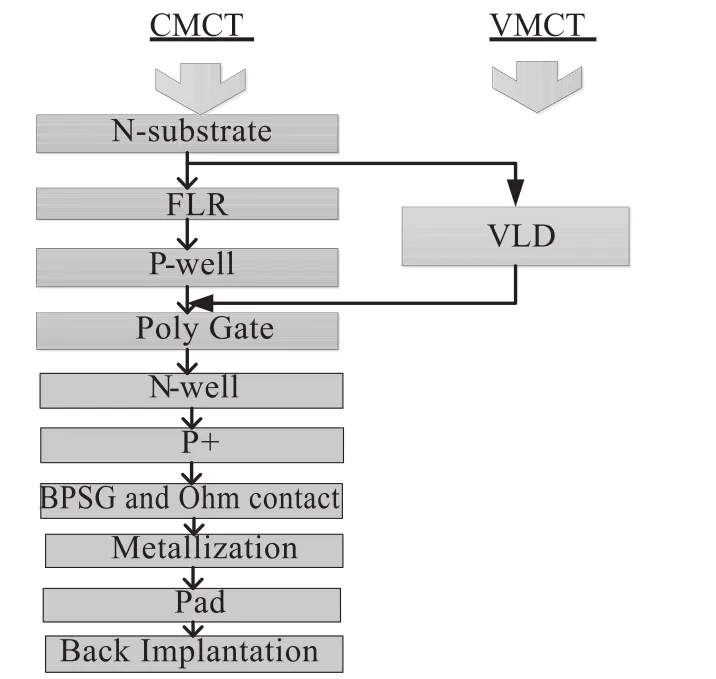

图2是一种典型的CMCT器件工艺流程图[6],从中可以得出CMCT在形成P-well时需要两张掩模版,即FLR(结终端)和P-well,来完成两次杂质注入;在形成FLR时掩模版也在P-well处开孔注入杂质。用两张掩模版的原因是如果采用一次杂质注入造成P-well浓度过大,MCT开启电压增大,电流能力减小;P-well浓度过小,MCT在承受电压的时候P-well里的杂质会耗尽,使得耐压降低,因此优化P-well的浓度成为了关键。

图2 MCT和VMCT器件工艺流程图

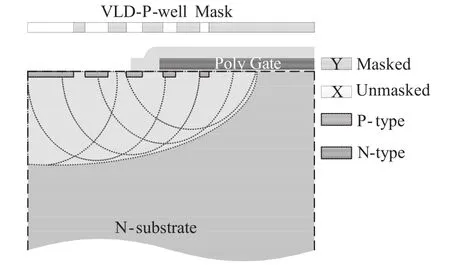

图3 VLD注入窗口示意图

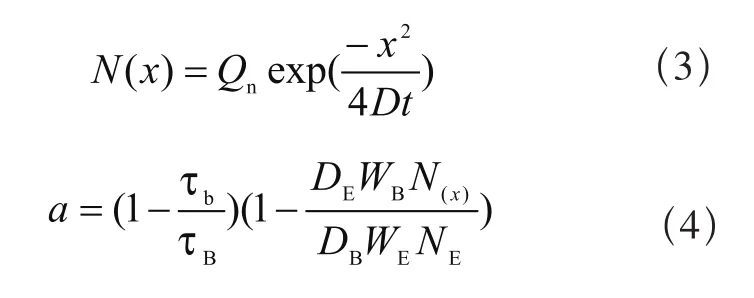

VLD技术是通过调整掩模版的窗口大小和比例调节注入杂质的剂量[7],近而实现调整杂质浓度的目的。本文中P-well的浓度如果过低,在承受电压的时候会穿通;P-well的浓度如果过高,会影响MCT的电流能力,而VLD技术可以解决这一问题。因此本文基于VLD[8]技术提出一种新的MCT工艺,在新工艺中把P-well和FLR用一张掩模版完成,这样在优化P-well浓度的同时也节省了一张掩模版;图3是VLD注入窗口示意图[9],其原理可以用公式[10](1)、(2)、(3)来解释。从公式[10](4)得到采用VLD技术调节P-well的浓度可以优化电流放大系数a,使得寄生晶体管NPN的aNPN提高,从而使器件更容易满足aNPN+aPNP≥1的条件,使得MCT电流能力得到提高。

4 仿真条件

器件采用的是电阻率为80 Ω·cm、<100﹥径向的硅片;VMCT的VLD层的注入剂量为5×1013cm-2;CMCT的FLR和P-well的注入剂量分别为4×1013cm-2和2×1013cm-2;N-well的注入剂量为2×1014cm-2,P+的注入剂量为4×1015cm-2,阳极P的注入剂量为2× 1015cm-2,器件掺杂浓度分布如图4所示。

5 仿真结果和分析

图4 X=5 μm时Y方向的浓度分布

图4是X=5 μm时Y方向的杂质浓度分布,从图中可知CMCT的浓度要高于VMCT,原因在于CMCT中的P-well由两次杂质注入扩散形成,而VMCT只有一次,这也正是VMCT工艺优越之处;此外由于杂质补偿作用导致两种工艺都会出现器件局部浓度很低的情况。

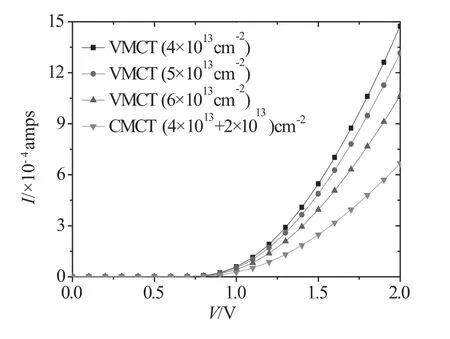

图5 VMCT和CMCT的正向电流图

图5是VMCT和CMCT器件在开通过程中的电流图,图6是当器件导通阳极加2 V电压时部分漂移区(长度100 μm)的电子浓度分布图,从两图中可知采用VLD技术时P-well注入剂量越小,漂移区的电子浓度越大,电流能力越强。采用VLD工艺可以降低P-well的浓度(由图4可知),导致N(X)降低(参考公式4),从而使寄生晶体管NPN的放大系数aNPN变大,使得MCT电流能力更强。但是如何选择VLD工艺的杂质注入剂量又成了问题,由于器件的耐压和P-well浓度有很大关系,器件的耐压成了衡量P-well杂质注入剂量的标准。

图6 漂移区电子浓度分布图

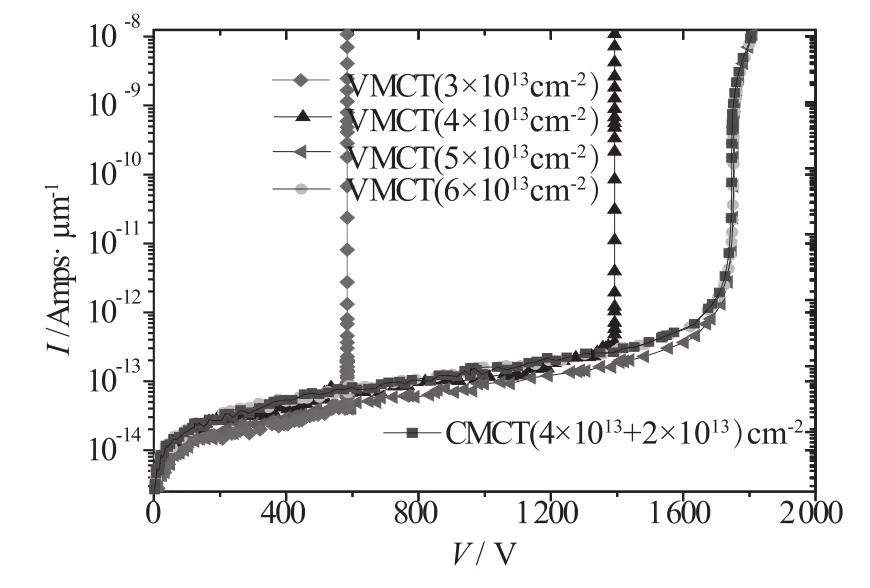

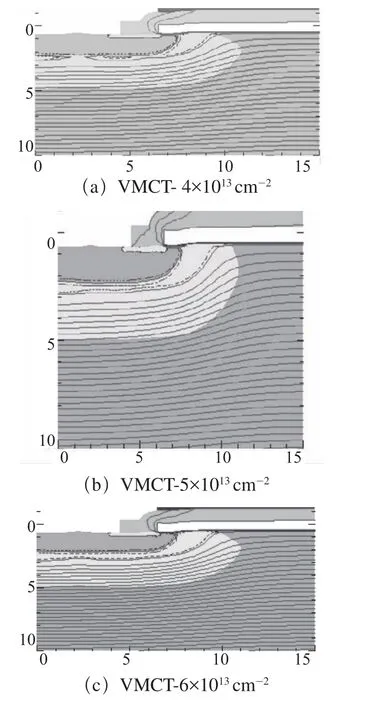

图7 VLD层不同注入剂量下的耐压图

图7为MCT不同注入剂量下的耐压图,图8为MCT正向承受耐压时P-well的耗尽曲线图。从图7中可以得知不同注入剂量的VMCT器件耐压差别很大。采用VLD工艺时,P-well的注入剂量太低会导致耐压时P-well全部耗尽,见图8(a),器件击穿,耐压降低;在注入剂量为5×1013cm-2的时候,VMCT器件的耐压和CMCT器件的耐压同样达到1740 V;注入剂量增加到6×1013cm-2的时候,VMCT器件耐压几乎保持不变且P-well并没有完全耗尽,见图8(c)。从图5可知注入剂量为5×1013cm-2时VMCT器件电流能力强于注入剂量为6×1013cm-2时,并且注入剂量为5×1013cm-2时VMCT的电流能力近似于CMCT的2倍,因此选择5 ×1013cm-2的注入剂量。但是由于MCT关断特性不好的特点,在选择P-well注入剂量的时候应该考虑其是否对MCT的关断特性造成影响。

图8 MCT的正向耐压P-well耗尽曲线

由于杂质补偿作用P-well浓度改变会导致N-well浓度改变,N-well浓度变化会改变器件的关断阈值电压。图9是MCT在不同注入剂量下的关断电压图,从图中可知注入剂量为5×1013cm-2时的VMCT和CMCT关断电压相同,所以选择注入剂量为5×1013cm-2。

6 结束语

图9 不同注入剂量下MCT的关断电压

本文在CMCT的工艺流程基础上提出了一种新的工艺流程,采用横向变掺杂工艺替代以前的两次扩散工艺。仿真结果表明,和CMCT相比,VMCT的电流能力得到了很大提高,阳极外加电压2 V时VMCT电流能力近似于CMCT的2倍;此外VMCT器件相对于CMCT器件在工艺流程上还节省一张掩模版。有了新工艺,MCT在功率脉冲电子领域将会有更大的应用潜力。

[1] B J Baliga. Enhancement and depletion-mode verticalchannel M.O.S. gated thyristors[J]. Electronics Letters, 1979, 15(20): 645-647.

[2] 俞苹. MOS控制晶闸管(MCT)的特性、驱动及应用[J].电力电子技术, 1995, (02).

[3] 高勇,陈治明. 新型电力电子器件与功率集成电路最新进展[J]. 半导体技术, 1997, (03).

[4] 李学宁,唐茂成,李肇基. MOS控制晶闸管三重扩散工艺[J].电子学报, 1996,05.

[5] B. J. Baliga. Fundamentals of power semiconductor devices[M]. New York: Springer Scientific, 2008.

[6] Michael.Quirk, Julian Serda.半导体制造技术[M]. 北京:电子工业出版社,2003.

[7] R Sten gl, U Gosele. Variation of Lateral Doping-A New Concept to Avoid High Voltage Breakdown of Planar Junctions [C]. in IEDM, 1985. 154-157.

[8] H Jiang, B Zhang, W Chen, et al. A simple method to design the single-mask multi-zone junction termination extension for high-voltage IGBT[C]. Proc. of International Symposium on Power Semiconductor Devices & ICs, Bruges, 2012, 173-176.

[9] S Merchant. Arbitrary lateral diffusion profiles[J]. IEEE Trans. Electron Device, 1995,42(12): 2226-2230.

[10] 陈星弼,张庆中. 晶体管原理与设计(第二版)[M].北京:电子工业出版社,2006.

Simulation and Analysis of MCT Device Based on VLD Technology

RUAN Jianxin1,2, CHEN Wanjun1,2, SUN Ruize1,2, PENG Zhaofei1,2, ZHANG Bo1

(1.State Key Laboratory of Electronic Thin Film and Integrated Devices,UESTC,Chengdu610054,China; 2.Institute of Electronic and Information Engineering in Dongguan,UESTC,Dongguan523808,China)

MOS controlled thyristor (MCT) which is used in pulsed power field is investigated by numerical simulation tool in this paper. A new process based on VLD(variable lateral doping) technology for MCT is proposed and its advantages are also found by simulation. Current amplification factoraof NPN transistor in MCT is optimized by adjust the size of mask and the dose of impurity implantation.The dose of impurity implantation is identified by simulation.The simulation results indicate that the current ability of conventional MOS controlled thyristor (CMCT) is only half of the VLD MOS controlled thyristor (VMCT). The breakdown voltage and turn off voltage of VMCT are the same as CMCT.However, compared with CMCT, a mask is saved in the VMCT process.

MCT; VLD; breakdown voltage; current ability

TN386.2

A

1681-1070(2014)08-0028-04

阮建新(1988—),男,河南开封人,电子科技大学硕士研究生,研究方向为新型功率半导体器件与集成电路和系统。

2014-03-07

国家科技重大专项02专项(2011ZX02706-003);预研项目(51308030407)