基于FPGA的Buck变换器新型DPWM技术研究

2014-03-12王树文王峥峥常宇恒郑博元

王树文,张 冰,高 鹏,王峥峥,常宇恒,郑博元,李 楠,王 健

(东北农业大学电气与信息学院,哈尔滨 150030)

脉宽调制(PWM)型DC/DC变换器被广泛应用于开关电源、直流电机调速及便携式电子产品等领域。近年来,电力电子技术发展迅速,应用计数器和延迟线实现典型DPWM。这两种方式的不足是若单独使用计数器,使计数器产生很多功耗;若单独使用延迟线,会使硅区面积迅速增加。

本文充分利用FPGA高性能、低功耗、多逻辑单元等优点[1],采用Verilog HDL硬件描述语言[2]或者输入原理图方式,利用QuartusⅡ进行仿真。针对传统DPWM技术不足,提出MDPWM设计方案,即在计数器的传统DPWM设计基础上,增添一个与主计数器相反的辅助计数器;在延迟线的传统DPWM设计的基础上,增加辅助延迟单元。仿真结果表明,MDPWM技术能减少开关管开通和关断延迟时间、减小器件的功率损耗,当负载波动时,输出电压瞬态响应快,使输出电压稳定性好。方法简单可行,对实际应用具有指导意义。

1 Buck变换器的拓扑及基本工作原理

开关变换器输出电压与输入电压关系通过反馈控制原理实现,变换器拓扑结构和工作原理由输入—输出电压关系决定。直流斩波电路种类较多,包括六种基本斩波电路:降压斩波电路、升压斩波电路、升降压斩波电路、Cuk斩波电路、Sepic斩波电路和Zeta斩波电路。这些类型的斩波电路都是在开关控制电路中,在一个时钟周期的储能元件利用其导通时间和关断时间实现输入电压与输出电压的转换关系。本文主要针对Buck型变换器进行研究。

1.1 Buck变换器的拓扑及基本工作原理

Buck型变换器又称为降压变换器,因为输出电压要低于输入电压,作为最基本DC-DC拓扑结构,广泛应用于各式各样的开关电源中[3]。其中,Buck型变换器电路结构如图1所示。

图1 Buck变换器电路结构Fig.1 Circuit of Buck converter

由图1可知Buck电路由开关管VT、二极管VD、电感L和电容C组成,开关管VT受占空比为D的脉冲控制,使其导通或截止,再经过L和C组成的滤波器,得到负载R上的直流输出电压,最后完成从未经稳压的直流输入电压到平滑直流输出电压的转换过程[4]。Buck电路中开关管的导通和关断等效结构见图2,开关管的通断主要靠PWM控制方式实现,本文利用DPWM方式控制开关管导通和关断。

图2 Buck型开关管导通和关断等效结构Fig.2 Equivalent structure of Buck switch tube to turn on or turn off

在开关管VT导通期间,二极管VD截止,电源通过电感L向负载提供电能。电流流过电感L时,在电感未饱和前电流线性增减,负载R流过电流IO,R上的电压即输出电压UO,其极性为上正下负。当Ii>IO时,电容器C处于充电状态。在开关管VT截止期间,Ii=0,而电感中的电流iL不会发生突变,电感L中的磁场将改变L两端电压UL的极性,以维持电流iL不变,负载R上的电压UO仍保持上正下负。流过电感的电流iL将线性减小,在减小到IO之前,电感电流给负载供电,同时给电容充电;在iL<IO时,电容器C处于放电状态,以维持IO不变,即保持输出电压IOR(UO)不变,二极管VD处于正偏置状态,为电感电流iL和输出电流IO提供通路,所以二极管VD起续流作用[5]。

当在稳态工作时,流经电感上的电流是否可以下降到零,以此为根据把电路工作的状态分为连续模式(CCM)和断续模式(DCM)两种。假设流经电感上的电流的最小值大于零时,则可认为变换器是工作在连续导通模式下;假设在整个开关周期中,流经电感上的电流有在一段时间内有为零的情况出现,则可以认为变换器是工作在不连续导通模式下。且这两种模式的临界情况是流经电感的电流下降到零开关刚好打开。

1.2 DPWM主要的实现方式

DPWM发生器的功能是根据占空比大小d(n)产生对应开关频率的控制信号d(t)。目前,采用FPGA可实现比较成熟DPWM方法主要有:计数器方式、延迟线方式、数字抖动的计数混合方式、∑-Δ方式等[6-10]。与前两种方法比较,虽然∑-Δ方式对DPWM的性能有所提高,但实现较为复杂,会对功率损耗增加。因此,本文主要介绍计数器和延迟线两种方法。

1.2.1 计数器方式

计数器方式是DPWM发生器最典型的实现方式,其原理是依据DPWM发生器d(n)所使用的位数N,用一个时钟频率为fc=2Nfs的信号控制计数器的计数。在每一个开关时钟开始时对d(t)置高电平。当计数时钟计数到d(n)所表示大小的数据时,d(t)输出为低电平。即可得到时间与占空比对应大小的栅极控制信号d(t)。

这种实现方式需要一个N位的计数器和一个时钟频率为fc=2Nfs时钟信号,时钟频率较高。以时钟频率为1 MHz为例,如果使用10位的DPWM发生器需一个频率为1024 MHz的时钟信号,成本颇高。虽然利用FPGA倍频方式同样可以实现,但时钟频率过高,不仅对系统稳定性造成严重影响,会产生高频干扰。

1.2.2 延迟线方式

基于延迟线较常采用的结构实现方式见图3。在此结构中,缓冲器延迟线和选择器是关键单元。当一个Clock脉冲开始时,RS触发器的Set置高电平,则会使PWM的OUT输出为高电平。于是,Clock脉冲便会沿着缓冲器构成的延迟线依次传播,当MUX选中该脉冲后,则会输出到RS触发器的Reset端。此时,RS触发器Set=0、Reset=1,OUT即为0电平。且延迟线中总延迟设计与Clock周期相等。

图3 基于延迟线的DPWM发生器结构Fig.3 Structure of DPWM generator based on the delay line

基于延迟线结构的DPWM发生器主要缺点是MUX面积随DPWM发生器分辨率位数n呈指数级的增长。假设要实现一个10bit的DPWM,则需要1024位的多路复用器,造成面积浪费。工艺和温度变化直接影响半导体器件和电路,电路性能存在偏差。因此,导致延迟单元延迟时间变化。

1.2.3 数字抖动的计数混合方式

通过在输出DPWM波形中提高抖动,使DPWM发生器分辨率增加,此为数字抖动实现方式。利用数字抖动去提高DPWM发生器分辨率是根据功率级的稳态输出电压是平均化结果。

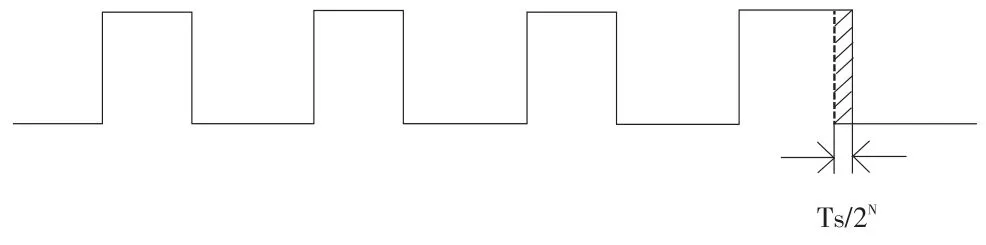

如图4所示,假设在稳态的时候,一个N位的DPWM发生器的输出控制信号波形中每4个输出脉冲只在最后一个脉冲宽度上增加一个Ts时长,如果在其增加之前输出电压为VO,那么增加之后这4个脉冲信号控制的输出电压变化则为VO+VIN,平均一个时钟周期多变化了Ts,且平均到一个周期输出电压变化即为

图4 数字抖动原理Fig.4 Principle of digital jitter

2 传统的DPWM设计

2.1 基于计数器的DPWM设计

基于计数器的设计是利用VerilogHDL语言进行设计仿真,其灵活性强,还能够降低开发成本。在数字PWM中,占空比的值与计数器的值相比较,即可产生DPWM信号。在本试验中,计数器每个计数的单元时间是2 ns。计数器可以递增计数,也可以递减计数,这取决于其调制方式。当主计数器计数下降时,则为前缘调制。当主计数器计数上升时,则为后缘调制。而且前缘调制对于DPWM信号会有关断延迟,后缘调制则会有打开延迟。基于计数器的传统DPWM设计的主要优点是简单化和线性关系。为实现高分辨率计数器的比特率会很高,其主要缺点是需要很高的时钟频率和功率消耗[10-13]。因此,基于DPWM的实现高频率、高分辨率的计数器有一定困难[14]。

2.1.1 前缘数字脉宽调制

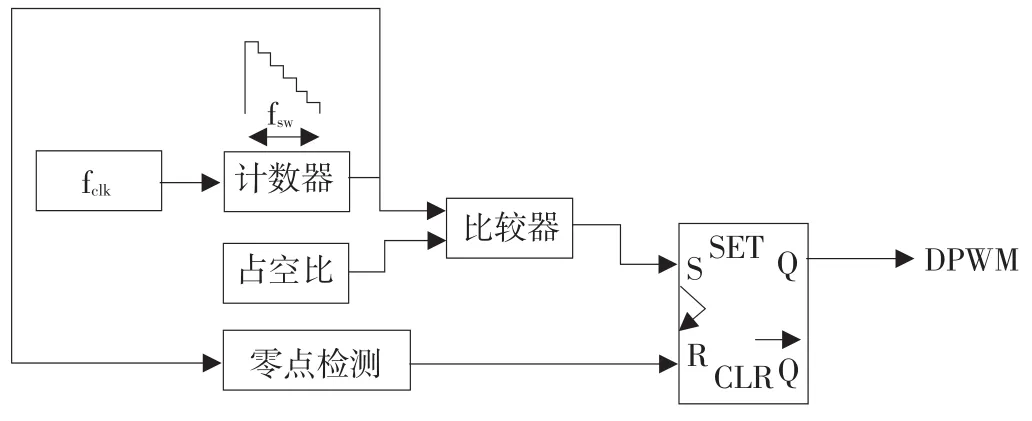

基于计数器的前缘DPWM控制框图(见图5),占空比和计数器的值输入到比较器中,计数器开始向下计数。当占空比值高于计数器值时,S-R触发器设置DPWM信号为高电平,这时比较器的输出变为DPWM脉冲。且DPWM仅在开关周期结束时,才被关断。当主计数器完成计数为零时,则重置。

图5 基于计数器的前缘DPWM框图Fig.5 Block diagram of Leading-edge DPWM based on counter

占空比的低于计数器值,但调制器不能对其变化产生相应的反应,会等待直至开关周期结束后,才关断DPWM信号。这个关断延迟会导致感应器过度充电,感应器会提供更多的输出功率,并导致额外的过冲或环回路输出电压。因此,这种传统的前缘调制在关断DPWM时,会产生延迟。

2.1.2 后缘数字脉宽调制

基于计数器的后缘DPWM控制框图(见图6),在这个方案中,主计数器向上计数,DPWM信号由固定的时钟信号打开,通过比较器输出而关断。比较器输入类似于前缘调制。当占空比的值低于计数器值时,DPWM脉冲被关断。当占空比在相同的开关周期继续变高,调制器将对其改变不会有相应反应,等待直到下一个开关周期,才打开DPWM信号。

图6 基于计数器的后缘DPWMFig.6 Block diagram of Trailing-edge DPWM based on counter

占空比值高于计数器值,但调制器不能对其变化产生相应的反应,会等待直至开关周期结束后,才打开DPWM信号。因此,导致打开延迟。

2.2 基于延迟线的DPWM设计

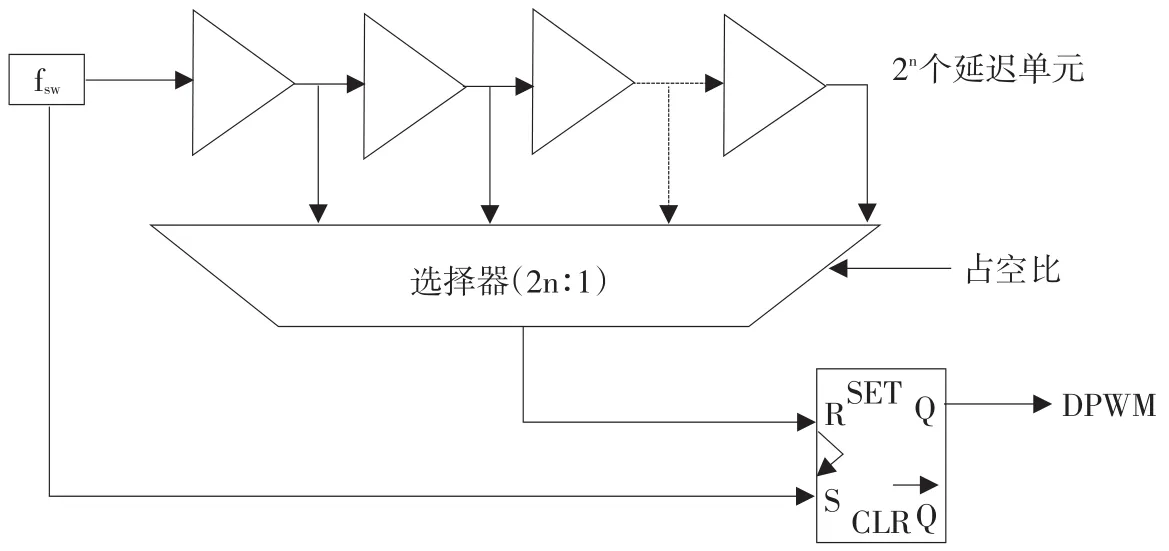

这类调制采用串联延迟单元连接,脉宽被量化为一个延迟单元的函数,若有n位占空比,则会有2n个延迟元件被使用,通过选择器选择延迟单元。选择器以n位占空比,2n∶1的方式进行选择。因此,选择器的控制信号也是n位,去执行延迟单元的选择。在本试验中,延迟线的每个门的延迟时间是5 ns。基于延迟线的DPWM的设计框图(见图7)。

图7 基于延迟线的DPWMFig.7 Block diagram of DPWM based on delay line

3 改进的MDPWM设计

计数器法结构虽简单、占用面积小,但当DPWM精度要求较高时,则有可能导致计数器产生相当大功耗。延迟线法即使能获得精度较高DPWM,却会导致硅区面积急剧增加。在传统的数字脉宽调制方案中,前缘数字脉宽调制显示关断延迟,后缘数字脉宽调制显示打开延迟。因此,本文提出DPWM改进方案(MDPWM)以减少此类延迟。

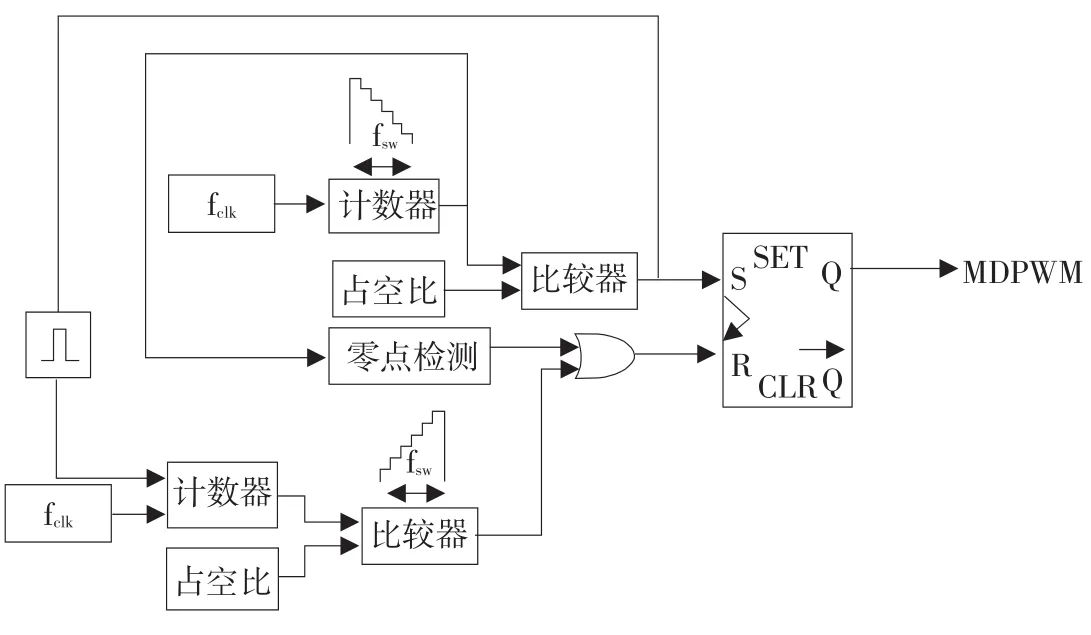

基于计数器的前缘MDPWM的控制原理图(见图8),其基本概念是增添辅助计数器。主计数器是在前缘DPWM情况下的降值计数器,补充辅助计数器是一个与主计数器相反的升值计数器。在传统的前缘调制设计中,当DPWM信号设置为高电平之后,DPWM信号在任何时间都不能被关断,直到该周期结束为止。相反,在MDPWM设计中,当辅助计数器值达到占空比的值时,开始向上计数。此时,DPWM信号设置为高电平,在开关周期结束时,设置为低电平。这样,当占空比从高变低时,DPWM会立即复位,以减少关断延迟时间。

图8 基于计数器的前缘MDPWM控制原理Fig.8 Control principle diagram of Leading-edge MDPWM based on counter

基于计数器的后缘MDPWM控制原理(见图9),图9显示,由传统后缘数字脉宽调制所引起打开延迟的降低方法。操作如下,主计数器是在后缘DPWM情况下的升值计数器,辅助计数器是一个与主计数器相反的降值计数器,其原理与前缘MDPWM控制原理相同。

图9 基于计数器的后缘MDPWM控制原理Fig.9 Control principle diagram of trailing-edge MDPWM based on counter

基于延迟线的MDPWM控制原理图(见图10),延迟单元数量取决于DPWM位数量。在传统的DPWM延迟线中,其DPWM脉冲的设置取决于延迟元件,而复位则取决于时钟信号。在MDPWM中,延迟元件会使DPWM脉冲复位,而设置动作则是由一个时钟信号或者是辅助延迟元件完成。当在一个开关周期中,有一个以上的占空比变化时,所添加延迟元件使DPWM脉冲做出及时响应。因此,会降低延迟时间。

图10 基于延迟线的MDPWM的控制原理Fig.10 Control principle diagram of MDPWM based on delay line

4 结果与分析

FPGA(Field programmable gate array,现场可编程逻辑门阵列)产生于20世纪80年代中期,采用掩膜可编程阵列结构,不受“与或”阵列结构的限制,靠内部逻辑单元构成复杂的逻辑电路。

Quartus II是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL(Altera hardware description language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程,使设计者能够方便进行设计输入、设计处理和器件编程[15]。

Quartus II的特点如下:

①能支持多时钟定时分析、LogicLockTM用于模块的设计、SOPC(可编程片上系统)、内嵌SignalTapⅡ、功率估计器等高级工具。

②使引脚的分配及时序约束能够更方便。

③其内部还包括有MAX+plusⅡ的GUI,而且容易将MAX+plusⅡ的工程可以稳定地过渡到Quartus II的开发环境中去。

④对于Fmax设计而言,拥有良好的预期效果。

⑤能够支持的器件种类较多。

FPGA的设计需要遵守一定开发流程,在流程的固定环节中,还需要遵守固定的原则和规定。FPGA的设计流程大致上包括系统规范、模块设计、设计输入、功能仿真(前仿真)、综合、布局布线、时序验证(后仿真)、配置下载等8个步骤,设计流程如图11所示。

图11 设计流程Fig.11 Flow of design

4.1 DPWM和MDPWM的仿真结果比较

考虑到传统DPWM在某种程度上的局限性,因此本文提出一种用FPGA实现DPWM控制器的方案。该方案具有高频高精度、频率可调、速度快、易修改、可现场编程等特点。其中,DPWM信号输出的周期时间是1MHz。

在仿真实验的主电路中,各参数如下:

VIN=4.75v-23 v,VO=3.3 v,L=2.2 uH,C=4.7 uF,f=1 MHz。

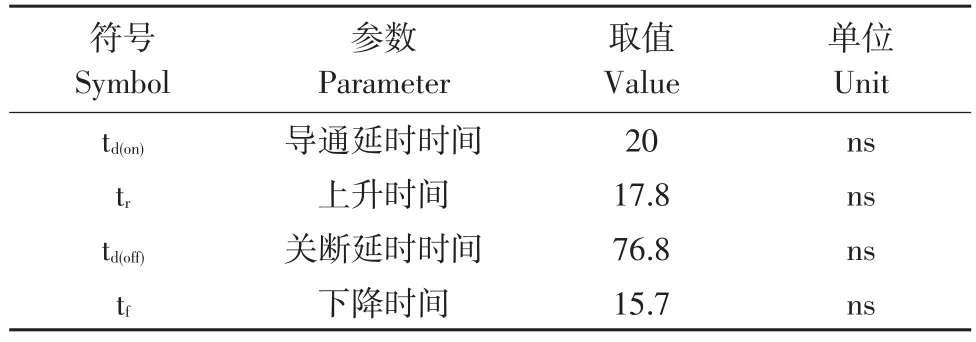

开关管VT选择SSF7509,是采用新技术制成的中压大电流N沟漕增强型功率MOSFET。其优点是这项新技术增加单胞,同时降低导通电阻。VT参数特性如图表1。

表1 VT参数特性Table 1 Parameter character of VT

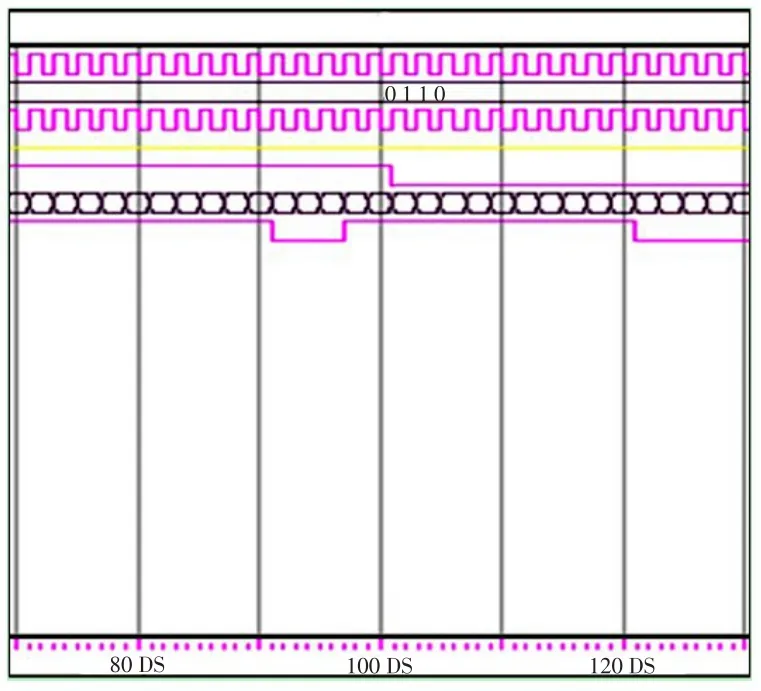

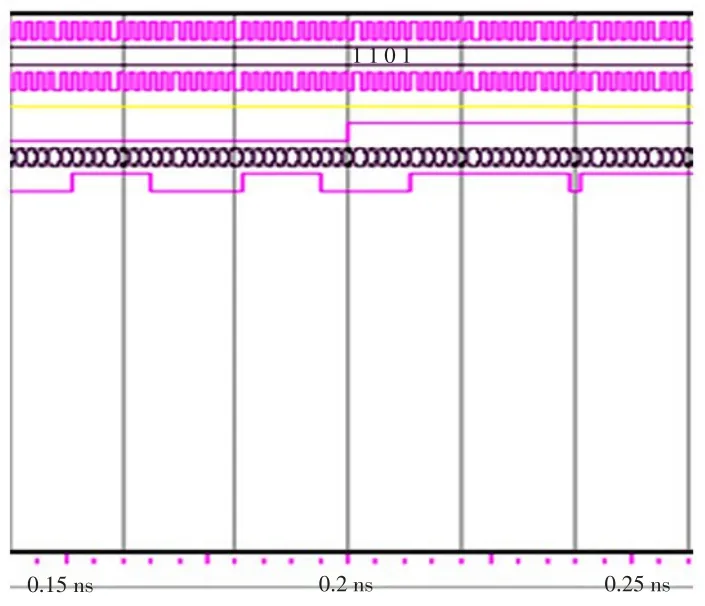

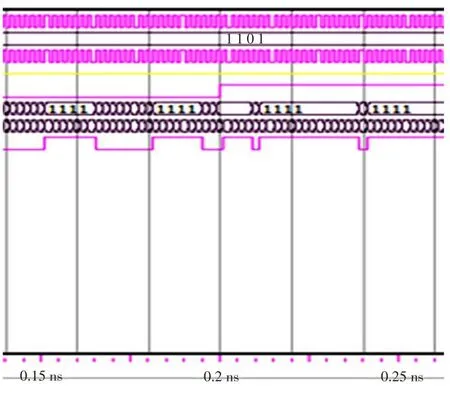

如图12、13所示,比较基于计数器的传统DPWM和改进MDPWM仿真结果。可以看出,当在前缘脉宽调制方式中,在相同的时间点上(100 ps=0.1 ns)附近,占空比从高变低,相比于传统的DPWM,本论文提出的改进方案,它不会等待直到开关周期结束,MDPWM才复位。相反,所输出的DPWM信号,能在任何时间对占空比的变化有所改变和复位。因此,减少关断延迟时间。图14、15可以看出,相同于前缘脉宽调制,在后缘脉宽调制方式中,0.2 ns这一点上,所提出的MDPWM方案中,输出DPWM信号对占空比改变做出响应,减少打开延迟时间。

图12 基于计数器的前缘DPWM仿真Fig.12 Simulation of Leading-edge DPWM based on counter

图13 基于计数器的前缘MDPWM仿真Fig.13 Simulation of Leading-edge MDPWM based on counter

图14 基于计数器的后缘DPWM仿真Fig.14 Simulation of trailing-edge DPWM based on counter

图15 基于计数器的后缘MDPWM仿真Fig.15 Simulation of trailing-edge MDPWM based on counter

如图16、17所示,比较基于延迟线的传统DPWM和改进MDPWM两个仿真结果。可以看出,在20.0~30.0 ns这个时间段上,时钟信号值有一个以上的变化时,相比于传统的DPWM,本文方案中,输出DPWM对变化能较快做出响应,减少延迟现象。

图16 基于延迟线的DPWM仿真Fig.16 Simulation of DPWM based on delay line

图17 基于延迟线的MDPWM仿真Fig.17 Simulation of MDPWM based on delay line

通过仿真结果比较,可见本文提出MDPWM方案具有可行性,能减少传统DPWM造成延迟时间,使输出脉冲响应变快,提高效率。

4.2 负载输出的影响

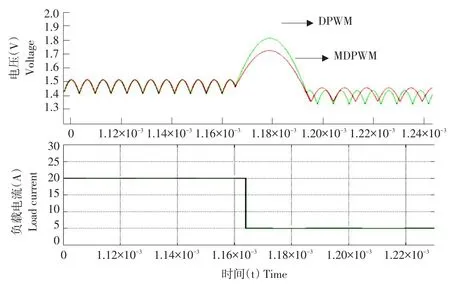

当负载瞬态电流突然变化时,就会产生输出电压偏差现象。为维持稳定的输出电压,控制信号必须指示DPWM更快地打开或关断。因此,电压的偏差必须减少以满足负载动态的需求。这时,需改变占空比维持稳定的输出电压,即改变导通时间。负载的输出电压和瞬态电流变化情况如图18所示。

图18 负载的输出电压和瞬态电流Fig.18 Output voltage of the load and transient current

通过Matlab仿真结果的比较,本文提出的MDPWM方案,当负载电流瞬态变化时,降低负载输出电压偏差。使输出电压维持在良好稳定状态下。可见由于减少延迟时间,获得负载输出动态响应改进。

5 结 论

PWM控制技术以其控制简单、灵活和动态响应好优点成为电力电子技术最广泛应用控制方式。本文主要针对数字脉宽调制技术,对Buck型DC-DC变换器中的开关管VT进行控制,利用FPGA的Verilog HDL硬件描述语言,通过QuartusⅡ软件进行仿真。分别用传统的DPWM和改进方案MDPWM控制方式实现,比较两者仿真输出结果。

结果表明,MDPWM对占空比改变马上进行响应,减少延迟时间,其减少范围为6 ns。该设计具有较强可行性,提高开关管VT效率,影响Buck型DC-DC变换器负载输出。因为MDPWM方案可减少延迟时间,当负载电流瞬态变化时,对输出电压的偏差起抑制作用。使负载的输出电压响应及时、调速变快,维持在稳定状态下,对Buck型DC-DC变换器具有参考和推广价值。

[1] 冯远辉.FPGA的现状及展望[J].电子设计应用,2006(2):1-3.

[2] 刘福奇,刘波.Verilog HDL应用程序设计实例精讲[M].北京:电子工业出版社,2009:291.

[3] 高凡凡.于FPGA控制的DC-DC变换器研究[D].西安:西安科技大学,2012.

[4] 刘树林,刘健.开关变换器分析与设计[M].北京:机械工业出版社,2010.

[5] Kocybik P F,Bateson K N.Digital control of a ZVS fullbridge DCDC converter[C].IEEE APEC Rec Dallas,USA,1995:687-693.

[6] Wyns A,Bogaerts D.Pspice simulations and 3D-PCB transformers for ZVS full-bridge converters[J].EPE Rec Switzerland,1993(3):208-215.

[7] Vlatkovic V,Sabate J A.Small signal analysis of the phaseshiften PWM converter[J].IEEE Trans Power Electronics,1992,7(1):128-135.

[8] 白永江,冯维一,杨旭.高精度数字PWM的实现——数字“抖动”[J].电力电子技术,2007(8):54-56.

[9] Zdravko Lukic,Nabeel Rahman,Aleksandar Prodic.Multibit∑-ΔPWM digital controller IC for DC-DC converters operating at switching frequencies beyond 10 MHz[J].Ieee Transactions on Power Elcetronics,2007(9):1693-1707.

[10] Prodic D.Maksimovic and Erickson R W.Design and implementation of a digital PWM controller for a high-frequency switching DC-DC power converter[J].The 27th Annual Conference of the IEEE Industrial Electronics Society,IECON,2001(2):893-898.

[11] Syed A,Ahmed E,Maksimovic D,et al.Digital pulse width modulator architectures[J].IEEE Power Electronics Specialists Conference,2004,6(4):4689-4695.

[12] Yousefzadeh V,Takayama T,Maksimovic D.Hybrid DPWM with digital delay-locked loop[J].IEEE Workshop on Computers in Power Electronics:2006:142-148.

[13] Castro De,Sutter A,G.,Huerta,S C,CobosJ A.High resolution pulse width modulator in FPGA[J].IEEE 3rd Southern Conference on Programmable Logic,2007(7):137-142.

[14] Pit-Leong Wong,Fred C.Lee.Switching action delays in voltage regulator modules[J].IEEE Power Electronics Specialists Conference,2002(2):675-678.

[15] 周润景,等.基于QuartusⅡ的数字系统Verilog HDL设计实例详解[M].北京:电子工业出版社,2010.