基于五光谱TDICCD的模拟信号发生器设计

2014-03-05王旭刘正敏樊奔何志宽

王旭 刘正敏 樊奔 何志宽

(北京空间机电研究所,北京100094)

0 引言

多光谱电荷耦合器件(CCD)是在一个CCD器件内实现可探测多个光谱的线阵,其实现方式是将多条CCD线阵封装在一起,再采用镀膜或窗口分光的方式,使每条线阵探测不同光谱。多光谱TDICCD是多光谱CCD器件的一种,其光敏面全部由TDICCD阵列组成[1]。

经过20多年的发展,我国空间多光谱CCD相机的研制取得了长足的进步,高性能的多光谱TDICCD器件开始被广泛应用到最新的多光谱CCD相机中,进而大幅简化航天相机设计的复杂程度[2-3]。但是多光谱TDICCD器件的价格昂贵,而且相机研制阶段的多次调试也会增加损坏的风险,采用通用的信号发生器模拟的多光谱TDICCD信号又存在输出波形固定、通道数量有限和信号时序失配等问题。针对以上问题,文章根据某高分辨率多光谱相机定制的五光谱TDICCD的特性,设计了一种基于现场可编程门阵列(FPGA)的16通道TDICCD模拟信号发生电路,其输出的模拟TDICCD信号可以同时满足航天相机研制对五光谱TDICCD波形、通道数量和时序的要求,在输出模拟信号频率达到20MHz时,噪声可以控制在10mV以内,达到了高精度、多通道、低噪声等特点,可以为空间多光谱TDICCD相机研制提供信号源,有效缩短研制周期。

1 五光谱TDICCD器件的时序关系和输出特性

TDICCD是时间延迟积分CCD,其中TDI也称作延迟相加或者运动补偿模式,是一种能够增加线扫描传感器灵敏度的扫描技术[4-5]。其工作过程是基于对同一目标的多次曝光,通过延迟积分的方法,来增加等效积分时间,增强光能的收集。与普通CCD相比,TDICCD通过可变的积分级数,增加了曝光时间,因此具有更高的灵敏度,可以在低光照度环境下成像,又不影响扫描速度[6-8]。

某高分辨率多光谱航天相机定制的五光谱TDICCD器件由一条6 144个像元的TDICCD和4条3 072个像元的TDICCD组成,通过在窗口玻璃上镀滤光膜实现分光,使该器件可以探测P区、B1区、B2区、B3区和B4区共5个谱段。其中P区像元尺寸为10µm(水平)×10µm(垂直),有8通道输出,B区像元尺寸为20µm(水平)×20µm(垂直)(包括B1、B2、B3和B4四个谱段)共有8个通道输出,16个通道的最高输出频率都是20MHz。

信号发生器系统除了要产生16通道最高频率20MHz的模拟TDICCD信号,同时对P区和B区像元时钟和同步信号之间的相位关系也有严格的要求。图1是五光谱TDICCD像元时钟和同步信号之间的相位关系。

图1 五光谱TDICCD像元时钟和同步信号之间的时序关系Fig.1 Tim ing diagram of five-spectral TDICCD pixel clock and synchronous signal

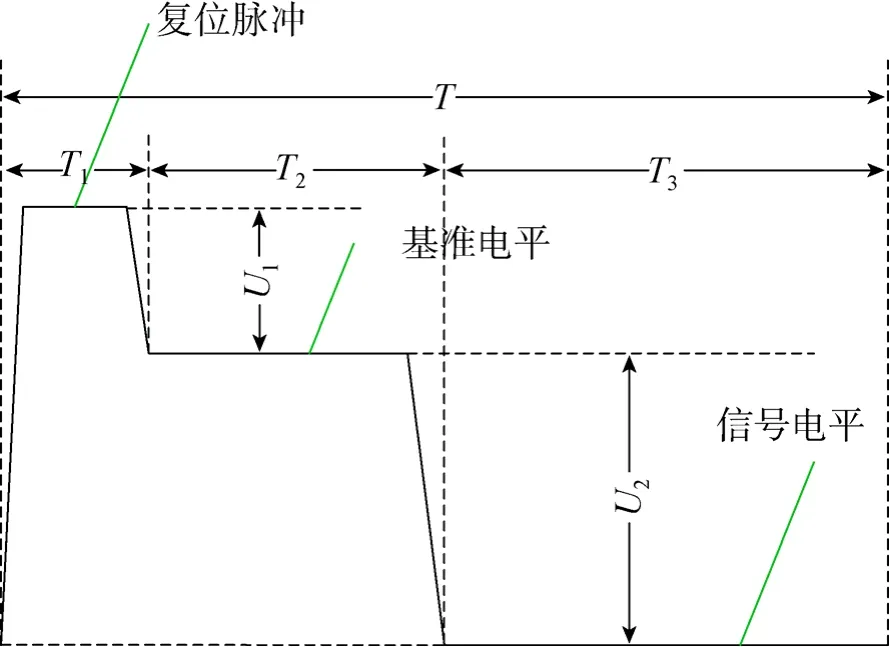

除了通道数量、信号频率和相位要求,信号发生器系统输出的模拟TDICCD信号波形也有幅度参数和时间参数两个要求。图2是五光谱TDICCD信号波形的示意,波形由复位脉冲、基准电平和信号电平三部分组成。在每一个像元周期开始时,在信号电荷到达之前,复位脉冲的到来使复位开关接通,即在内部存储电容上复位一个参考电平。当信号电荷到来时,复位开关截止,信号电荷注入到已被复位的存储电容上,使电位降低ΔU,输出缓冲放大器的源极也跟随变化。这一过程主要是把CCD光电转换获得的电荷转换成以电压形式输出的视频信号,ΔU的大小反映了光信号的强弱,而转换过程产生的复位噪声可以通过相关双采样技术来有效清除[9]。针对五光谱TDICCD的特点,本系统设计的复位过冲U1为0.5V,最大信号电平U2为1.5V;时间参数方面,复位脉冲时间T1、基准电平时间T2和信号电平时间T3这3个时间设计成1∶2∶3的关系,分别是1/6个像元时钟、1/3个像元时钟和1/2个像元时钟。

图2 五光谱TDICCD信号波形Fig.2 Signalwaveform of five-spectral TDICCD

2 电路的系统设计

信号发生器系统主要由图像处理电路、数模转换电路和模拟信号滤波电路三部分组成(如图3所示),其中图像处理电路主要由FPGA、第二代双倍速率同步动态随机存储器(DDR2)和闪存(FLASH)组成。FLASH负责存储来自上位机的图像数据;DDR2作为FLASH和FPGA之间的缓存用来提高数据读取速度;FPGA以本地20MHz的晶振时钟作为工作时钟,进行相应的数据处理和数据拼接,然后数模转换电路以6倍本地时钟(120MHz)的频率进行数模转换,产生16路TDICCD模拟信号,最后为了提高信号精度,模拟信号滤波电路对16路TDICCD模拟信号进行滤波处理。

图3 信号发生器系统的组成Fig.3 Block diagram of system

2.1 图像处理电路

(1)器件的选择

信号发生器需要将来自上位机的图像数据进行存储,为了保证不同相机对图像数据大小的要求,FLASH使用了一款2Gbit容量的FLASH。为了加速图像数据的读取,在FLASH和FPGA之间增加了DDR2作为数据的缓存,同样选择了一款的2Gbit容量的DDR2,该器件标准工作频率为200MHz,数据传输速率达到400Mbit/s。图像处理电路的核心器件FPGA选用XILINX公司一款Virtex-5系列的FPGA,拥有丰富的可编程门阵列资源和庞大的I/O(输入/输出)接口,可用I/O接口数量达到640个,时钟管理模块(CMT)有6个,包括2个数字时钟管理单元(DCM)和1个锁相环(PLL),合计共12个DCM和6个PLL,可以单独分开使用也可以联合使用,能够产生复杂的控制逻辑,适合高速的时序控制和大规模的并行处理[10]。

(2)时序设计

如图4所示,图像处理电路时序部分设计了5个模块:通讯接口模块、指令控制模块、时钟同步信号产生模块、遥测数据输出模块和数据处理模块。通讯接口模块集成了UART接口、双向通讯接口和时钟同步接口等通讯接口;指令控制模块负责完成FPGA和上位机之间的交互,并且对FPGA内部各个功能模块进行配置;时钟同步信号产生模块负责FPGA内部时钟和各种同步信号的产生;遥测数据输出模块是为了完成转发图像数据的辅助信息以及各种遥测数据所预留的功能模块;最后一个模块是数据处理模块,负责CCD图像数据的接收和处理,完成级数曝光、噪声叠加和编码映射等处理,并且实现复位脉冲数据、基准电平数据和有效图像数据拼接功能。

图4 图像处理电路时序设计框图Fig.4 Block diagram of image processing circuit tim ing design

数据处理模块是时序设计的核心模块,分为数据接收单元和数据处理单元。如图5所示,数据接收单元由FLASH控制和DDR2控制两个部分组成,负责接收和存储外部的图像数据,主要实现数据接收、高速缓存的写入和输出,供给后级数据处理单元处理。数据处理单元由随机噪声叠加、曝光级数累加、像元累加、固有噪声叠加、编码映射和数据拼接共6个部分组成,主要实现数据格式量化、随机噪声生成与叠加、级数累加、相邻像元合成累加、固有噪声叠加、编码映射以及数据拼接和输出到数模转换电路。

图5 数据处理模块结构Fig.5 Block diagram of data processing module

2.2 数模转换电路

数模转换电路负责完成灰度图像数据从数字信号到模拟信号的转换,数模转换芯片选用DAC5662,其最高的数据更新速率达200Mbit/s,电路输出结构为高阻差分电流输出,该芯片的满量程的输出电流可控,范围为2~20mA。芯片采用差分输出方式可以消除所有的偶次谐波,最大程度上减小信号噪声和电磁干扰[11-12]。数模转换电路如图6所示。

图6 数模转换电路示意Fig.6 Sketchmap of digital-to-analog conversion circuit

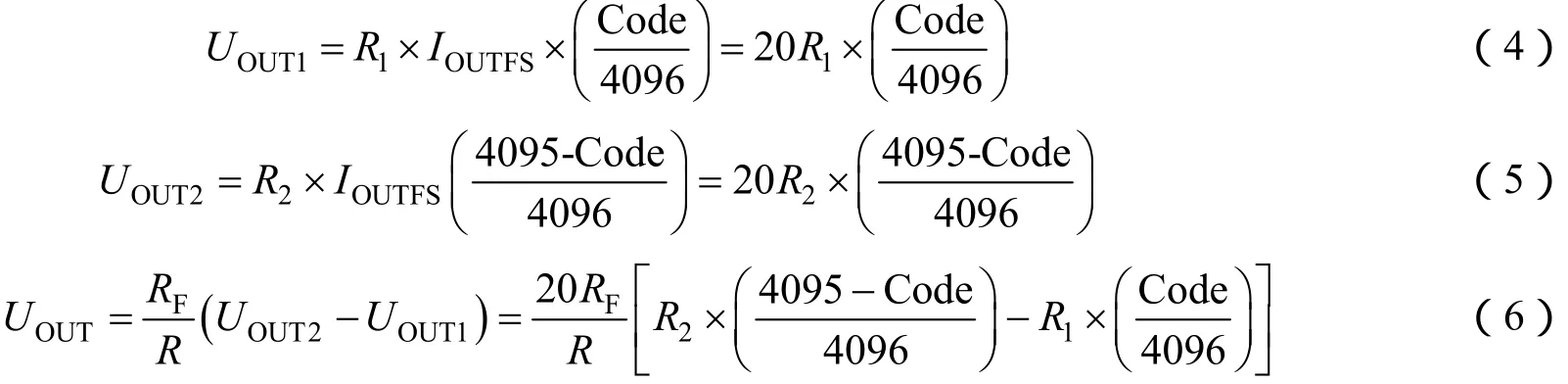

根据DAC5662的芯片资料[13],双通道输出电流参考公式如下:

式(1)中UREF是DAC5662内部+1.2V的基准电压,RSET是外部配置电阻,通过该电阻来调节DAC5662的满量程输出电流,本系统将电阻RSET都设置为2kΩ。根据式(1),得到满量程输出电流IOUTFS约为20mA。根据式(2)和(3)可知,输出的电流值除了和IOUTFS有关,还与芯片输入数字码Code有关。本系统通过对地电阻来实现DAC5662输出电流信号到电压信号的转换。根据式(4)和(5),R1和R2的选取决定了芯片DAC5662输出电压的大小。运放A1构成了差分比例运算电路,为保证运放输入端的平衡条件,选取同相输入端和反相输入端的外接电阻对称,由此得到运放输出电压(mV)和图像Code码的对应关系(如式(6)所示),其中反馈电阻RF和R等值,为了满足模拟信号最大输出电压范围(2V)的要求,R1和R2取值 50Ω。

根据式(6),当 Code=0,UOUT=1V;当 Code=1023,UOUT=0.5V;当 Code=4095,UOUT=–1V。根据图像Code码和输出电压的对应关系,图像处理电路负责把0~4095的图像码映射到1024~4095中(对应电压幅值0.5~–1V),使CCD的有用信号幅值范围为–1~0.5V,复位过冲信号幅值范围为0.5~1V,满足设计要求。

2.3 模拟信号滤波电路

为了提高输出模拟信号精度,降低电路中的高频噪声,在发生器模拟信号输出端采用了二阶低通滤波电路(如图7所示)。该电路既引入了负反馈,又引入了正反馈,其中负反馈决定了电路的放大倍数,而合适的正反馈既可以获得适合系统的中心频率,又不会因为正反馈过强而产生自激振荡。通过正向输入端阻容的选取,系统可以得到合适的–3dB截止频率和平坦的幅频曲线[14-15]。电路选取了R3=R4=51Ω、C1=10pF、C2=22pF,经过仿真分析,–3dB截止频率为132.9MHz,具有平坦的幅频曲线。

图7 二阶低通滤波电路Fig.7 Second-order low-pass filter circuit

3 系统的测试

3.1 测试平台

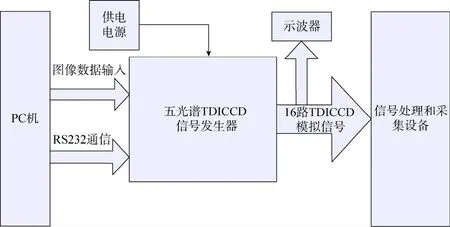

为了测试五光谱TDICCD模拟信号发生器系统,搭建了一个测试平台(如图8所示),包括PC机、供电电源、示波器、五光谱TDICCD信号发生器以及信号处理和采集设备。

图8 系统测试平台Fig.8 Platform of system testing

3.2 信号波形

通过测试平台得到五光谱TDICCD信号发生器的输出波形,如图9所示,该图为像元时钟20MHz情况下固定灰度值(图像码Code=3071)系统输出的TDICCD波形。本文从幅度参数和时间参数两个方面给出了输出波形的实测结果:1)输出有效信号幅度理论值为1V,实测有效信号幅度为0.992V;2)复位脉冲时间T1、基准电平时间T2和信号电平时间T3的设计值分别是1/6个像元时钟(8.333 3ns)、1/3个像元时钟(16.666 7ns)、1/2个像元时钟(25.000 0ns),实测结果T1=8.333 3ns,T2=16.668 3ns,T3=25.001 5ns。依据上述测试结果,本系统输出的模拟TDICCD波形和设计值十分接近,完全满足系统输出波形的设计要求。

图9 系统输出的TDICCD信号波形Fig.9 TDICCD signalwaveform of system output

3.3 信号噪声

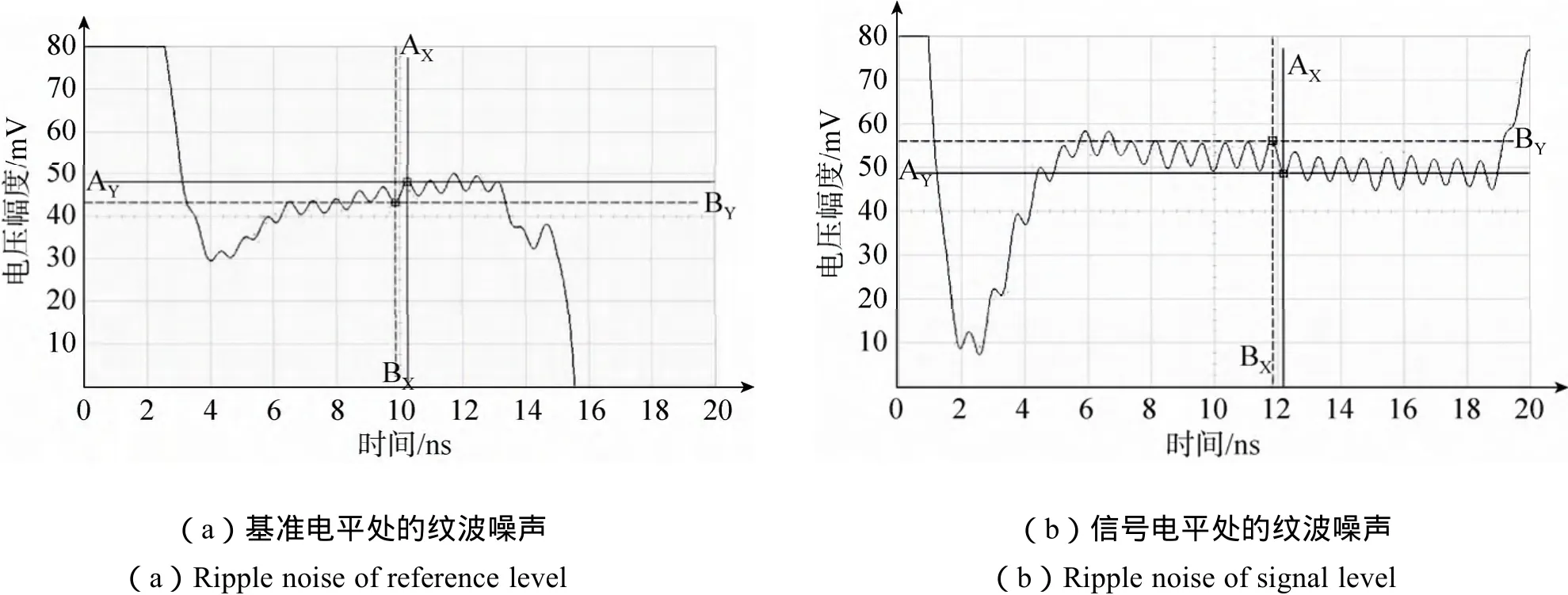

使用示波器对输出模拟信号波形进行了放大测试,得到了复位电平和信号电平处的纹波噪声(如图10所示),基准电平最大纹波噪声为5.8m V(见图10(a)),信号电平处最大纹波噪声为7.5m V(见图10(b))。从测试结果看,输出信号纹波噪声小于10mV,达到了低噪声的要求。

图10 系统输出的TDICCD信号纹波噪声Fig.10 TDICCD signal ripple noise of system output

3.4 输出图像

通过测试平台,系统根据上位机输入的RS232串口指令,产生了相应的图像数据(B区为黑白条纹,P区为渐变图像),并通过数模转换和滤波电路产生相应幅值的16路五光谱TDICCD模拟信号输出,测试平台使用信号处理和采集设备采集了B区黑白条纹图像(如图11(a)所示)和P区渐变图像(如图11(b)所示),根据系统输出图像,计算得到了满量程输出情况下16个通道的信噪比,最高可达69dB。依据上述测试结果,本系统可以根据上位机指令输出指定图像,同时输出图像具有很高的信噪比,完全满足系统对输出图像的设计要求。

图11 系统的16通道输出图像Fig.11 16 channels output image of the system

4 结论

本文对某高分辨率多光谱相机定制的一款五光谱TDICCD的输出特性进行了分析,设计并实现了一种五光谱TDICCD模拟信号发生器系统。通过搭建测试平台,测试了系统的输出波形、纹波噪声和输出图像,测试结果表明:系统输出的模拟五光谱TDICCD波形,频率达到20MHz,纹波噪声小于10mV,同时根据上位机的指令可以输出指定图像,输出图像信噪比最高可达69dB,可以满足遥感相机对五光谱TDICCD模拟信号的要求。目前该发生器已经成功应用到某高分辨率多光谱相机的研发测试中,有效缩短了空间遥感相机的研发测试周期。

(References)

[1] 韩志学,王旭,蔡媛媛,等.一种高速分辨率遥感相机全色/多光谱焦平面电路设计[J].航天返回与遥感,2012,33(4):57-58.HAN Zhixue,WANG Xu,CAIYuanyuan,et al.Design of Focal Plane Circuits of High Speed and High Resolution Remote Sensing Camera[J].Spacecraft Recovery&Remote Sensing,2012,33(4):57-58.(in Chinese)

[2] 郝贤鹏,任建岳.TDICCD相机的低噪声视频处理技术[J].光学精密工程,2008,16(10):1869-1873.HAO Xianpeng,REN Jianyue.Low Noise Video Processing Technique for TDICCD Camera[J].Optics and Precision Engineering.2008,16(10):1869-1873.(in Chinese)

[3]李爱玲,张伯珩,达选福,等.基于CPLD的CCD相机图像信号模拟器的设计[J].微计算机信息,2006,22(2):151-153.LIAiling,ZHANG Boheng,DA Xuanfu,etal.Implementation of CPLD-based Image Signal Simulator for CCD Camera[J].Control&Automation,2006,22(2):151-153.(in Chinese)

[4] 万旻,李涛.TDICCD时序设计在FPGA中的工程实现[J].航天返回与遥感,2006,27(3):34-36.WAN M in,LITao.A Kind of FPGA Engineering Realization of TDICCD Timing Design[J].Spacecraft Recovery&Remote Sensing,2006,27(3):34-36.(in Chinese)

[5] 卢阳,陈向东.基于CPLD的TDI/CCD图像传感器驱动时序设计[J].微计算机信息,2006,22(17):227-229.LU Yang,CHEN Xiangdong.Design of Driving Generator for TDI/CCD Imaging Sensor Based on Complex Programmable Logic Device[J].Control&Automation,2006,22(17):227-229.(in Chinese)

[6] 李云飞,李敏杰,司国良,等.基于FPGA的科学级CCD相机时序发生器的设计[J].微计算机信息,2007,23(5):196-198.LIYunfei,LIM injie,SI Guoliang,et al.The Design of Tim ing Generator of Scientific Grade CCD Camera Based on FPGA[J].Control&Automation,2007,23(5):196-198.(in Chinese)

[7] 宋小龙,张犁,石光明.基于FPGA的高精度TDI-CCD信号发生器的设计[J].电子科技,2007,19(4):1-4.SONG Xiaolong,ZHANG Li,SHIGuangm ing.A High Accuracy TDI-CCD Signal Generator Based on FPGA[J].Electronic Sci&Tech,2007,19(4):1-4.(in Chinese)

[8] James R J.Scientific Charge-Coupled Devices[M].USA:SPIE,2010:22-24.

[9] 黄巧林,金伟其,朱敏.航天TDICCD相机视频信号处理中相关双采样技术的研究[J].航天返回与遥感,2002,23(4):17-25.HUANG Qiaolin,JIN Weiqi,ZHU M in.TDICCD Video Data Sampling Technique for Space Remote Sensing Camera[J].Spacecraft Recovery&Remote Sensing,2002,23(4):17-25.(in Chinese)

[10] Xilinx.Virtex-5 User Guide[EB/OL].//www.xilinx.com

[11] 姜博,阮锦.基于CPLD的CCD信号发生器的研究[J].微计算机信息,2009,25(17):267-269.JIANG Bo,RUAN Jin.Design of CCD Signal Generator Based on CPLD[J].Control&Automation,2009,25(17):267-269.(in Chinese)

[12] 刘杰,牛燕雄,董伟,等.基于FPGA的视频信号发生器设计与应用研究[J].仪器仪表学报,2008,29(3):654-657.LI Jie,NIU Yanxiong,DONGWei,et al.Design and Application of Video Signal Generator Based on FPGA[J].Chinese Journalof Scientific Instrument.2008,29(3):654-657.(in Chinese)

[13] Texas Instruments.DAC5662[EB/OL].//www.ti.com

[14] 曹伟,谭南征.基于TDICCD相机有源低通滤波器的优化研究[J].航天返回与遥感,2005,26(2):29-33.CAOWei,TAN Nanzheng.Optim ization Research of Active Low-pass Filter of TDICCD Camera[J].Spacecraft Recovery&Remote Sensing,2005,26(2):29-33.(in Chinese)

[15] 裴晓旭,鞠浩,张建勋.CCD读出电路中数字补偿式一阶模拟滤波器设计[J].光电工程,2008,35(6):135-140.PEIXiaoxu,JU Hao,ZHANG Jianxun.Digital Compensation First-order Low pass Filter in the CCD Readout Circuit[J].Opto-electronic Engineering,2008,35(6):135-140.(in Chinese)