基于Multisim软件的首信号鉴别电路设计

2014-01-20李鹏

李鹏

(烟台职业学院电子工程系,山东烟台264670)

基于Multisim软件的首信号鉴别电路设计

李鹏

(烟台职业学院电子工程系,山东烟台264670)

首信号鉴别电路应用广泛,文中给出了一种包括声光提示、数码显示功能的首信号鉴别电路完整设计方案,包括其设计框图,各部分设计的原理和仿真,并将整体电路绘制在Multisim10中进行仿真运行测试,获得正确的设计方案。

首信号;Multisim;JK触发器;鉴别;屏蔽;仿真

首信号鉴别电路可以用在需要鉴别第一输入信号并屏蔽其他后续输入信号的场合,如竞赛抢答器、反应能力测试器、抢跑测试器等。在首信号鉴别电路上,可以附加指示灯、声响报警、数字显示等功能,使之更具有实用性。用边沿触发的D触发器或JK触发器设计首信号鉴别电路的主电路,是比较高效的方案。

为便于测试电路的功能,更清楚的阐述其设计思路和电路设计原理,本设计采用Multisim 10这款仿真软件来实现。Multisim 10是美国 NI公司在EWB(Electrical Workbench)这款EDA软件的基础上升级而来的功能强大的windows操作系统下的电路设计和仿真软件,它已经广泛的应用到电子电路的教学中和电路设计人员的设计仿真、测试中[1]。

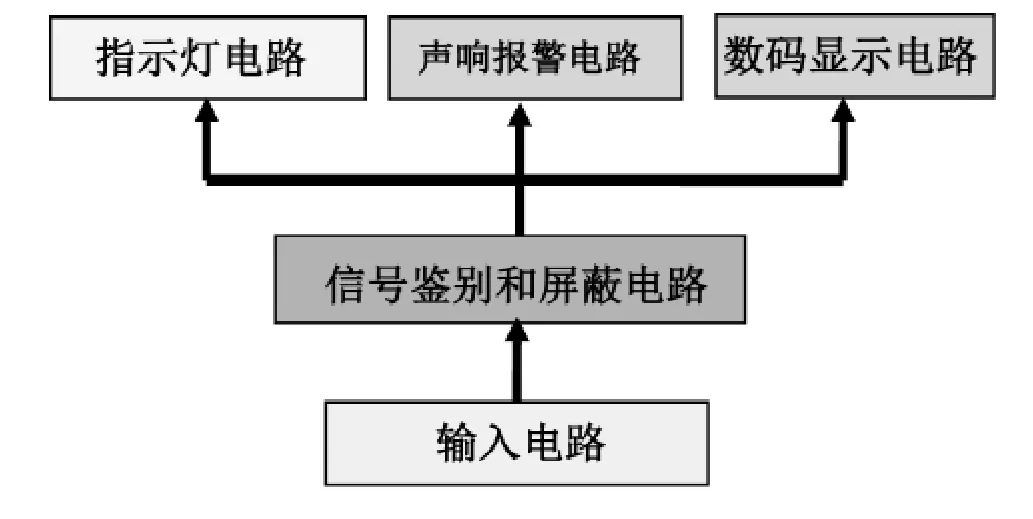

1 电路设计框图

功能较全面的首信号鉴别电路的结构框图如图1所示,它包括输入电路、信号鉴别和屏蔽电路、输出外围电路(指示灯、报警电路、数码显示电路),其中信号鉴别和屏蔽电路是主电路,功能是接收输入电路送来的信号并鉴别出第一输入信号,对之后输入的信号进行屏蔽[2]。输入电路的形式需要根据应用场合来确定,如智力竞赛抢答中,输入电路可以是按钮,反应能力测试中可以是某种传感器,也可以是某种按钮。

图1 首信号鉴别电路结构框图

2 各部分电路的设计与 Multisim仿真

本设计以四人知识竞赛抢答器电路为实例,详细说明首信号鉴别电路的设计与在Multisim中的实现。市面上边沿D触发器和JK触发器都很多,所以设计中选用二者均可。本文选用带有异步复位端的下降沿触发的双JK触发器74LS73进行设计。

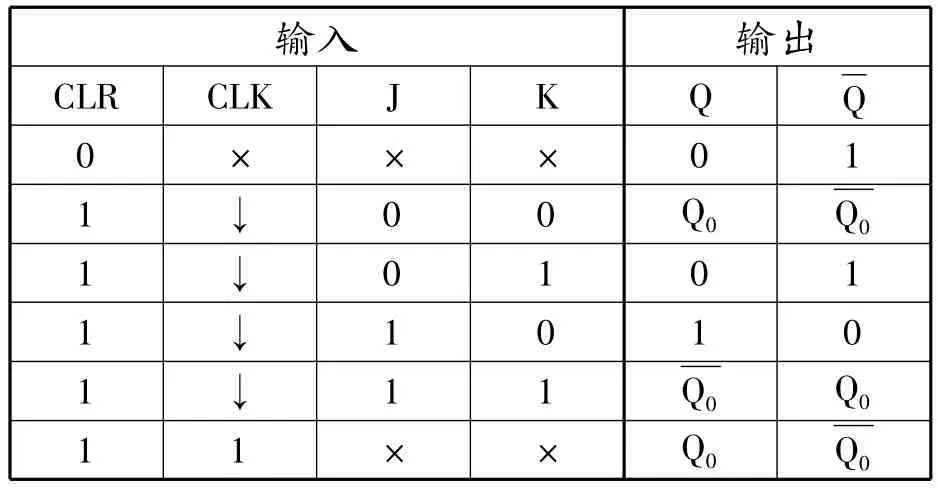

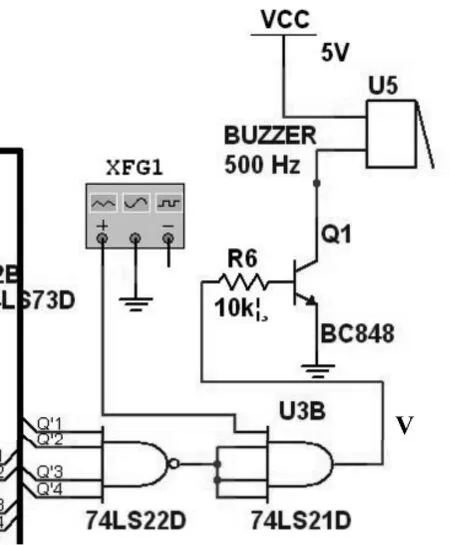

2.1 双JK触发器的基本功能

双JK触发器74LS73的功能表如表1所示,内部逻辑结构及引脚排列如图2所示[3]。

表1 74LS73的功能表

由表1和图2可以看出:

①74LS73中JK触发器的时钟端CLK是下降沿有效。

②数据清除端CLR是低电平有效的异步清零功能端。

③在CLR为高电平情况下,在时钟CLK的下降沿到来时,如J=K=0,输出Q保持不变;如J=1,K =0,输出Q被置位为1;如J=0,K=1,输出Q被复位为0;如J=1,K=1,输出Q将求反。

图2 74LS73的内部逻辑结构及引脚图

④当时钟CLK没有下降沿时,JK触发器将保持不变。

2.2 按键输入部分的设计

输入电路包括主持人按键和四个队的抢答键,主持人按键起到复位的作用,使得亮起的指示灯灭掉,显示队号的数码管显示0或灭掉。74LS73上的异步复位端是低电平有效的,所以主持人按键常态是高电平,按下是低电平,如图3(a)所示。

图3 首信号鉴别电路输入部分

抢答键按下,会使对应的触发器置位,并能封锁其他队的按键信号和自己队再次输入的信号,避免二次按下引起的报警现象。首信号识别后,封锁后续信号的电路实现,可从两个方面来设计:一是封锁信号使触发器进入保持状态,抢答按键作为CLK信号使用;二是抢答键输入的信号作为J或K信号,CP信号在主持人复位之前不再有下降沿,也使触发器保持状态不变。本设计中采用第一种做法,需要在按下抢答键时产生一个下降沿,常态也是高电平,如图3(b)所示。

2.3 首信号鉴别和屏蔽电路设计与仿真

首信号鉴别和屏蔽电路设计的基本思路是:在主持人按复位键后触发器被复位变成0,要识别输入的抢答信号,触发器就得翻转为输出1,前面已经确定抢答信号作为CLK使用,抢答按键送来的下降沿使触发器翻转,触发器的输入应该是J=K=1。当有人第一个按下抢答按钮后,触发器要变成保持状态,则J=K=0屏蔽再次输入的抢答信号。所以J和K不应该是恒定的1或者0,应该是受到屏蔽电路的控制的,并且屏蔽电路的输出应该和触发器的输出有关,这样可以用Q或作为屏蔽电路的输入,屏蔽电路的输出再送到J和K上。在抢答前,触发器输入端J=K=1,输出端Q=0,=1,有人抢答后,Q=1=0,输入变成J=K=0,因此可以使用Q作为屏蔽电路的输入。本设计中有四个输入,需要四个触发器,每个触发器的工作原理是相同的,所以可将四个触发器的相与送至J和K上,如图4所示,是在Multisim 10中绘制的电路设计原理图,仿真测试的结果完全符合要求。

图4 首信号鉴别电路(四路抢答器)的设计图

在图4中,用四输入与门74LS21实现屏蔽电路,其输出屏蔽信号的表达式是:

抢答前,与门的四个输入来自四个触发器的Q =1,与门输出1送至四个触发器的J和K端;在抢答后,例如J1先抢答,给第一个触发器U1A的CLK一个下降沿,使得U1A的状态翻转=0,则与门输出Y=0,将四个触发器的输入J、K都变成0,即便再有CLK下降沿输入,触发器输出端也是保持不变。

2.4 指示灯部分设计

设计中用LED充当指示灯,如图4中每个LED的阳极串接500Ω限流电阻后接5V电源正极,阴极接触发器的,当=1时,灯不亮,当=0时,灯亮。例如在J1首先抢答后,U1A触发器的=0,对应的LED1亮,其他触发器保持不变,灯不亮。由此,可以通过LED灯的指示清楚获得第一信号的来源。

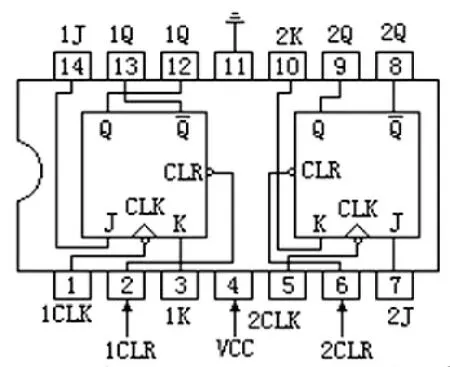

2.5 声音报警电路设计

本设计中用蜂鸣器作为发声元件,如图5所示。用JK触发器输出端控制三极管BC848基极,抢答时给基极500HZ的脉冲信号驱动蜂鸣器发声。所以基极的控制信号表达式如下式:

与式①比较可得:

图5中电路是按照式②实现的,图中与门U3B和图4中的U3A在同一个集成块上,不必再增加两输入端的与门。实践中也可以按照式③来实现,将Y送入非门求反后和500HZ脉冲信号送入与门U3B,两种做法在实践中可以灵活选用。

图5 发声电路原理图

2.6 数码显示电路

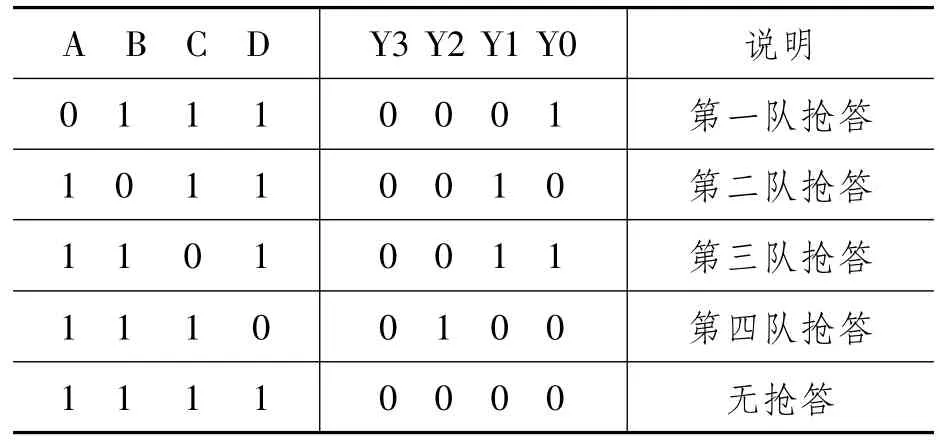

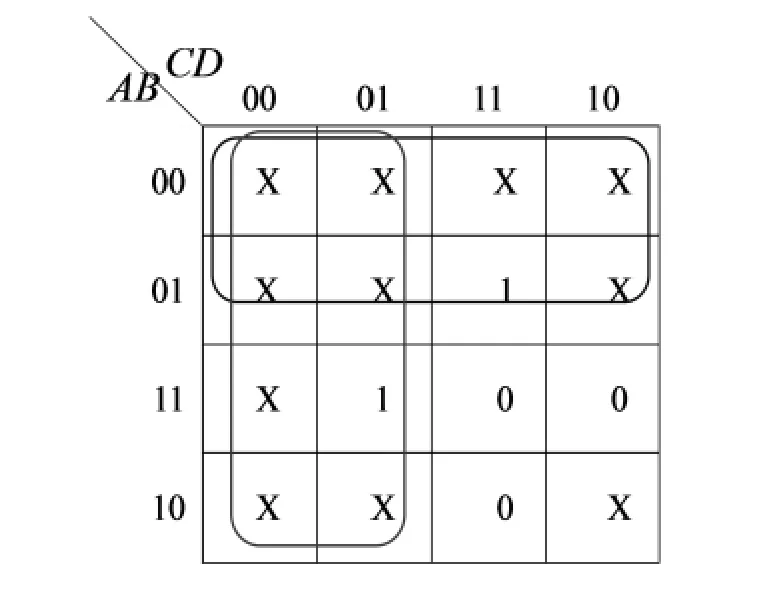

在首信号鉴别电路中可以加入数码显示电路,当鉴别出第一信号之后,能显示出第一信号的来源,在抢答器电路中,可以显示出第一抢答的队号。为此,可以设计一个由JK触发器的输出端逻辑状态到8421BCD码的转换电路来驱动数码管。为表述方便,用A、B、C、D分别表示,用Y3、Y2、 Y1、Y0分别代表8421BCD码的四位,可以画出转换电路的真值表如表2所示。显然,在四人抢答器电路中只会出现5种情况,其他不出现的作为无关项来处理,采用卡诺图进行化简。图6是Y0的卡诺图。

表2 数码显示电路真值表

图6 Y0的卡诺图

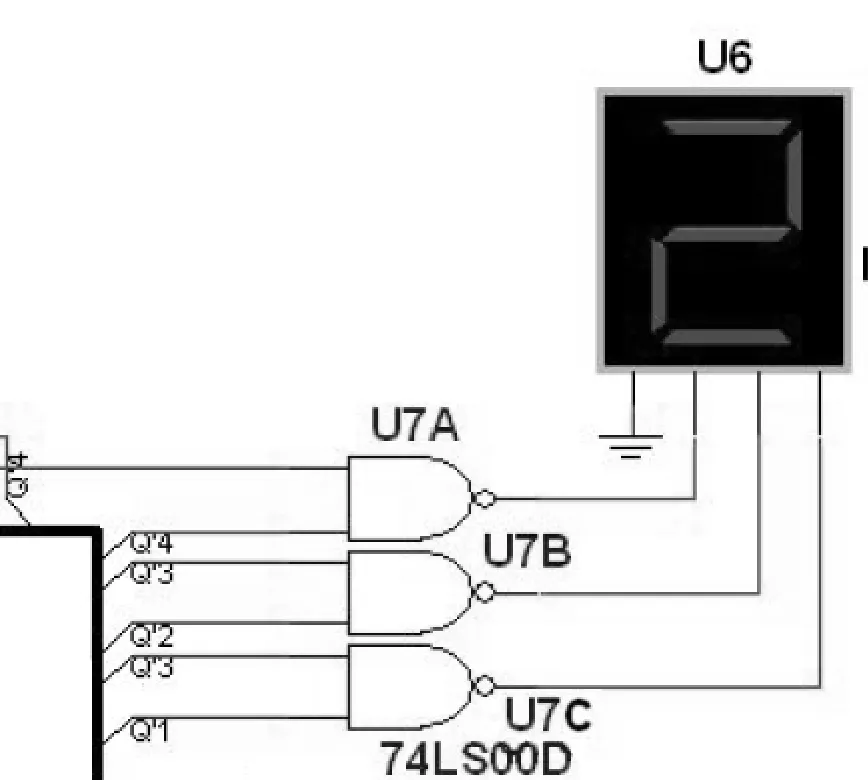

由式④画出代码转化电路如图7所示。

图7 数码显示部分电路

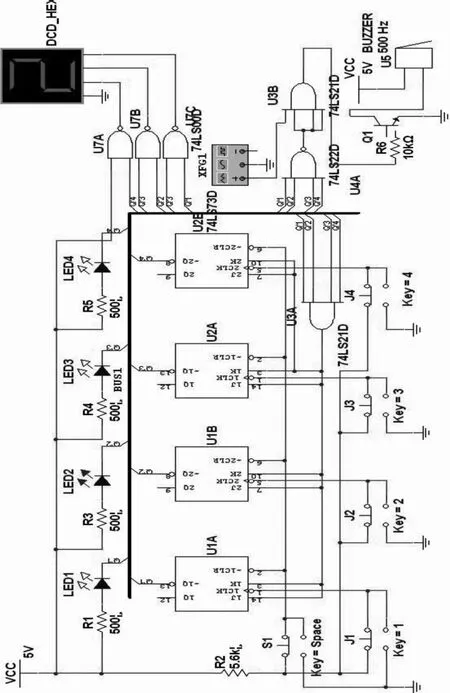

3 完整电路与结论

以四人竞赛抢答器为实例的首信号鉴别电路的完整电路设计如图8所示。该电路在Multisim中进行功能仿真,各项功能完全正常,电路工作中电路参数稳定,原理设计完全正确。

图8 完整的首信号鉴别电路图

[1]summao.Multisim10的使用教程[EB/OL].2010-06-07,http://wenku.baidu.com/link url=SX-qOEuZo4Ey0fQ2eXSQId0QHKbEZAgpfLrd_BT2-gH9jpWcG4BbFM-tkS7VsVjbV2ewE6N4T439lGwaLT H93F-h4cbNvfahyrDhq_xvQWEC.

[2]郑景华.CMOS电路的第一信号鉴别器[J].河南大学大学学报(自然科学版),1995(1).

[3]杨志忠.数字电子技术(第三版)[M].北京:高等教育出版社,2008.

(责任编辑 侯中岩)

TN702

B

1673-5382(2014)02-0071-05

2014-03-20

李鹏(1974-),男,山东平邑县人,烟台职业学院讲师,硕士.