数字可调中频噪声源设计

2014-01-16马路石立国王竹刚

马路,石立国,王竹刚

(中国科学院国家空间科学中心 北京 100190)

高斯白噪声信号源是一种必不可少的通信信道模拟器。产生高斯白噪声的途径主要有物理和数字两种方式。物理噪声源虽然精度较高,但是不好控制。数字方式简单快捷,便于控制参数。数字高斯白噪声的产生方式很多,一般都是先产生均匀分布随机数,再通过一定的转换获得高斯随机数。

文献[1]利用Wallace算法生成均匀分布随机数,通过查找表获得高斯白噪声。文献[2]利用Tausworthe算法产生均匀分布随机数,通过box-muller方法获得高斯白噪声。文献[5]利用CASR和LFSR组合的方法获得均匀分布随机数,通过函数映射法获得高斯白噪声。文献[6]利用m序列产生均匀分布随机数,通过函数映射法获得高斯白噪声。

为了获得长周期的均匀分布随机数,本文采用了文献[2-3]提出的产生均匀分布随机数的方法。由于产生的是32位的均匀分布随机数,如果采用文献[1]的查找表法,则将耗费很多硬件资源,而文献[3]的box-muller方法含有不便于FPGA实现的超越函数,为此采用文献[5-6]提出的函数映射法来获得基带高斯白噪声。

调用ISE14.1中的FIRIP核,配置IP核为多系数(multiplecoefficent)模式,通过载入不同的滤波器系数获得所需中心频率和带宽的中频噪声。

配置OSERDES2在DDR模式下,把KC705开发板产生的中频噪声通过LVDS接口输出给AD9739-R2-EBZ开发板。

1 均匀分布随机数产生算法

均匀分布随机数的好坏直接影响所得到的高斯分布随机数的性能。均匀分布随机数产生器对高斯分布随机数的影响主要有[2]:

1)周期。均匀分布随机数的周期决定了高斯分布随机数的周期。

2)位宽。均匀分布随机数的位宽决定了可以产生的高斯随机数的范围和高斯随机数的分辨率。

3)速度。产生均匀分布随机数的速度不能低于高斯随机数产生算法的硬件工作速度。

针对以上的问题。文中采用了一种改进的Combined Tausworthe方法[2-3],这种基于矩阵思想设计的转换逻辑的硬件结构,提高了均匀分布随机数的产生速度。

1.1 Combined Tausworthe算法

为了产生周期足够长的均匀分布随机数,文章采用了Combined Tausworthe[3]算法。

Combined Tausworthe随机数生成器是由若干个Tausworthe随机数生成器组合而成,每个Tausworthe随机数生成器产生随机数的公式如下

其中,s和L是正整数,s是跳变步长,L是随机数的输出位宽。xj,ns+i-1是一个随机数,满足线性递归模二和公式

其对应的特征多项式为

当 P(z)为本原多项式时,输出序列有最大周期:2k-1。P(z)通常取三项

且满足:

0<2q<k,0<s≤k-q<k≤L,gcd(s,2k-1)=1

由J个Tausworthe随机数生成器构成的Combined Tausworthe随机数生成器产生的(0,1)区间内均匀分布的随机数为

其中,xj,ns1+i-1是第j个Tausworthe随机数生成器的输出。

文献[4]提供了Tausworthe随机数生成器一种快速算法思想:令r=k-q。假设A,B,C的长度都是 L,且 A的初始值为s~n-1=(x(n-1)s,…,x(n-1)s+L-1),C 是一个掩码(1,1,…,1k,0,0,…,0L-k),它是由 k 个 1 和 L-k 个 0 组成。 开始,令 n=1,A:s~0=(x0,…,xL-1),第二步之后,B=(xk,…,xr+L-1,xL-q,…,xL-1)。 第五步之后,A=(xs,…,xr-1,01,…,0s+L-k),即含有 s+L-k 个 0,而 B=(01,…,0k-s,xk,…,xs+L-1)。 第六步之后,A=s~1。 此即为线性递归模二和算法。经过一系列的移位和逻辑操作,旧的随机数更新产生新的随机数[3]。

1.B←q-bit left-shift of A;

2.B←A⊕B

3.B←(k-s)-bit right-shift of B;

4.A←A&C;

5.A←s-bit left-shift of A;

6.A←A⊕B

采用文献[4]提供的算法可以很容易地在FPGA上实现。然而,这种操作耗费的资源比较多,而且有冗余的步骤,为此文章引用了文献[2]的改进型的Combined Tausworthe算法。这种改进型算法耗费的资源少,且非常适合在FPGA上实现。

1.2 改进型Combined Tausworthe算法

在改进型算法中,每个Tausworthe随机数生成器由一个L位的寄存器和转换逻辑A'构成,寄存器中的每一位数据满足式(2)的约束关系。转换逻辑根据这一关系结合式(1)求出下一时刻的随机数[2-3]。

式(2)的递推关系用矩阵表示为

其中,Xj,n是当前时刻的 L 位寄存器状态,Xj,n+1是下一时刻的状态。A为转换矩阵

其中,C1×L是特征多项式 P(z)的系数向量,I(L-1)(L-1)是一个单位矩阵,0(L-1)×1是一个零向量。

一次更新s位信息的转换关系如下

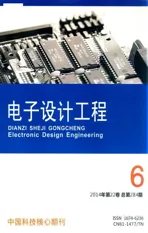

最后,由J个这种结构的Tausworthe随机数生成器经过异或操作得到Combined Tausworthe随机数生成器。器硬件结构如图1。

J个Tausworthe随机数发生器的构成的Combined Tausworthe周期为[3]:

根据文献[1]的周期搜索结果,表1列出了满足“ME(Maximally Equidistributed)条件”的 3 种参数组合(kj,qj,sj)。

图1 Combined Tausworthe随机数生成器结构Fig.1 Structure of combined Tausworhthe random number generator

2 高斯分布随机数生成算法

随机过程理论:给定任何随机变量X的累积分布函数F(X),则 Y=F(X)是在(0,1)区间内均匀分布的随机变量,且与X的分布特征无关。

可以把Y看成是均匀分布,X看成是高斯分布,所以可以通过概率的方法可以获得均匀分布与高斯分布之间的映射关系。

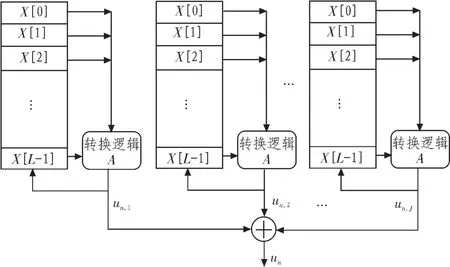

2.1 均匀分布与高斯分布之间的映射关系

设 X 服从[1,232-1]区间内的均匀分布;Y 服从(0,1)的标准正态分布。考虑到FPGA硬件实现,Y仅在[-4,4]之间取值。Y的概率密度为[5-6]:

则X→Y的映射算法如下:

1)计算每个高斯随机数的概率。 对 f(y)在[-4,4]之间0.02 等间隔采样 401 个点,表示为 zi(i=1,…,401),其中 zi=f(yi),sum(z)=z1+z2+…+z401。 重新计算 401 个点的概率为:f(zi)=zi/sum(z)。

2)计算每个zi对应的均匀分布随机数的个数。高斯分布随机数总个数。等于均匀分布随机数的总个数L=232,则N(zi)=f(zi)×L即是每个高斯随机数对应的均匀随机数的个数。

3)计算横坐标。 每个高斯分布随机数 zi(i=1,…,401)对应的横坐标为:前一个zi-1对应的横坐标位置Xi-1加上zi取值个数N(zi-1)-1。从第一个算起,则z1对应横坐标上的X1点,z2对应横坐标上的X1+N(X1)-1点,以此类推,zi对应横坐标上的 Xi-1+N(Xi-1)-1点,一共 401个对应点。

4)绘制映射曲线。 以 zi[-4,4]为纵坐标,以 Xi-1+N(Xi-1)-1为横坐标绘制均匀分布到高斯分布的映射曲线,如图2。

图2 均匀分布到高斯分布映射曲线Fig.2 Mapping curve of uniform distribution to Gaussian distribution

2.2 折线逼近法

如果把3.1中的映射关系全部存入FPGA的ROM中,需要的空间大小为232-1=429 496 729 5,这是不可实现的。由于映射曲线在很大区间上表现为线性关系,所以可以用斜率不同的折线段分段逼近关系曲线。在一定精度的要求下,这种方法简单易行,占用的硬件资源少,而且运算速度很快,适合在FPGA中实现。图3是20段折线段逼近法得到的拟合关系曲线。

图3 20段折线逼近映射曲线Fig.3 Mapping curve with 20 section broken line

2.3 FIR设计

滤波器的设计可以采用XILINX自带的FIR IP核。要实现中心频率和带宽可调,需要把该IP核配置成多系数(multiple-coefficent)模式。这样可以使用MATLAB的fdatool工具生成一系列对应的滤波器系数,各组系数所采用的滤波器阶数必须相同。把这一系列系数存在一个.coe文件中,通过IP核编辑界面将该文件导入IP核,同时设置“coefficient set”为对应的滤波器组数。

本文使用了16组滤波器,每组滤波器都是200阶,对应一个中心频率和一个带宽。通过filter_sel端口来控制选通对应的滤波器。对应的滤波器框图如图4所示。相应的系数组织形式如图5所示。

图4 重载系数FIR滤波器Fig.4 Overload coefficient filter

图5 FIR系数组织形式Fig.5 Coefficients organization form

3 硬件实现

3.1 高斯白噪声的硬件实现

开发环境采用ISE14.1,开发板选用Kintex-7 FPGA KC705 Evaluation Kit,器件选用 XC7K325T-2FFG900,编程语言为VHDL。其硬件实现如图6。

高斯白噪声发生器包括两个部分:均匀分布随机数发生器模块和均匀分布到高斯分布的映射模块。

模块中信号说明:point代表折线段的起点的横坐标,point_value代表折线段起点的纵坐标,slope代表折线段的斜率。

算法流程:时钟的上升沿,均匀分布随机数发生器产生一个随机数X,该随机数随即被送入一个比较器。在比较器中,随机数X和20段折线的起点值point比较。当确定该随机数的取值范围后,折线逼近法得到相应的高斯随机数:

gauss=(X-point)×slope+poin_value_delay

其中point_value_delay是point_value的延时,因为前面的乘法运算有延时。

图6 基带高斯白噪声FPGA结构Fig.6 FPGA structure of baseband Gaussian noise

3.2 FPGA与AD9739的LVDS接口

本设计中采用的DA为ADI公司的AD9739芯片,FPGA和DA之间的接口采用的是LVDS电平接口。AD9739包括两个14位复用低压差分信号(LVDS)输入端口,该器件接受1/4DAC刷新速率的时钟,在时钟上升沿和下降沿均触发转换。输入数据速率为1/2时钟速率。本设计中时钟信号DCI_P/DCI_N为2.4G,AD9739的工作时钟由安捷伦的信号发生器提供。其中DCO_P/DCO_N输出作为FPGA的系统时钟,其频率为600 MHz。为保证FPGA生成的数据传到AD9739接口端与DCI_P/DCI_N时钟相位对齐,时钟产生方式必须同数据产生方式相同,均由OSERDES产生。FPGA与AD9739的接口设计如图7所示[7-10。

图7 接口结构设计Fig.7 Interface structure

3.3 测试结果

AD9739-R2-EZB开发板的2.4G系统时钟由Aglient信号发生器提供,DA出来的中频噪声频谱由Aglient的频谱仪来分析。

图8是系统产生的70 M中心频率,20 M带宽的中频噪声的频谱。由图可知,产生的中频噪声带内平坦度小于1 dBm,带外衰减大于60 dBm,效果非常好。

图8 噪声源频谱图Fig.8 Spectrogram of Gaussian noise

4 结 论

文章采用Combined Tausworthe方法产生长周期的均匀分布随机数,通过曲线拟合的方法实现均匀分布到高斯分布的映射。利用可重载系数的FTR滤波器实现了参数可调的中频噪声源。通过安捷伦频谱仪测试,该可调中频噪声源性能满足要求。

[1]黄本雄,侯洁,胡海.高斯白噪声发生器在FPGA中的实现[J].微计算机信息,2007,10(11):55-58.HUANG Ben-xiong,HOU Jie,HU Hai.The realization of gaussiannoisegeneratorin FPGA[J].Microcomputer Information,2007,10(11):55-58.

[2]谷晓枕,张民选.一种基于FPGA的高斯随机数生成器的设计与实现[J].计算机学报,2011,34(1):165-173.GU Xiao-chen,ZHANGMin-xuan.Design and implementation of a FPGA based gaussian random number generator[J].Chinese Journal of Computers,2011,34(1):165-173.

[3]谷晓枕,张民选.多输出外部反馈型LFSR均匀分布随机数生成器的分析与设计[J].计算机工程与科学,2009,31(A1):80-83.GU Xiao-zhen,ZHANG Min-xuan.Multi-output fibonacci type LFSR based uniform random number generator:Design and Analysis.Computer Engineering and Science,2009,31(A1):80-83.

[4]Pierre L E.Maximally equidistributed combined tausworthe[J].Mathematics of Computation,1996,65(213):203-213.

[5]艾余雄,寇艳红.一种基于FPGA的高斯白噪声发生器的设计与实现[J].遥测遥控,2009,30(6):36-40.AI Yu-xiong,KOU Yan-hong.Design and implementation of gaussian noise generator by FPGA[J].Journal of Telemetry,Tracking and Command,2009,30(6):36-40.

[6]管宇,徐雷,徐建中.用FPGA产生高斯白噪声序列的一种快速方法[J].电子元器件应用,2008,23(7-2):165-167.GUAN Yu,XU Lei,XU Jian-zhong.A method to generate gaussian sequences by FPGA[J].Electronic Component&Device Application,2008,23(7-2):165-167.

[7]韩庆喜.基于DVB-S标准的射频调制器设计与FPGA实现[D].山东:山东大学电路与系统系,2010.

[8]王猛,吕卫祥.基于高速D/A AD9739的宽带信号产生[J].雷达与对抗,2011,31(4):55-58.WANG Meng,LV Wei-xiang.The high-speed D/A AD9739-based wideband signal generation[J].Radar&ECM, 2011,31(4):55-58.

[9]Marc Defossez.Parallel LVDSHigh-Speed DAC Interface[R].America:XILINX,2012.

[10]程光伟,刘大伟.基于FPGA的异步FIFO的研究和设计[J].工业仪表与自动化装置,2013(2):67-69,75.CHENG Guang-wei,LIU Da-wei.Research and design of asynchronous FIFO based on FPGA[J].Industrial Instrumentation&Automation,2013(2):67-69,75.