高速多通道时域宽带数字波束形成器设计

2014-01-01逄锦昊

逄锦昊,吴 凯,杨 涛,苏 涛

(西安电子科技大学雷达信号处理国家重点实验室, 西安710071)

0 引言

宽带相控阵雷达(Phased Array Radar,PAR)作为宽带雷达和相控阵雷达的结合体,满足了目前高速多目标以及高分辨等苛刻的雷达系统要求[1]。数字阵列雷达(Digital Array Radar,DAR)是一种数字化的PAR,其收、发均采用数字波束形成技术,具有多功能和可重构等特点[2]。DAR将宽带雷达技术应用于各种PAR,提高了雷达目标的距离分辨率、目标跟踪性能以及抗干扰能力[1]。多波束形成技术进一步提高了DAR的检测性能和电子反对抗能力[3]。针对宽带DAR多波束形成对高速大容量数据传输以及高性能实时信号处理技术的需求,目前存在的宽带DAR多波束形成系统主要基于光纤数据传输以及现场可编程门阵列(FPGA)高速并行运算处理平台[4-7]。文献[7]设计的宽带DBF系统可实现200 MHz带宽下,4个通道合成1个波束[1]。文献[7]在相同带宽下,设计了单个宽带数字波束形成模块,可实现16通道同时合成4个波束。

本文针对PAR海量数据传输和计算量大的需求,提出了基于任意时延滤波器(Random Delay Filter,RDF)的宽带数字波束形成算法,并基于该算法设计了一种高速多通道宽带DBF。设计的DBF最大支持48通道,在200 MHz带宽下,若使用全部通道,可同时合成3个波束;若只使用16通道,可同时合成8个波束。通过级联和子阵划分技术[2],本文设计的DBF可用于线阵或面阵等任意形式的大型DAR。

1 基于任意时延滤波器的宽带数字波束形成

1.1 宽带数字波束形成系统结构

宽带DBF的关键是精确补偿各个阵元通道上的信号延时[8-9]。分数延时滤波器的引入有效地解决了宽带数字波束形成中的时间色散问题[1]。基于均匀线阵,图1a)给出了常用的宽带数字波束形成系统结构[1,8-9],每个阵元通道由相应的移相器、数字延迟线和分数时延滤波器组成。移相器用来消除信号载波项带来的相位偏移,数字延迟线和分数时延滤波器用来完成各自所需的整数和分数倍采样时间的延迟。本文设计的RDF可实现图1a)中数字延迟线和分数时延滤波器的功能。移相器只是简单的线性加权,对于单个通道的所有采样点都相同,可以作为比例因子与RDF融合成一步完成,得到图1b)所示的基于RDF的宽带DBF单通道补偿结构。为了论述方便,下文在提及RDF时,均未包含移相器的线性加权。

图1 宽带数字形成系统结构

1.2 任意时延滤波器设计

理想的RDF频率响应由式(1)给出,其中,ω为数字角频率,τ为任意时延。可以看出式(1)表示的滤波器的幅频响应恒为1,群延迟恒定为任意时延常数τ。

由于IIR滤波器具有设计复杂和稳定性差的问题[9],本文采用FIR进行RDF的设计。设FIR滤波器的权向量为 h=[h(0),h(1),…,h(N-1)]T,则其频率响应为

式中:e(f)=〔1,e-j2πf,…,e-j2π(N-1)f〕;f为归一化的数字频率。滤波器权向量的获取,可以通过求解式(3)的最小化问题得到。

式中:Wk为非负加权向量,可以灵活控制各频点受约束的程度;0<f<fu为滤波器设计的频率范围;fu为受约束的频率上限;Hd(f)为期望频率响应,对于本文RDF的设计,由式(1)表示的Hd(f)具有如下形式

在0<f<fu频率范围内,幅频响应恒为1,群延迟τn是n号阵元通道相对参考阵元期望的任意时延量。式(3)中,当norm表示‖·‖2范数时,式(4)表示最小化滤波器频率响应的加权均方误差;当norm表示‖·‖∞时,式(4)表示最小化最大滤波器频率响应的加权误差,该准则下设计的滤波器具有等波纹特性。同时,可以根据具体的设计要求,在该基本优化模型中加入具体的约束,例如,可以让期望频点上的误差范数小于某个值。借助于MATLAB的CVX工具箱,这类凸优化问题容易求得全局最优解。

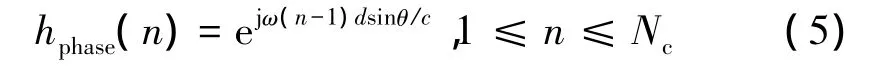

若考虑载频的影响,每个阵元通道还需要借助移相器进行相位补偿,对于均匀标准线阵,相位补偿因子可以表示为

式中:n为阵元通道索引;d为阵元间距;θ为波束指向;Nc为阵元个数。考虑通道均衡问题,需要设计通道均衡滤波器[7,10],即在每个阵元通道后接入用于消除幅相不一致的FIR滤波器。假设n号阵元后用于通道均衡的滤波器系数向量为hE,则由凸优化问题和相位补偿因子可以得到最终n号阵元通道所需的滤波器系数为

式中:hRDF为由式(3)优化得到的n号阵元通道的滤波器系数;⊗为卷积运算。

1.3 构建大型DAR的子阵划分

对于千量级阵元,考虑到成本、复杂性和尺寸等方面的因素,不可能为每个阵元都添加RDF滤波器。然而,通过子阵划分技术,可以在保证宽带性能的条件下,尽可能的减少所需的时域滤波器的个数[1,11-12]。

子阵划分时,需要正确选取最大子阵尺寸L1,要求子阵的孔径渡越时间小于雷达等效脉冲宽度的一半,即满足

其中,不等式左端为子阵的孔径渡越时间;右端τe=F/B,为雷达等效脉冲宽度,F为加权系数,B为雷达信号带宽。选择子阵时,需要根据式(7)确定最大子阵尺寸。另外,子阵的周期划分会导致宽带栅瓣[12],为了降低栅瓣,需要采用子阵重叠等技术,使子阵的相位中心呈现不规则或随机变化。

2 宽带数字波束形成器设计

基于光纤数据传输和FPGA高速并行运算平台,本文采用高速串行接口和模块化程序结构,设计了基于RDF的宽带DBF。下面将着重介绍该DBF的硬件结构和模块化程序设计。

2.1 数字波束形成器硬件构成

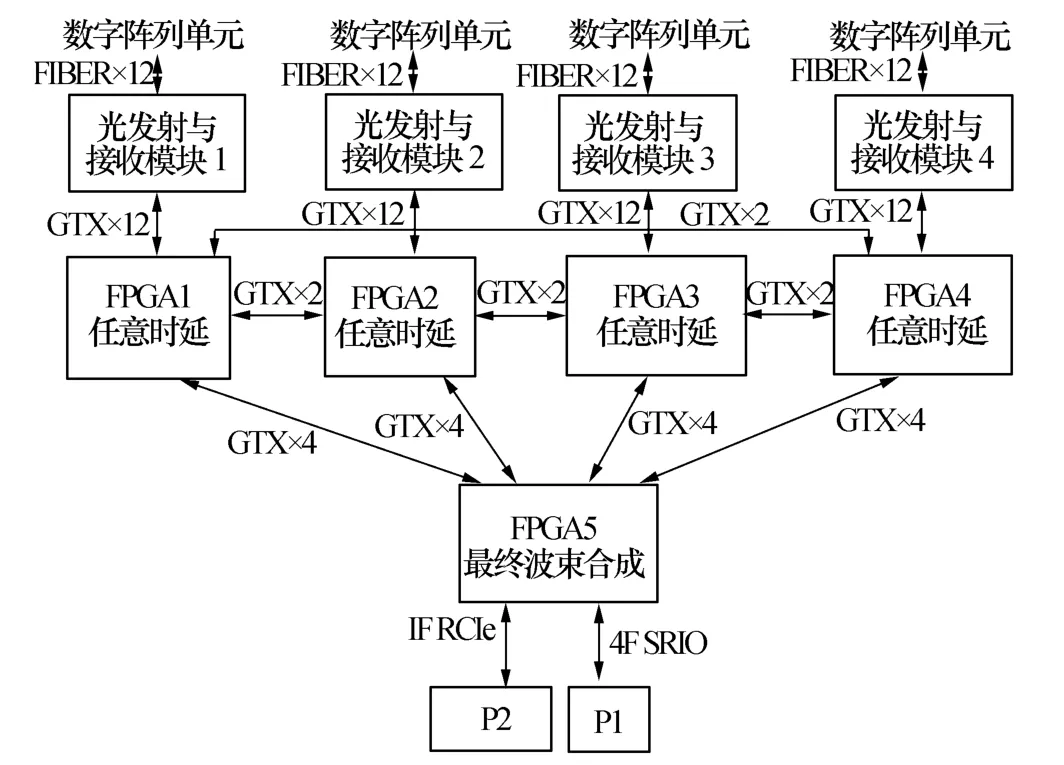

硬件模块采用高速串行接口和FPGA并行计算的设计思路,满足宽带数字波束形成传输量和计算量大的要求;同时基于VPX协议,具有易于集成和数据通信速率高的优点,可适用于多种带宽和数据率的数字波束形成系统。图2给出了硬件模块结构图,包含以下特点:

(1)包含4组12通道并行光发射模块和12通道并行光接收模块,每个模块通过12路GTX与FPGA1~4相连,单路GTX最高传输速率可达5.0 Gb/s。硬件模块通过光纤连接外部的数字阵列单元,数字阵列单元由数字T/R组件、预处理模块和光纤通信接口等组成。

(2)共有5片Xilinx高速FPGA。FPGA1~4采用具有很强的信号处理能力和高速串行互联的SXT系列,包括1 344个DSP48E1,24.7 Mb Block RAM 和20个高速串行GTX接口。FPGA5采用具有最大高速串行互联带宽的HXT系列,具有48个高速串行GTX接口。FPGA之间通过GTX互联成环形和星形结构,星型结构主要用于高速传输部分波束形成结果和权值,环型结构主要用于高速片间传输。

(3)FPGA5有4路4x的SRIO和1路4x的PCIe与VPX接插件连接,前者用于板间高速传输波束形成结果,后者用于上位机实时更新RDF权值。同时,多个波束形成器可通过SRIO互联实现更多通道的波束形成。

图2 硬件模块结构图

2.2 模块化程序设计

FPGA程序采用模块化设计,主要由同步模块、波束合成模块和高速接口模块构成。波束合成模块包括任意时延模块和最终波束合成模块。高速接口模块包括光纤模块、GTX模块、PCIe模块和SRIO模块。这些模块均由FPGA硬核资源实现,通过使用差错控制编码和硬核的差错控制功能,提高传输的可靠性。程序分为实际模式和自检模式。实际模式下,输入外部光纤的信号;自检模式下,输入RAM中存储的测试信号。自检模式可在无雷达回波的情况下检测系统是否正常工作,且在设计初期可对程序进行行为级仿真验证。

同步模块接收外部频综的基准时钟,根据雷达系统的需要,产生定时信号,即脉冲重复时间(PRT)和相干积累时间(CPI),定时信号通过光纤模块发送给数字阵列单元,数字阵列单元将雷达数据送回光纤模块。雷达数据包括协议帧头部分和预处理的雷达数据部分。光纤模块在解析帧头的协议后使用FIFO对预处理的雷达数据进行缓存,在最后一路雷达数据到达后再进行波束合成,实现各路数据同步传输。

图3给出了波束合成模块结构图。波束合成模块包括4个任意延时模块和1个最终波束合成模块。单个任意时延模块通过对12个通道输入数据进行k阶FIR滤波后求和得到时延结果,时延结果在位宽控制后通过GTX模块传输到最终波束合成模块。最终,波束合成模块采用FIFO缓存4路时延结果实现同步,通过对4路时延结果求和得到最终波束合成结果,再经过位宽控制后通过SRIO模块传输到后端处理器。

图3 波束合成模块结构图

PCIe模块采用1.0协议,通过BMD模式传输数据,经测试有效传输带宽可达4.8 Gb/s,当PCIe模块接收上位机的权值时,若FIR滤波器为40阶,48个通道合成一个波束所需的32位复权值量为61.5 kb,波束扫描的加权导向矢量的更新最短时间约为13 μs。

2.3 宽带数字波束形成器特点与性能

宽带数字波束形成器的特点和性能如下:

(1)离线设计延时滤波器系数,具有设计灵活、精度高的特点。

(2)采用单个RDF实现各个通道延时和相位补偿,简化系统结构,节省硬件资源。

(3)最大支持48通道,200 MHz带宽下,若使用全部通道,可同时合成3个波束;若只使用16通道,可同时合成8个波束。

(4)最大光纤传输带宽为240 Gb/s,在300 MHz运算时钟下,定点处理能力可达1 785 GMACs。

(5)能够通过PCIe接口与上位机通信,实现权值实时更新。

(6)采用模块化程序结构,利于时序约束,便于程序维护。

3 性能测试与分析

需要说明的是,采用均匀标准线阵对本文设计的宽带DBF进行仿真测试与分析时,设计的宽带DBF适用于线阵或面阵等任意形式宽带DAR。雷达系统参数如表1所示,可以先计算出每个阵元通道相对于参考阵元的时间延时,从而按照式(4)构造合成每个波束时各个阵元通道上RDF的理想频率响应。

表1 仿真参数

以群延迟均方误差(Group Delay Square Error,GDSE)来衡量RDF的延时性能,给出GDSE的定义如下

借助MATLAB中的函数grpdelay表示求滤波器的群延迟,它的第一个参数表示滤波器的前向加权系数,第二个参数用于IIR滤波器表示后向反馈系数,这里设置为1。对于hRDF,需要根据式(3)的优化结果求取滤波器的群延迟。对于hideal可由式(4)得到以下群延迟响应

待优化频率范围内,理想滤波器的群延迟响应为D+τn。其中,D由滤波器自身延迟引入,τn是合成某一波束时n号阵元相对于参考阵元的时间延时。

图4为合成每个波束各个阵元通道所需的RDF的GDSE分布图。可以看出,所有RDF在[0,0.8]的频率区间内GDSE均在-80 dB以下,随着频率的增加由-100 dB逐渐增加至-80 dB,具有较好的延时性能。

图4 合成每个波束各个阵元通道所需RDF的GSE分布图

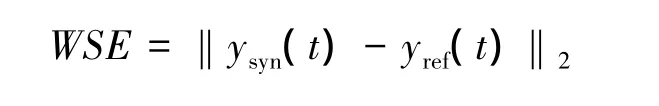

利用上述设计的RDF进行宽带数字波束形成仿真实验。以合成波束相对于参考通道信号的波形均方误差(Waveform Square Error,WSE)为标准衡量宽带DBF性能。假设合成信号的时域形式为ysyn(t),参考通道的时域波形为yref(t),则定义波形的WSE为

图5分别给出了基于MATLAB理想宽带数字波束形成和基于本文宽带DBF合成波束的WSE。可以看出,基于本文宽带DBF合成波束的WSE相对于理想情况增加了不到10 dB,这归因于量化误差与定点操作中的截位和舍入误差。

图5 两种宽带DBF合成波束均方误差

根据表1给定的雷达系统参数,以上仿真分析了48个阵元通道,合成3个波束时合成波束的性能。表2给出该模式下本文设计的宽带DBF中FPGA1~4每个芯片内关键资源的利用情况。同时,给出了本文设计的宽带DBF在16个通道下同时合成8个波束时,FPGA1~4芯片内关键资源的利用情况。

表2 FPGA关键资源的利用

4 结束语

本文提出了基于任意时延滤波器的宽带数字波束形成算法,设计实现了一种高速多通道宽带数字波束形成器。仿真结果表明:本文设计的RDF具有较高的延时精度,将其应用于宽带DBF,经实测验证,最终合成波束的波形误差相对于理想情况增大了仅不到10 dB,整体误差不超过-168 dB。本文宽带数字波束形成器设计时,FPGA内关键资源都留有一定的裕量,为进一步级联通道均衡滤波器提供了条件。

本文初步探索了宽带数字波束形成器的硬件实现,但在工程化运用中还存在其他问题,如各路数据的采样时间点对齐问题等,这将作为笔者下一步的重点研究工作。

[1]王德纯.宽带相控阵雷达[M].北京:国防工业出版社,2010.Wang Dechun.Wideband phased array radar[M].Beijing:National Defense Industry Press,2010.

[2]吴曼青.数字阵列雷达及其进展[J].中国电子科学研究院学报,2006,1(1):11-16.Wu Manqing.The development of digital array radar[J].Journal of CAEIT,2006,1(1):11-16.

[3]张光义.多波束形成技术在相控阵雷达中的应用[J].现代雷达,2007,29(8):1-6.Zhang Guangyi.Application of multi-beam formation technologies in phased array radar[J].Modern Radar,2007,29(8):1-6.

[4]Nuteson T W,Stocker J E,Clark J S,et al.Performance characterization ofFPGA techniquesforcalibration and beamforming in smart antenna applications[J].IEEE Transactions on Microwave Theory and Techniques,2002,50(12):3043-3051.

[5]程 伟,左继章,许悦雷.数字波束形成器的FPGA实现[J].现代雷达,2003,25(5):34-39.Cheng Wei,Zuo Jizhang,Xu Yuelei.FPGA implementations of digital beamformer[J].Modern Radar,2003,25(5):34-39.

[6]Cheung C,Shah R,Parker M.Time delay digital beamforming for wideband pulsed radar implementation[J].IEEE International Symposium on Phased Array Systems&Technology,2013,15(18):448-455.

[7]王 峰,李 婧,刘 俊,等.宽带数字阵列雷达数字波束形成系统研究[J].雷达学报,2013,2(3):312-318.Wang Feng,Li Jing,Liu Jun,et al.System realization of broadband digital beam forming for digital array radar[J].Journal of Radars,2013,2(3):312-318.

[8]刘张林.基于分数时延的宽带数字波束形成技术[J].现代电子技术,2013,36(5):24-26.Liu Zhanglin.Wideband digital array beamforming technology based on fractional delay[J].Modern Electronics Technique,2013,36(5):24-26.

[9]陈舒敏,栾铸征,林 晨.基于全通型分数时延滤波器的数字阵列宽带波束形成[J].舰船电子对抗,2013,36(2):39-43.Chen Shumin,Luan Zhuzheng,Lin Chen.Digital array wideband beam forming based on fractional time delay allpass filter[J].Shipboard Electronic Countermeasure,2013,36(2):39-43.

[10]傅有光,唐 纬,张 倩.通道间幅相差异对旁瓣相消性能的影响与解决方法[J].现代雷达,2000,22(6):50-55.Fu Youguang,Tang Wei,Zhang Qian.Influence of difference of amplitude and phase between channels to SLC performance and its solution method[J].Modern Radar,2000,22(6):50-55.

[11]曹运合,齐飞林,刘 铮.宽带相控阵子阵划分及自适应干扰对消技术[J].中国电子科学研究院学报,2010,5(4):337-343.Cao Yunhe,Qi Feilin,Liu Zheng.Wideband phased array sub-array partition and adaptive interference cancellation technique[J].Journal of CAEIT,2010,5(4):337-343.

[12]程乃平,潘点飞.大型阵列天线子阵划分及栅瓣抑制[J].信号处理,2014,30(5):535-543.Cheng Naiping,Pan Dianfei.Subarray partition method and grating lobe suppression for large array antenna[J].Journal of Signal Processing,2014,30(5):535-543.