一种EAS扫频信号源的设计与实现

2014-01-01牛元海刘太君石志京

牛元海,刘太君,叶 焱,石志京

(宁波大学信息科学与工程学院,浙江宁波315211)

0 引言

在电子商品防盗(Electronic Article Surveillance,EAS)系统中,扫频信号源的扫频方式(频带宽度、频点数和扫频周期等)、扫频信号性能(频率精确度、相位噪声)等指标将直接或间接影响天线发射信号的质量与接收端标签识别的灵敏度、检测率和误码率。

传统EAS信号源多采用普通单片机控制频率合成芯片甚至是用模拟电路产生,频率精确度和可控性较低。设计以TI公司TMS320F28335为主控芯片控制AD9834芯片产生扫频正弦波,无论是控制能力还是数字合成技术都有较大提高。另外,随着标签制作工艺的提高,其谐振频率更加精确,波动范围越来越小,所以信号扫频范围设计为8.0~8.5 MHz,而不再采用一直以来 7.2 ~8.2 MHz的传统频带指标,这样可以减小信号扫频宽度,扫频周期更短,对提高系统的检测率大有助益。

1 工作原理及芯片概述

1.1 扫频信号发生原理

正弦波的一般表示形式为:a(t)=sin(ωt),可见正弦信号是非线性的,但是正弦波的相位是线性变化的:Δphase=ωΔt,继续推理可得:ω =Δphase/Δt=2πf,求得所需发生的频率为:f=Δphase×fMCLK/2π,上式转化一下便可得出频率寄存器的表达式:

式中,FREQREG表示频率字,FOUT是需要输出的正弦波频率,而fMCLK是外部晶振信号频率。

1.2 核心芯片介绍

设计使用的核心芯片有2片:ANALOG DEVICES公司AD9834芯片用于发生扫频信号;德州仪器公司(TI)TMS320F28335芯片用于系统控制和数据的发送。

AD9834是一款75 MHz、低功耗 DDS器件,能够产生高性能正弦波和三角波输出,当时钟速率为1 MHz时最高可实现0.004 Hz的分辨率。AD9834通过一个三线式串行接口写入数据,该串行接口能够以最高40 MHz的时钟速率工作,并且与DSP和其他微控制器标准兼容。

TMS320F28335是TI公司新推出的一款浮点型数字信号处理器,在拥有很好的控制性能的基础上兼备复杂的浮点计算能力,可以节省代码执行时间和存储空间,具有精度高、成本低、功耗小、外设集成度高、数据及程序存储量大和AD转换更快速等优点,为嵌入式工业应用提供了更加优秀的性能和更加简单的软件设计。DSP28335外设资源丰富,设计使用其多通道缓冲串行端口(McBSP)向AD9834写入控制字、频率子以及相位字。

2 系统硬件设计

2.1 DSP28335最小系统设计

(1)电源部分

DSP28335内核电压为1.9 V,I/O引脚电压为3.3 V,所以本设计采用外部5 V直流电源供电,然后接到TPS767D301(TI公司新推出的双路低压差电压调节器,其中一路是可以调节的)用以产生上述所需电压。

(2)时钟部分

一般简单的应用设计可以采用DSP内部晶振作为时钟信号,但考虑EAS系统的复杂性和前后时钟同步问题,本设计采用50 MHz的外部晶振提供给XCLKIN作为DSP部分的时钟输入,同时也连接到AD9834的MCLK引脚,这样既保证了同步也有较高的稳定性。

(3)JTAG接口部分

JTAG接口是链接调试电路板和PC仿真器的硬件接口,用于DSP开发人员进行软件调试,它主要包括这样几个引脚:TDI、TDO、TMS、TCK、#TRST 5个JTAG信号和EMU0、EMU1 2个仿真信号。设计的JTAG接口部分设计如图1所示。

图1 JTAG调试端口电路图设计

2.2 DSP与DDS的接口设计

本设计创新地采用DSP28335提供的多通道缓冲串口向AD9834写入数据,所以这里所说的接口设计就是多通道缓冲串口的硬件接口设计。

多通道缓冲串口(Multichannel Buffered Serial Port,McBSP),它的通信主要靠6个引脚完成,发送引脚 MDX、接收引脚 MDR、发送时钟信号引脚MCLKX、接收时钟信号引脚MCLKR、发送帧同步引脚MFSX和接收帧同步引脚MFSR。如图2所示,通过 GpioCtrlRegs.GPCMUX2寄 存 器 将 GPIO24、GPIO26和GPIO27分别复用为多通道缓冲串口模式,其中GPIO24(MDX)用于传送数据(包括频率字、相位字以及控制字),GPIO26(MCLKX)用于传送来自DSP28335内部的时钟信号SCLK,而GPIO27(MFSX)用于传输使能信号,当MFSX为低电平时开始传输数据。

图2 MCBSP接口电路图设计

3 软件设计

本设计的软件部分可归纳为3个部分内容:①初始化程序,包括Sys_Init(),McBSP_Init()和DDS_Init()3个函数;② 频率扫描程序,即Freq_Sweep();③ 频率锁定程序,即Freq_Lock()。系统软件设计流程如图3所示。

图3 系统软件设计流程图

初始化多通道缓冲串口时有几点需要注意:①使帧同步逻辑、采样率发生器、接收器和发送器处于复位状态(FSRT=GRST=RRST=XRST=0);② 其次,在使能采样率发生器前需要等待至少2个时钟周期(具体等待多久与具体的时钟频率有关),以保证内部的同步;SRG的帧同步周期和脉冲宽度在这里不需要设置。

AD9834工作模式取决于其内部的16位控制寄存器(DB15-DB0)的配置。在配置控制寄存器(写控制字)时,DB15和DB14必须置0,用以系统区别于频率相位信息。其中DB13和DB12共同决定写入字的方式,本设计采用DB13=1DB12=0方式,这样需要2次写操作才能将一个完整字载入任一频率寄存器,第1次写入包含频率字的14位LSB,第2次则写入14位MSB。控制寄存器配置结束后,需对频率寄存器和相位寄存器执行清零处理,否则可能会出现误码错传等情况,清零结束后需将整个DDS复位。

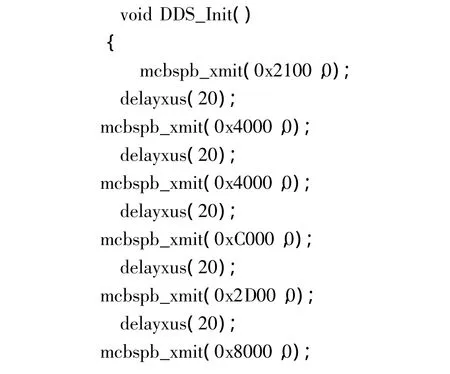

DDS_Init()部分配置情况相对复杂,不同的配置输出结果相差较大,配置信息详见 AD9834 DataSheet.pdf文档,这里列出本设计详细代码。

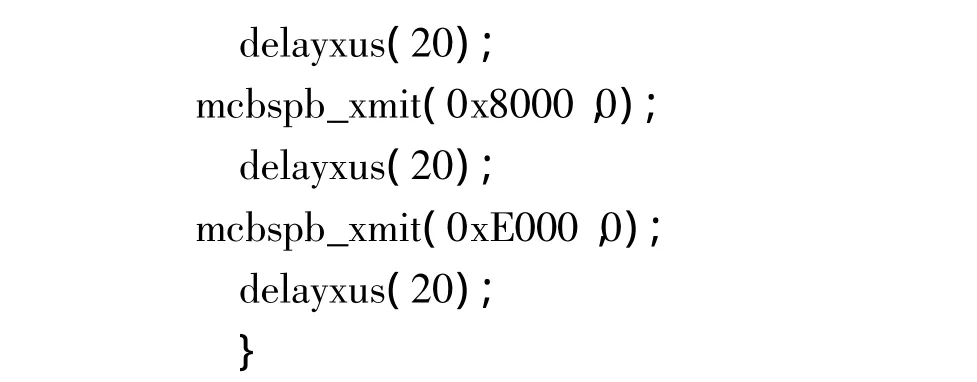

AD9834具有2个频率寄存器,可以使用其中任何一个,也可以2个同时使用,但当目标功能是频率扫描的时候,建议轮流使用2个频率寄存器,这里定义一个递增变量i利用其奇偶性进行控制,具体程序如下:

结合上述代码可知,扫频频信号共有16个频点,最低频率为 8 MHz,最高频率频率 8.5 MHz,频点间距为33.3 kHz。为了防止错误传输,相邻2次写操作间要有一定时延,这里引入了一个延时函数delayxus()。需要强调的是,本设计中不需要额外的相位偏移,所以相位字全部写0即可。

此外,Freq_Lock()过程描述如下:如果天线电磁辐射区域内没有标签出现,即没有标签信号产生时,则一直循环执行Freq_Sweep()函数,一旦检测到标签信号,系统会自动触发一个中断服务子程序,保存上述程序中的变量i值,频率锁定函数Freq_Lock()调用i即可实现频率锁定,具体程序与Freq_Sweep()类似,这里不再赘述。

4 结果展示

图4所示的是调试板上MCBSP传输数据的时序图。其中,上面一条波形的高低电平分别表示传输数据1和0,中间一条波形表示时钟信号,最下面曲线为帧同步信号,当帧同步信号为低电平且时钟信号在上升沿时才能实现1 bit数据的传输。如图4所示,本设计采用的传输字长是16 bit,此时传输的数据用二进制可表示为:0100 1010 0011 1101。

图4 MCBSP数据传输时序图

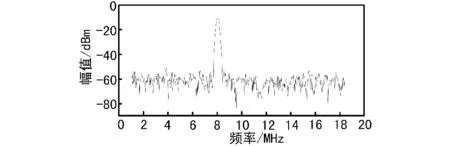

本设计输出的正弦波频率扫描范围为8.0~8.5 MHz,幅度700 mV左右,相位噪声较小,示波器测得波形如图5所示,图6为用频谱仪测得该正弦波的动态频谱图。

图5 输出正弦波波形

图6 输出正弦波动态频谱

5 结束语

设计创新之处:① 引入频率锁定技术,标签信号引起报警时锁定频率,2.5 s后解除锁定,这样可以在一定程度上降低系统误报率;② DSP28335与AD9834间的接口设计采用多通道缓冲串口方式,发送数据效率更高、速度更快;③本设计采用TMS320F28335(系统频率高达150 MHz)和AD9834芯片,与以往设计相比,硬件资源有较大提升。

由图5、图6可以看出,设计产生的正弦波信号线性度较好(与标准正弦波基本相同),相位噪声非常小(扫频时正弦波线条很细),频率精确度也较以往设计更高(扫频时频谱集中在8.0~8.5 MHz内部),本设计在很大程度上优化了扫频信号精确度与稳定性,具有较大推广价值。

[1] 刘陵顺,高艳丽,张树团,等.TMS320F28335 DSP原理及开发编程[M].北京:北京航空航天大学出版社,2011:25-76.

[2] 王忠勇,陈恩庆.DSP原理与应用技术[M].北京:电子工业出版社,2009:45-81.

[3] 王建新.直接数字频率合成技术及其应用研究[D].南京:南京理工大学,1999:35-41.

[4] 俞逖.射频EAS系统的性能优化和信号识别算法的研究[D].杭州:浙江大学,2006:3-26.

[5] 薛军,潘高峰,谢勇.基于ADF4350的多频段信号源的设计与实现[J].无线电工程,2011,41(11):53 -55.

[6] 窦兴川,王小东.基于DSP实现舰船目标检测与跟踪[J].无线电工程,2012,42(6):32 -34,38.

[7] CERCAS F A B,TOMLINSON M,ALBUQUERQUE A A.Direct Digital Frequency Synthesizer for a FH Spread Spectrum System:Analysis and Design[C]∥ 1990 SBT Telecomm Symposium IT S 90,1991:1 -3.

[8] NICHOLAS H T,SAMUELI H,KIM B.The Optimization of Direct Digital Frequency Synthesizer Performance in the Presence of Finite[M].USA:Wiley-IEEE Press,1992:1-2.

[9] GIFFARD R P,CUTLER L S.A Low-Frequency,High Resolution Digital Synthesizer[C]∥ IEEE Frequency Control Symposium,1992:1-3.