基于FPGA 的面阵CCD 图像采集系统

2013-12-22杨健鸷刘娟秀叶玉堂贾宏宇

杨健鸷,刘 霖 ,刘娟秀,叶玉堂,贾宏宇,王 平

(电子科技大学光电信息学院,现代光电测控及仪器实验室,成都610054)

CCD 因为噪声低,动态范围宽等特性,作为高性能成像器件被广泛用于工业非接触式测量。通过研究开发CCD 工业相机技术,可以针对应用环境不同的检测仪器,定制功能与其相适应的图像采集前端,获取高质量图像以完成高精度检测,用以降低实验室研发的光电检测设备前段采集系统的成本。

因为CCD 器件需要精确的驱动波形,所以比起CMOS 有更复杂的外围电路。同时由于选用的CCD器件采用的Bayer Array 作为颜色滤波阵列,采得的数据还需要经过插值算法恢复图像颜色。基于以上原因,本系统选用FPGA 做主控芯片,产生垂直移位驱动波形的同时配置AD 寄存器以产生水平移位驱动波形,并运用一种插值算法恢复图像数据输出到上位机[1-4]。实验结果满足研发一个采集前端系统的要求。

1 面阵CCD 成像系统

1.1 外围电路结构

CCD 芯片选用Sony 公司的ICX618AQA。AD芯片选用ADI 公司的AD9949,其具有输出行寄存器驱动波形(TG driving)的能力。驱动芯片选用CXD1267,能提供四象脉冲。

成像系统工作原理为:光学系统成像到CCD,光信息转换成模拟电信息,由FPGA 产生垂直移位驱动波形并配置AD 产生水平移位驱动波形,AD 对CCD 输出的模拟信号进行相关双采样后转化为数字信号[5]。数字信号在FPGA 中通过插值方法重新排列还原色彩。每帧图片存入SRAM1,同时读取SRAM2 中已存的上一帧图片。通过Cameralink 接口传到上位机进行处理。系统结构如图1 所示。

图1 系统设计框图

1.2 CCD 驱动时序分析

ICX618AQA 是Sony 公司生产的行间转移面阵CCD 图像传感器芯片。它的面积为1/4 foot(对角线长度),有效像素为659(H)×494(V),像元尺寸5.6 μm×5.6 μm,帧频为60 frame/s。驱动部分电路图如图2 所示。

CCD 正常输出模拟信号需要垂直驱动时序(VФ1,VФ2A/B,VФ3A/B,VФ4)和 水平驱动时序(H1,H2),复位时钟(ФRG)和衬底时钟(ФSUB)。因为垂直时序需要-5.5 V、0 V、15 V 3 个等级的电压驱动,FPGA 输出的CMOS 电平还需要经过一块驱动芯片CXD1267,同时额外引入XSG1,XSG2 2 个信号,与FPGA 产生的时序经过驱动芯片的门电路来控制垂直时序,实现电荷信号的正常转移[6]。

所有时序必须严格满足要求,基本工作原理为:每帧开始阶段,VФ2A/B,VФ3A/B通过15 V 电压阀将电荷从光敏感区转移到垂直寄存器区。之后四相垂直信号(VФ1,VФ2A/B,VФ3A/B,VФ4)在每行产生一组时序,将储存在垂直移位寄存器区的电荷向水平移位寄存器移动一行。水平移位信号(H1,H2)相互为反相关系,交替产生脉冲把存在水平移位寄存器的一行电荷按顺序输出到OUT 引脚,每移动一个像素复位信号(ФRG)清除剩余电荷。

图3 为关键信号仿真,其中XV2、XV4、SXHT 分别控制VФ1、VФ4、ФSUB,XV1 和XSG1 控制VФ2A/B,XV3 和XSG2 控制VФ3A/B。

图2 CCD 驱动电路图

图3 垂直移位驱动信号仿真

1.3 AD 寄存器配置

系统选用的AD 芯片通过配置寄存器完成2 个部分的功能,一是水平移位时序(H1,H2)和复位时钟(ФRG)的驱动,二是对模拟信号的相关双采样,再经过箝位,增益等操作,最后转变为数字信号输出[7]。

AD 芯片可以通过内部时序核心把输入的主时钟单周期分为48 份,H1,H2和RG 的跳转位置可以在这48 个相位上选择,并在电荷从垂直移位寄存器转移到行移位寄存器的阶段,通过控制HBLK 屏蔽H1,H2的跳转,AD 输出的3 个驱动信号强度需配置为8.4 mA,以满足CCD 要求。

由于CCD 输出的为模拟信号,且每个周期分为复位电平,参考电平,信号电平3 个阶段,而储存的电荷经过放大器才能输出,所以放大器的复位(KTC)噪声和放大器1/f 噪声是影响CCD 的主噪声[8]。由于参考电平和信号电平的噪声都同时会被放大,采用相关双采样(CDS)技术,第1 次对复位电平进行采样,第2 次对象元信号电平进行采样,两次取样的差值可以抵消复位噪声。AD9949 芯片可以内部产生双采样脉冲,同样,每个时钟被分成48个相位位置,可以选用其中2 个做为采样位置。相关双采样技术抑制噪声的程度由两次采样得到的复位噪声的相关程度决定。

一般输出的模拟信号经过相关双采样,象元电平在百毫伏左右,需要经过VGA 的增益才能使图像动态范围更大,同时,由于CCD 对不同波长敏感性不一样,对绿色的敏感度更高,所以AD9949 还提供了3 种模式的针对不同滤光片的增益方法(PxGA)[9]。此系统中我们选用贝叶滤光片,逐行扫描模式。

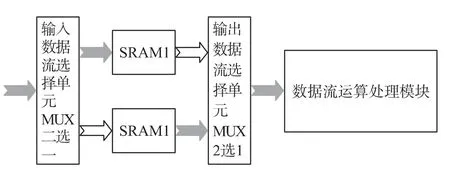

1.4 SRAM 存储

“乒乓操作”是常用于数据流控制的处理技巧。处理流程为:输入数据流通过“输入数据流选择单元”,在奇数帧时间把数据存入SRAM1,同时读取SRAM2 的内容,偶数帧时间相反。交替进行,等时地将数据流分配到数据缓冲模块。如图4 所示。

图4 SRAM 的乒乓储存

乒乓操作的最大特点是,通过“输入数据流选择单元”和“输出数据流选择单元”按帧频(VD),相互配合地切换,将经过缓冲的数据流没有时间停顿地送到“数据流运算处理模块”,进行运算和处理。把乒乓操作模块看成一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有停顿,非常适合对数据流进行流水线式处理,所以乒乓操作常用于流水线式算法,完成数据的无缝缓冲和处理[10]。

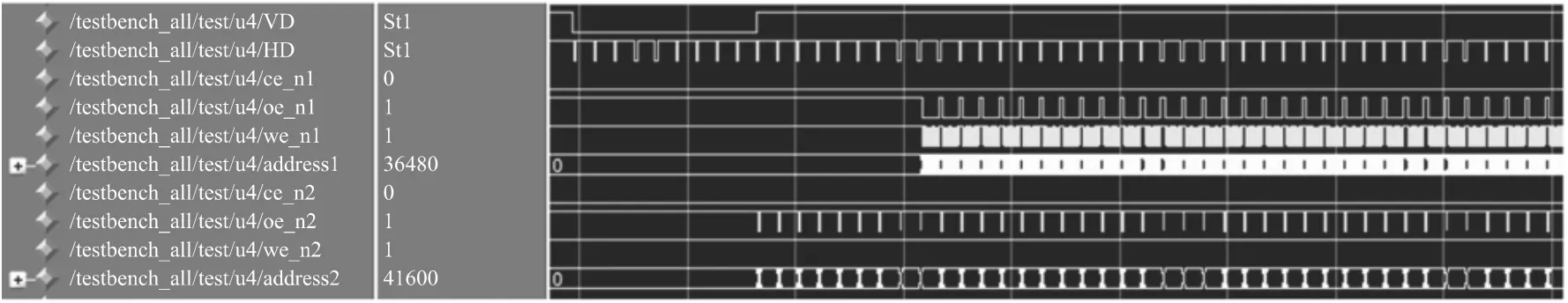

如图5 为乒乓操作操作的仿真部分波形,存取的时候已经根据感光区域大小截存需要的象元数据,读取的时候因为需要通过Cameralink 传输到上位机显示,所以读完一行的时候需要控制Cameralink 行完成信号(LVAL),此时读取需要停止。仿真中数据采集跟存同步,比读取时钟慢了12倍,故从仿真中可以看出每行读取要比存取快很多。

图5 SRAM 乒乓操作

2 颜色恢复算法

目前存在多种类型的颜色滤波阵列,其中Bayer型颜色滤波阵列有很好的彩色信号敏感特性和彩色恢复特性,被广泛的应用在各种图像传感器上。本系统实现一种典型算法采用颜色分量信息,合成彩色图像。基本原理为:如果1 个像素缺少某种颜色的分量,就用其邻域中同色分量填补[11]。

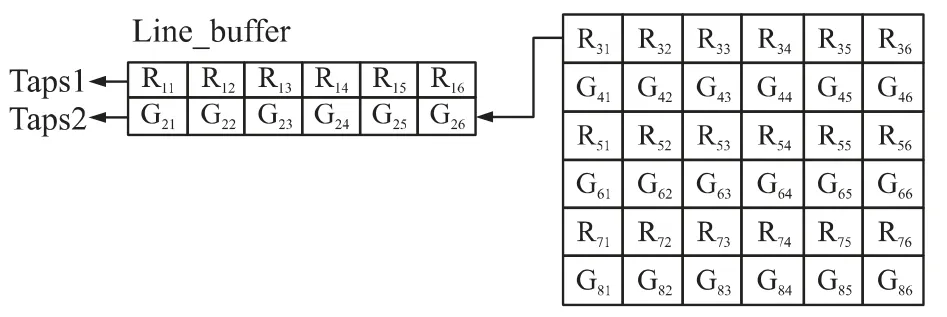

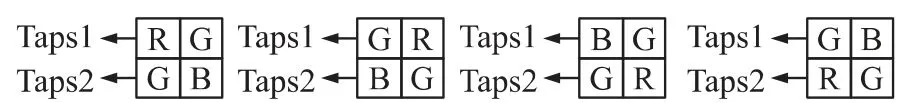

模块采用Verilog 语法描述,如图6 所示。

方法使用了带有2 个并行输出端(taps1,taps2)的移位寄存器(line_buffer),数据按顺序移入寄存器。如图所示,已移入1,2 行的数据,第1 个周期taps1 得到R11(第1 行第1 个红色像素)的数据,taps2 得到G21的数据。将两个数据保存进变量,第2 个周期得到G12和B22,同时用取得的4 个数据进行计算,每次输出的数据是对2×2 像素块的处理结果。

图6 颜色恢复示例

图7 四种排列方式

由于进入移位寄存器后的像素有4 种排列模式,需要设计两个计数器并通过最后一位来判断颜色处于哪种顺序之下。从上述方法可以看出,采用这种颜色恢复方法是以降低分辨率为代价的。此后的采集系统中,将采用在硬件上实现双线性插值的方法恢复图像颜色。

3 实现及测试结果

为了得到更加直观的测试结果,采集速度做了降低处理。

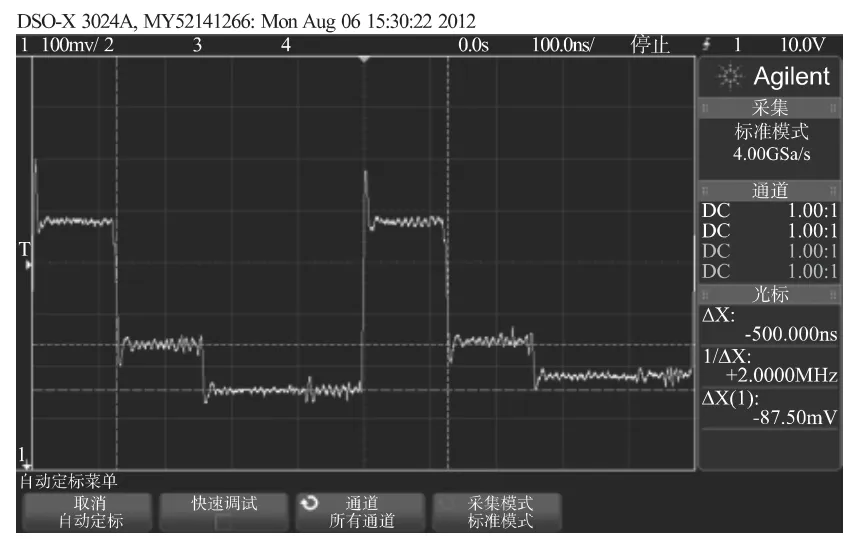

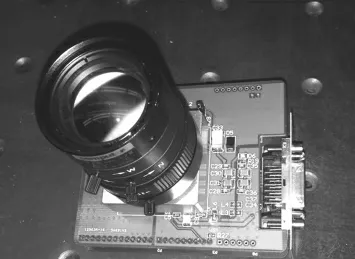

图8 为CCD 输出波形,图9 为相机实物。

图8 CCD 输出波形

图9 相机实物

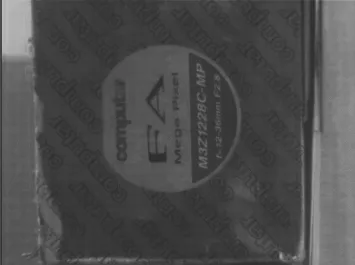

实验工作环境为实验室普通光源,原始如图10所示。

图10 原始图像

通过插值算法恢复得的黑白和彩色图像如图11 和图12 所示。

从图10 中可以看出,CCD 感光单元对经Bayer滤波阵列后的RGB 3 种颜色感光度不同,造成有规律的暗点出现。图11 是经过颜色恢复算法的黑白图,图12 是经过颜色恢复算法的彩色图像。

图11 恢复后黑白图像

图12 恢复后彩色图像

4 结论

本文通过分析SONY 公司CCD 芯片ICX618AQA,实现一种基于FPGA 的彩色面阵CCD 图像采集系统。电路设计采用层板对接的方式,目前是用插针,后期改良采用软排线可以另厚度进一步降低,达到小型化的目的。系统由FPGA 控制,代码采用Verilog设计,易于仿真和修改,关键时序产生和图像恢复算法都在FPGA 中完成,代码验证后再下载到器件的过程令设计的正确性得到保证。根据实验,可以满足系统高速,集成度经济性等要求。

[1] Wang Yan,He Zhikuan. Design of High-Speed Driving Circuit for Large Area Array Full Frame Transfer CCD[C]//International Symposium on Photoelectronic Detection and Imaging 2011:Advances in Imaging Detectors and Applications,2011,Proc.of SPIE Vol.8194:819411-1.

[2] Srinivasan R,Anupama K,Suneeta,et al.FPGA Based ASM Implementation for CCD Camera Controller[C]//2009 International Conference on Emerging Trends in Electronic and Photonic Devices &Systems(ELECTRO—2009),2009.

[3] Xu Zhipeng,Wei Jun,Zhou Qianting.Design of the Driving System for Visible Near-Infrared Spatial Programmable Push-Broom Remote CCD Sensor[C]//.Advanced Sensor Systems and Applications Ⅳ,2010,Proc.of SPIE Vol.7853:78531O-1.

[4] Tian Yan,Cao Jianzhong,Yao Dawei.Technology Research of High-Definition CCD Camera Based on FPGA[C]//International Symposium on Photoelectronic Detection and Imaging 2011:Advances in Imaging Detectors and Applications,2011,Proc.of SPIE Vol.8194:819425-1.

[5] Li Binhua,Song Qian,He Chun.Method to Implement the CCD Timing Generator Based on FPGA[C]//.High Energy,Optical,and Infrared Detectors for Astronomy Ⅳ,2010,Proc. of SPIE Vol.7742:77421Y-1.

[6] 冉峰,黄舒平,杨辉. 图像采集系统的面阵CCD 驱动电路设计[J].电子技术应用,2009(11):43-45.

[7] 侯新梅,,李自田.AD9822 及其在面阵CCD 系统中的应用[J].现代电子技术,2010(20):191-196.

[8] Cheol-Hong Moon,Young-Soo Roo,Hwa-Young Kim. An SoC Embedded System Implementation Using an Array Sensor[C]//Fourth International Conference on Fuzzy Systems and Knowledge Discovery(FSKD),2007,0-7695-2874-0/07.

[9] Analog Devices Inc.,12-bit CCD Signal Processor with Precision Timing Core [EB/OL]. Product Specifications,http://www.analog.com.

[10] 吴继华,蔡海宁,王诚.Altera FPGA/CPLD 设计高级篇[M].北京:人民邮电出版社,2011:19-20.

[11]贺钦,刘文予.数字图像传感器颜色插值算法研究[J].小型微型计算机系统,2007,28(8):1482-1485.