高速印制电路板设计

2013-12-17林初善冉金志李倩茹邵云飞

林初善 冉金志 李倩茹 邵云飞

1.西安通信学院,陕西 西安 710106

2.中国人民解放军76110 部队75 分队,河南 衡阳 421008

1 概述

随着微电子技术的发展,速度已成为许多系统设计中需要考虑的最重要因素之一。对于高速系统的设计,无论是数字电路还是模拟电路,噪声是一个最值得关注的问题。高频信号会由于辐射而产生干扰,亦会导致振铃、反射以及串扰等,如果不加以控制,会严重降低系统性能。

本文将就高速信号反射控制、串扰控制、电磁干扰控制以及叠层设计等方面讨论高速印制电路板设计中需要注意的几个噪声控制问题。

2 高速印制电路板设计的难点

对于高速印制电路板设计,最重要也是最难的是如何保证信号的完整性和对电磁干扰的控制。对于信号完整性的分析,主要包括对反射、串扰及电源完整性的分析等。串扰可以使信号中增加干扰频率成分,导致信号质量变差,严重时接收端将无法接收信号。电磁干扰是指系统通过传导或辐射的方式发射电磁波影响其他系统或本系统内其他子系统的正常工作。它会影响本系统及其他系统的正常运行,也应该进行严格的控制。

3 信号的完整性保证与电磁干扰控制

3.1 信号反射控制

反射是指由于阻抗不匹配而造成信号能量不完全吸收的现象。当信号在不同媒介传播时,由于不同媒介的阻抗不同,导致信号在不同媒介交界处部分能量不能通过,情况严重时,还会引起信号在媒介两端不停地反射,随之产生一系列的信号完整性问题。但是,在实际设计中,并不能完全保证传输线阻抗的恒定不变,只能尽量控制。在设计过程中,采取以下措施来控制阻抗:

(1)对于驱动端与接收端的阻抗不一致现象,采用Thevenin 等效阻抗进行匹配。采用这种阻抗匹配方式能够平衡高低电平,提高电路的扇出能力,减小由于占空比失调引起的能量消耗。

(2)严格控制高速信号传输线的特性阻抗。通过调整线宽、线距、叠层厚度等PCB 参数尽量将传输线特性阻抗控制在一个固定值(如50Ω)。设计中信号走线采用表面微带传输线,它的特性阻抗计算公式如式(1)和式(2)。

其中,Z0 表示传输线的特性阻抗,单位为Ω;W 表示信号走线的宽度;T 表示信号走线的厚度;H 表示信号走线与参考平面的距离;表示介质的相对介电常数。W、T 和H 这三者的单位要一致;1mil=0.0254mm。

一般情况下高速信号均采用差分格式,此时表面微带差分传输线的特性阻抗的计算公式如式(3)。

式中,D 表示两差分走线边沿的距离,单位要与H 的单位保持一致;Z 差分表示差分传输线的特性阻抗,单位为Ω;

例如,在设计中,如果要把差分微带传输线的特性阻抗控制在100Ω,为此,兼顾其他方面的要求,可以确定各参数值如下:

W=0.2mm;T=0.03mm;H=0.2mm;D=0.2mm;=4.1(FR-4 材料的相对介电常数)。

将以上数值代入式2 和式3,计算得差分阻抗Z 差分=100.1Ω。当然,以上的计算并不精确,因为公式中本身就忽略了一些参数,如表面覆盖的绿漆厚度以及它的介电常数等,再加上在实际制板过程中,由于工艺上的误差可能导致各个参数值的差异,实际PCB 板上的差分特性阻抗并不完全等于100Ω。为此可以用专门的软件进一步计算这个特性阻抗,但最终的匹配阻抗值则需要在最后的调试阶段进行阻值调整,以达到完全匹配。用目前较为流行的计算特性阻抗的软件Polar Si8000 计算上例中的差分特性阻抗,得到Z 差分=109.77Ω,这个值是综合考虑了表面绿漆及工艺误差等因素得出的,最后的调试结果证明了这个差分阻抗能够实现较好的信号质量。其界面如图1所示。

(3)严格进行差分线上的阻抗连续性控制。为了达到使用差分传输线的最佳效果,必须进行阻抗连续性控制,否则信号就会在阻抗不连续的地方产生反射。为此,要尽量做到两差分线“等长等距”平行走线,信号离开器件引脚后,要尽量靠近,保持两差分线距离为0.2mm;尽量不使用过孔,必须使用过孔时要保持两差分线上的过孔数目相等;尽量使用圆弧折线,避免使用或折线,以减少阻抗不连续发生的可能性。

3.2 信号串扰控制

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生不期望的电压噪声干扰[5]。这种干扰是由于传输线之间的互感和互容引起的,所以对串扰的控制也就应该从减小传输线间的互感和互容入手。在设计中,可以从以下三个方面来减小串扰:

(1)使用差分信号格式。在设计初期选择器件时就优先选择具有差分信号接口的器件。由于数字信号在差分线上传输时,正负两路信号的相位相差,即信号是以“差模”的方式传输,而噪声是以“共模”的方式在一对差分线上耦合出现。在接收端,正负两路信号相减就可以得到信号,消除噪声,所以采用差分传输线可以有效地减小串扰。

(2)低速信号与高速信号分层布线。将电平幅度较大的低速信号(如TTL 电平信号)远离高速差分信号,尽可能将它们布在不同层面上,以减小低速信号对高速信号的影响。

(3)尽量减小地平面与传输线之间的距离,将它控制在0.2mm,使信号回流面积最小。

3.3 电磁干扰控制

图1 差分特性阻抗计算界面图

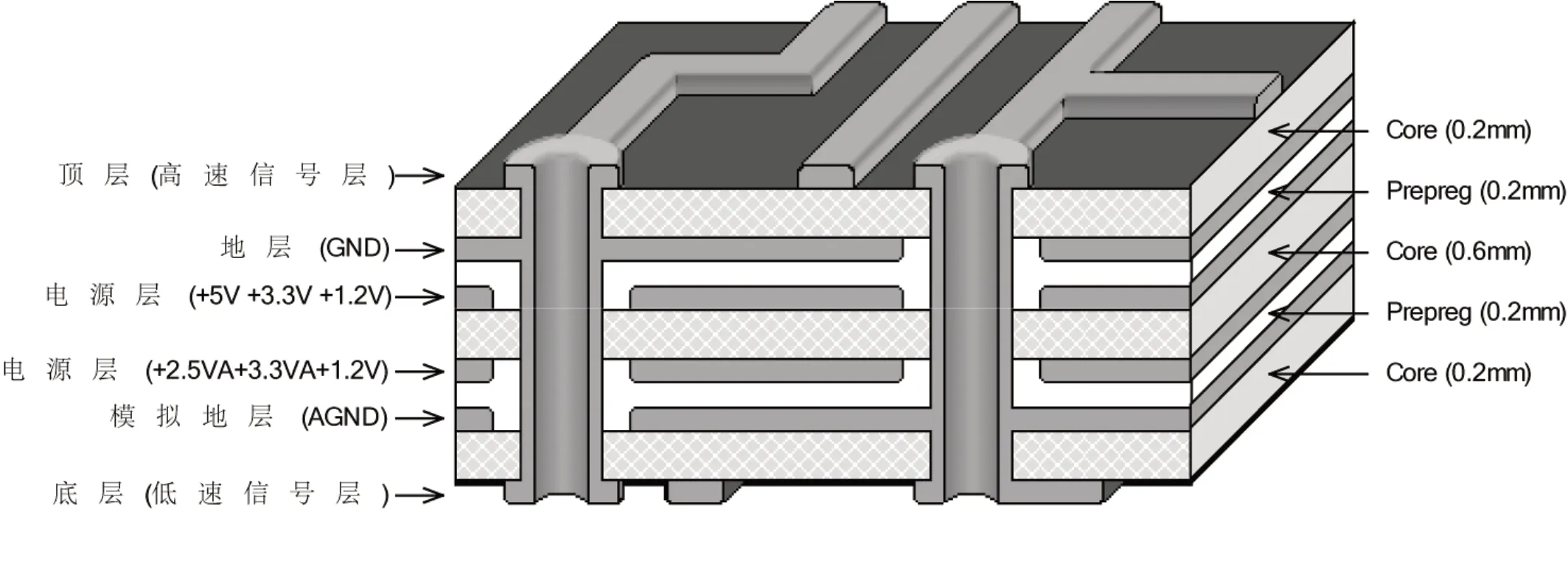

图2 6 层板典型叠层结构

电磁干扰(EMI)是电子设计过程中不可避免的一个问题。特别是在高速电路的PCB 设计过程中,如果不对EMI进行有效控制,就很难达到设计目的。控制EMI 的主要措施有三种:屏蔽、滤波和接地。它们之间的相互关联的,接地的好坏直接影响设备对屏蔽和滤波的要求,而屏蔽的优劣也影响着对滤波器的要求。此外,采用差分对走线也能起到抑制EMI 的效果。

(1)滤波。一般在设计中采用去耦电容、EMI 滤波器和磁性元件等器件来实现滤波。通常的做法是用电容值比较高的电容去滤除低频噪声,用电容值比较小的电容去滤除高频噪声。在设计中,每个电源输入处各放置一个47μF 和一个100μF 的钽电容,来抑制电源低频成分。在器件的每个电源输入引脚处尽可能多地放置一些去耦电容来滤除高频部分,容值为0.001μF 和0.01μF,电容位置尽可能靠近器件。电容之间使用多个过孔到地,电容的过孔尽量靠近焊盘,这样可以获得最佳的滤波效果。此外,磁性元件用于电源滤波的效果非常好。在设计中,在每个电源的输入端可以串连一个磁珠,这样可以有效加强对EMI的控制。

(2)屏蔽。通过空间传播的电磁干扰可以通过屏蔽进行有效地抑制。屏蔽不仅可以避免本系统给其他系统造成影响,而且可以防止外界电磁辐射干扰本系统。

(3)接地。接地方式有很多种,其中多点接地是指电路中的接地点都直接接到离它最近的地,以使得各个接地线的长度最小。

4 PCB 叠层设计

从前面的分析可以看到,保证信号到参考平面的低阻抗在抑制EMI 中起着重要的作用,因而在进行叠层设计时,应该特别注重参考平面层的安排。理想的分层结构应该是接地层紧挨着信号层两边,而且保证电源层与接地层相邻,二者距离尽可能的小。随着信号频率的不断提高,一般只有6 层以上的PCB 板才能起到良好的EMI 抑制效果。

以6 层板为例,其叠层结构设计如图2所示。

在图2中,与顶层高速信号层和底层低速信号层相邻的都是地层,距离为0.2mm。两个电源层分别与地层近距离相邻,距离为0.2mm。由于系统需要6 个电源电压,如果在一个电源层上分割困难,则采用双电源层设计。

[1]SI 仿真小组.高速PCB 基础理论及内存仿真技术[R].2002-10-252002-10-25.上海:ATP 华腾微电子(上海),2002

[2](美)Mark I.Montrose.电磁兼容和印刷电路板理论、设计和布线[M].(刘元安等译).北京:人民邮电出版社,2003:151~154

[3]江思敏.PCB 和电磁兼容设计[M].北京:机械工业出版社.2006.176~183

[4](美)V.Prasad Kodali.Engineering Electromagnetic Compatibility[M].(陈淑凤等译).北京:人民邮电出版社,2006.210~218

[5](日)久保寺忠.高速数字电路设计与安装技巧[M].(冯杰等译).北京:科学出版社,2006.161~164