基于VIIS-EM平台的虚拟数字集成电路测试仪的设计

2013-12-07尹超平张秉仁赵吉祥

尹超平,张秉仁,赵吉祥

(吉林大学 仪器科学与电气工程学院,吉林 长春 130026)

集成电路测试是对集成电路或模块进行检测,通过测量集成电路输出响应与预期输出进行比较,以确定或评估集成电路元器件功能和性能的过程,是验证设计、监控生产、保证质量、分析失效以及指导应用的重要手段[1]。数字集成电路DIC(Digital Integrated Circuit)测试是集成电路测试的一个主要分支,是一种保障数字集成化芯片内部电路质量和逻辑功能完整性的测试,主要应用于双极型数字集成芯片(TTL系列)和场效应型数字集成芯片(MOS系列)的检测。目前世界上高档集成电路测试系统大都是日本和美国生产的,如美国Credanceo公司推出的 Vanguard系列和SAPPHIRE系列,日本 Advantest公司研制的T600系列等。我国在半导体行业起步晚于发达国家,芯片测试行业也是如此,国内的大部分高端测试市场被国外的测试企业占据。购买国外的测试设备一般都价格昂贵,随着数字集成芯片的使用日益频繁,急需一种应用在中小型规模的数字集成电路检测设备来保障其性能[2],本文设计的虚拟数字集成电路测试仪就是从通用、快捷、准确、廉价等几个基本优势点出发,将其集成在吉林大学自主研发的VIIS-EM平台上。VIIS-EM平台的全称为虚拟电子测量仪器集成系统(Virtual Instrument Integration System for Electronic Measuring),它基于模块化仪器的设计思想,采用 “一个控制器+多个功能模块”的构建方式,方便了仪器的可重构性,上位机采用LabVIEW软件作为工具进行图形化编程,操作界面友好,自定义功能强大,方便于功能扩展[3]。文中详细阐述了虚拟数字集成电路测试仪的设计理念和实现方案,重点论述了系统的硬件电路设计和软件处理方法。并给出了实测结果,验证了仪器测试的可行性。

1 VIIS-EM平台与DIC测试技术简介

VIIS-EM平台机箱内置了直流稳压电源和系统总线背板。集成在系统中的功能模块均采用标准的3U(3.94英寸×6.3英寸)尺寸进行设计,各模块均通过 96脚的欧式连接器与系统背板相连,系统背板具有9个插槽,从左向右依次为0号槽、1号槽……8号槽。

在检测DIC芯片时,需要依照一定的测试顺序对芯片进行检测,顺序的合理性会使测试变得清晰,高效。一般的数字集成电路测试顺序为接触性测试、功能测试、直流参数测试及交流参数测试。

(1)接触性测试,隶属于直流参数测试的范畴,目的是为了验证芯片的各功能引脚是否正确连接。测试原理为在被测器件所有管脚都接到地的情况下,对被测管脚施加电流并测量相应的电压,通过得到的电压值来判断其连接性是否完好。

(2)功能测试,验证DIC芯片的逻辑完整性。通常有两种方法可供选择,一种是金器件法,一种是存储响应法。金器件即已知无误的芯片。测试时,通过同时检测被测器件和金器件,来对比判断芯片的好坏,这种测试方法具有依赖性,不能独立地进行测试操作,故本设计采用存储响应法的测试原理,将输入激励值和输出期望值都存入外部数据库中,测试时通过将实测值与期望值进行对比来判断芯片的好坏。

(3)直流参数测试,对DIC芯片的管脚进行电压电流测试,只要芯片通过了这些测试,就可保证其基本性能,对时间要求不是十分严格。测试的项目主要有输出高/低电平(VOH/VOL)测试;输入高/低电流(IIH/IIL)测试;输入漏电流II测试;输出短路电流IOS测试;电源电流测试等;

(4)交流参数测试,主要检测器件内部的晶体管在转换状态时的时序关系,包括一些时间常数。本设计只针对芯片的功能测试和直流参数测试,没有包括交流参数测试部分,故此处只做简单介绍。

2 系统总体结构设计

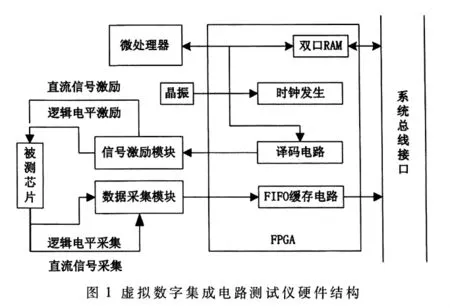

按层次结构分,系统可分为软件应用层、设备驱动层和硬件物理层。应用层使用LabVIEW软件进行编程,用于控制仪器和对采集的数据进行分析、处理及显示,同时LabVIEW中提供了“互联接口”函数可动态地调用仪器驱动程序。仪器驱动程序属于上层驱动,在运行时与底层USB驱动进行交互通信,实现板卡识别、消息传递等功能。硬件物理层使用“微处理器+FPGA”进行数据接收、发送和译码,并在前端搭建调理电路,实现不同逻辑电平的输出、微安级恒流源的输出、数模信号采集等功能。

3 虚拟数字集成电路测试仪硬件电路设计

根据模块化设计思想,将整个系统的硬件部分分成总线接口通信模块、信号激励模块、数据采集模块三个部分。硬件结构图如图1所示。

3.1 总线接口通信模块

系统通过FPGA中自定义的双口RAM电路实现与总线的接口通信。系统上电时,微处理器负责初始化设备,向双口RAM中写入配置信息,配置信息通过系统总线传输到总线控制器;在仪器运行过程中,若更改上位机控制命令,则模块板卡的微处理器也会通过双口RAM从总线控制器上读取相应的配置信息。

3.2 信号激励模块

信号激励模块可提供数字逻辑电平输出和直流电压/电流信号输出。数字逻辑电平输出用于驱动被测DIC芯片,测试其逻辑功能,本设计采用74LVC245A芯片转换LVTTL电平为TTL电平,用来驱动被测TTL数字集成芯片,对于CMOS型数字集成芯片,由于其高电平最小输入电压大于TTL电路高电平最大输出电压,故不能直接用TTL电平激励CMOS电路,在设计时采用外接4.7 kΩ上拉电阻将TTL输出电平拉高,来驱动被测CMOS芯片。

为了对DIC芯片进行接触性检测和直流参数测试,须对被测芯片提供必要的直流电压/电流激励信号。本设计采用BB公司的数模转换器DAC902搭建直流电压输出电路,此芯片的转换位数为12 bit,数据边沿触发锁存,差分电流输出,加负载电阻转换成直流电压信号,外接差分放大电路,将D/A差分输出的±1 V转为单极性输出,同时将电压放大2.5倍,差分放大电路如图2所示。

测试中所用的直流电流激励信号要求微安级别,DAC902不满足测试要求,设计中采用仪表放大器AD620和OPA602搭建出带跟随反馈的高精度微安级数控恒流源[4],如图 3所示。

3.3 数据采集模块

数据采集模块分为逻辑电平信号采集部分和直流电压/电流信号采集部分,它们在FPGA中公用一条8位数据总线,通过多路复用器进行模式选择。逻辑电平信号采集利用74LVC245A进行TTL/LVTTL电平转换,输出信号符合FPGA输入电平标准,故直接采用FPGA进行LVTTL电平采样;直流电压/电流信号的采集使用ADI公司的双8 bit高速模数转换器AD9288BST-40,前端调理电路进行电压衰减和驱动放大,使其输出电压在A/D的允许范围内。

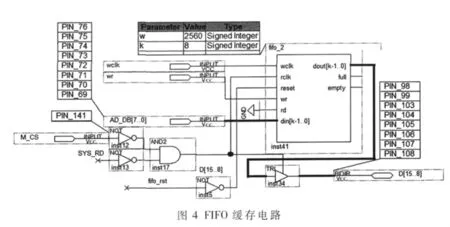

采集到的逻辑电平信号和直流电压/电流信号按每次8 bit数据缓存在FPGA的FIFO中。FIFO缓存电路如图4所示,每个FIFO设置为2.5 KB的存数空间,写速率时钟wclk最高可以达到20 MHz,即采集系统的最高采样频率,FIFO的输出端通过一个三态门实现数据的复用。

4 虚拟数字集成电路测试仪软件设计

系统上位机部分使用LabVIEW软件进行编程,主要分为前面板和程序框图两部分。前面板即用户界面,定义各种输入控件和显示控件,用来设置仪器参数以控制仪器;程序框图包含各种功能函数,可进行数据的运算处理和通信。以模块来划分,本仪器的软件部分主要分为数据通信模块、数据库调用模块和数据处理模块。

4.1 数据通信

LabVIEW中集成了功能强大的数据接口通信函数,能实现上位机与硬件模块的连接控制。本系统软件通过CLF(Call Library Function)节点函数调用动态链接库。在发送命令消息时将LabVIEW中的数据类型映射为DLL文件中定义的数据类型,实现命令参数的传递。同样,在数据采集时,通过CLF节点函数将硬件模块采集到的数据映射为LabVIEW数据类型,以完成进一步的处理与显示。

4.2 数据库调用

无论哪种汇编语言,都是在底层驱动的基础上,利用 ODBC或者 DAO、ADO调用API接口来操作数据库的。LabVIEW中集成了数据库连接工具包,封装了ADO(ActiveX Data Objects)的接口,为数据库的调用提供了编程环境。本系统软件即通过UDL建立数据源连接字符串,使用ADO模型调用Microsoft Office中的Access来实现数据库操作的。Access数据库中记录了九类常用数字芯片的逻辑关系,在初始化设定时,系统根据被测试芯片的芯片型号加载相应的数据库。在自动测试过程中,根据数据库表中建立的逻辑关系对芯片进行逐步激励。并采集输出逻辑信息,与数据库中期望值进行比对,若逻辑值符合期望标准则测试通过。

4.3 数据处理

采集到的数据信息通过CLF节点传递到上位机软件中,根据硬件FIFO存储容量限制,每路通道每次最大能读取320 B数据,16路数据存储在一个具有5 120个元素的一维数组中。在数据显示时,通过“抽取一维数组”函数和“索引数组”函数将一维数组数据拆分为16组布尔量,每组布尔量再转换为“0,1”逻辑序列,由数字波形图显示出来。

5 数据显示及实测结果

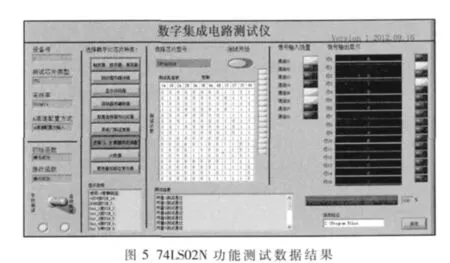

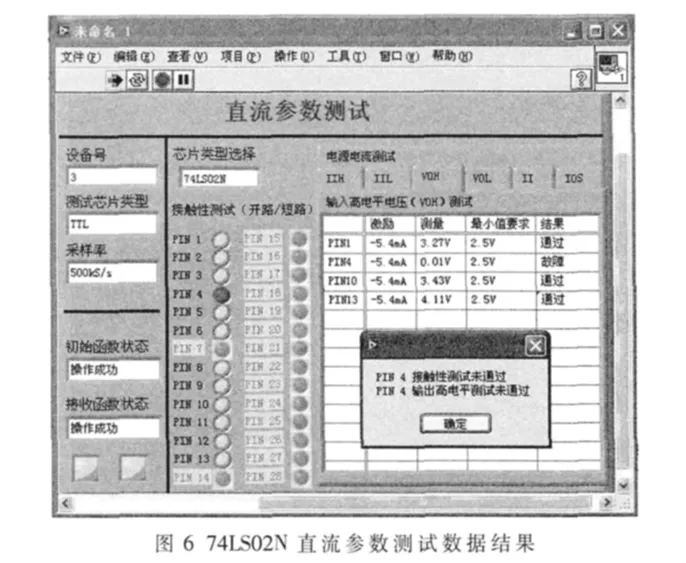

图5中显示的是测试74LS02N芯片功能好坏的测试用例,以图中面板中央位置显示的真值表项为依据,虚拟数字集成电路测试仪顺次给硬件模块发送激励信号,作用于被测芯片,同时读取采样电平与数据库标准逻辑比对,测试通过则显示文本提示并点亮相应的测试灯,右下方进度条代表测试进度。图6所示为74LS02N的直流参数的测试

结果,通过在芯片的各功能引脚处施加规定的电压电流信号,测量输出的直流参数是否在允许的范围内来判断芯片性能的好坏。测试时将74LS02N的PIN 4引脚开路作为异常情况测试。

采用VIIS-EM平台下研制的虚拟数字集成电路测试仪,通过反复的实验测试,表明对于常见的74系列和54系列数字集成芯片,系统能够准确快速地验证其逻辑功能的正确性和完整性,对于损坏的芯片能找出其问题引脚。系统的创新点在于应用了当今最前沿的模块化结构设计思想,优化了系统的设计、调试以及维护[5]。采用以计算机为核心的虚拟仪器技术,替代了传统仪器的部分硬件电路,改善了传统仪器笨重复杂等缺点,同时增加了仪器的可操作性和用户的自定义功能,在成本方面,基于虚拟仪器技术来搭建的系统价格也得到了大幅度降低。另外,本虚拟数字集成电路测试仪可扩展性强,可在通用性基础上进行功能提升、扩充,具有丰富的可重构前景。由于系统数据总线的位数限制,本仪器目前能够实现16位数字信号的采集,在未来的总线开发上还有待提高。

[1]高成,张栋,王香芬.最新集成电路测试技术[M].北京:国防工业出版社,2009.

[2]WEST G L.A microcomputer-controlled testing system for digital integrated circuits[J].IEEE Transactions on Industrial Electronics and Control Instrumentation,1980,IECI-27(4).

[3]阮奇桢.我和LabVIEW[M].北京:北京航空航天大学出版社,2009.

[4]胡波,李波,罗贤虎,等.微安级数控恒流源的设计[J].电子技术,2010(4).

[5]吴忠杰,林君.虚拟测试系统中模块化仪器关键技术研究[J].仪器仪表学报,2005(22):280-283.