用Verilog语言设计任意次ASIC分频器

2013-11-19唐卫斌

唐卫斌

(商洛学院 物理与电子信息工程系,陕西商洛 726000)

Verilog语言是应用最广泛的硬件描述语言(HDL)之一。它是硬件(数字逻辑电路)设计人员和EDA工具之间的界面;是一种用形式化方法来描述数字电路和设计数字逻辑系统的语言。设计者可以利用这种语言来描述自己的设计思想,然后利用EDA工具进行仿真验证和时序分析,再自动综合到门级电路,最后用ASIC(专用集成电路)或FPGA实现其功能[1-2]。

分频器是FPGA设计中使用频率非常高的基本单元之一。它是将较高频率通过分频得到较低频率的一种单元电路。尽管目前在大部分设计中还广泛使用集成锁相环 (如altera的PLL,Xilinx的DLL)来进行时钟的分频、倍频以及相移设计[3],但是,对于时钟要求不太严格的设计,通过自主设计进行时钟分频的实现方法仍是不错的选择。首先这种方法可以节省锁相环资源,再者,这种方式只消耗不多的逻辑单元就可以达到对时钟操作的目的,具有成本低、可编程等优点[4]。而使用Verilog语言进行分频器设计在当前设计实践中并不多见,文献[5]中夏宇闻教授对此稍有提及,但未给出具体代码。本文在介绍计数器设计的基础上,给出基于计数器的分频器设计模版,包括偶数次分频和奇数次分频,这些模版在当前的设计实践中尚且空缺,因而可以给其他数字逻辑电路设计人员直接调用,或者作为库文件使用,从而大大缩短电路设计人员的设计时间。

1 计数器

计数器是实现分频电路的基础,计数器有普通计数器和约翰逊计数器两种。这两种计数器均可应用在分频电路中[6]。

1.1 加法(或减法)计数器

使用Verilog实现的模十加法计数器:

module cnt10(clk,rst,cnt);/*定义端口变量 */

input clk,rst;

output[3:0]cnt;

reg[3:0]cnt;

always@ (posedge clk,posedge rst)if(rst)cnt<=0; /*复位信号*/

else

begin if(cnt==9)cnt<=0; /*当计数到 9时强制归零*/

else cnt<=cnt+1; /* 计数 */

end

endmodule

使用Modelsim仿真结果如图1所示。

图1 普通计数器仿真波形

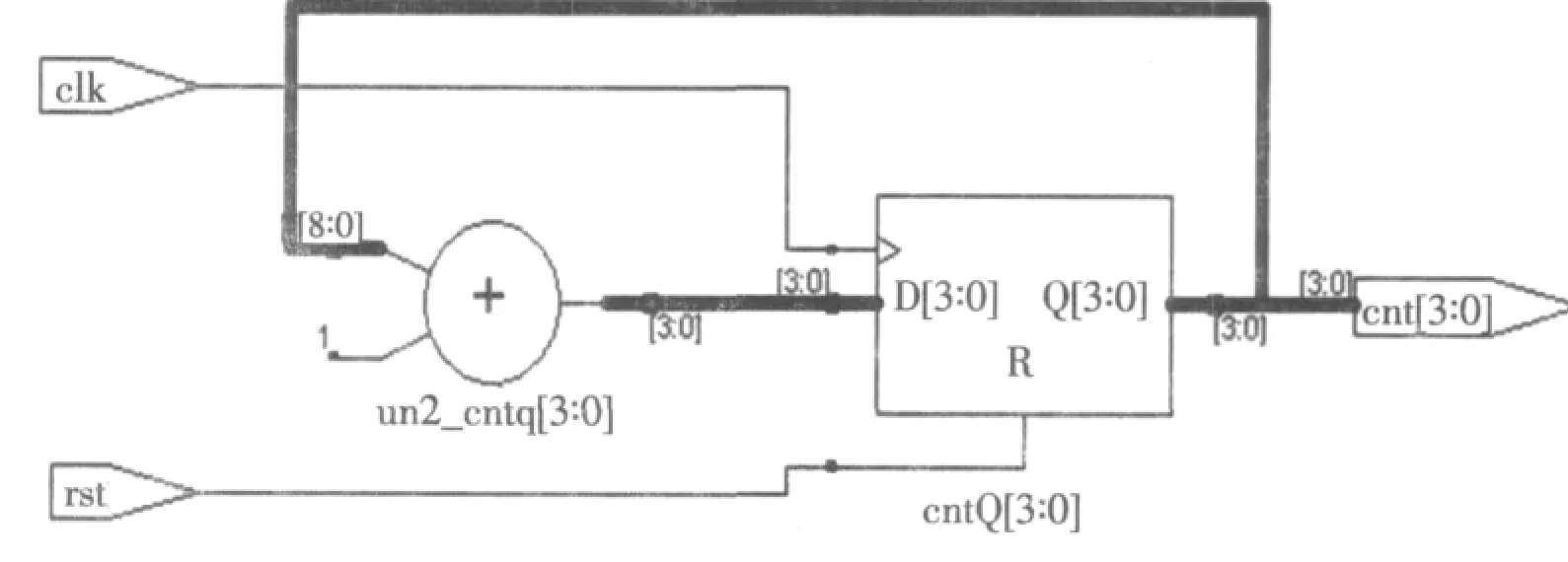

从波形上可以看到输出端口cnt反复循环输出0~9这10个数字。普通计数器的RTL(寄存器传输级)结构图如图2所示[7]。可见该计数器由四位加法单元和四位触发器构成。有两个输入端口:时钟输入clk和复位信号输入rst。

图2 普通计数器RTL结构

1.2 约翰逊计数器

约翰逊计数器是一种移位计数器,采用的是把输出的最高位取非,然后反馈送到最低位触发器的输入端。也称为扭环形计数器。它在每个时钟下只有一个输出发生变化[8]。

约翰逊计数器没有有效利用寄存器的所有状态,假设最初值或复位状态为0000,则依次为0000、0001、0011、0111、1111、1110、1100、1000、0000如此循环。

再者,如果由于干扰噪声引入一个无效状态,如0010,则无法恢复到有效循环中去,需要加入错误恢复处理。

2 分频器

分频器有整数次分频器和小数次分频器之分。对于整数次分频器又有奇数次和偶数次分频器。这里只讨论整数分频。

2.1 偶数次分频

偶数次分频通过计数器计数是完全可以实现的。如进行N次偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频[9]。基于此思路的代码见注释①。

从如图3所示仿真波形上可以看到,通过计数器计数,每计数3次,输出时钟反相一次,从而使输出时钟为输入时钟的1/6,完成了6分频,并且占空比是50%。

图3 偶数次分频仿真波形(6分频)

2.2 奇数次分频

奇数次分频归类为一般的方法为:对于实现占空比为50%的N次奇数分频,首先进行上升沿触发进行模N计数,计数从零开始,到(N-1)/2进行输出时钟翻转,然后经过(N+1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。再者同时进行下降沿触发的模N计数,类似翻转生成占空比非50%的奇数n分频时钟。两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟[10]。基于此思路的代码见注释②。

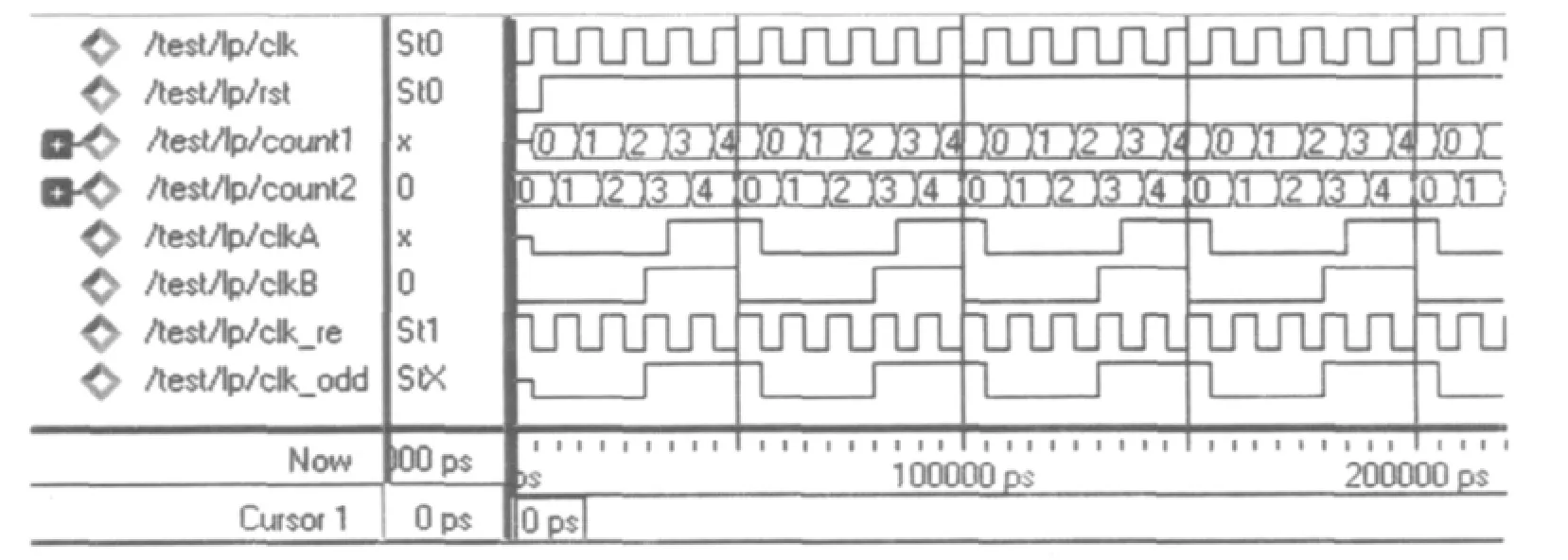

从如图4仿真波形上可以清楚地看到count1和count2两个计数器从1到4的计数过程,以及分别对应clk时钟和clk_re时钟计数所产生的clkA和clkB两个中间时钟,对这两个中间时钟相或的到最终所要的5分频输出时钟clk_odd,并且占空比是50%。

图4 奇数次分频仿真波形(5分频)

对该 5次分频电路进行软件综合 (synopsys_DC),获得RTL结构图如图5所示。

图5 分频器综合结果—RTL结构图

可以看到该逻辑电路是由若干与非门、或非门、反相器、或门以及D触发器构成,是典型的数字电路。该电路再经过后续软件进行布局布线、后仿真、时序分析、生成版图,就可以获得ASIC单元电路,应用到ASIC设计制造之中。

3 结语

本文详细给出了偶数次分频和奇数次分频的通用Verilog代码,并给出了相应的解释,通过了ModelSim的仿真。从仿真波形上看,两段代码均正确无误的完成了预期的功能。可见两段代码可以作为设计模版提供给其他数字逻辑设计人员直接调用,或者作为库文件使用。

注释:

①偶数次分频器代码

module even_division(clk,rst,count,clk_odd);/*定义模块 */

input clk,rst; /*输入端口*/

output clk_even;//输出端口

output[3:0]count;//输出端口

reg clk_even;//寄存器变量

reg[3:0]count;//寄存器变量

parameter N=6;//定义参数 6分频

always@(posedge clk)

if(!rst) //复位所有输出寄存器

begin count<=1'b0;

clk_even<=1'b0;

end

else if(count< N/2-1)begin //0~N/2-1计数,对本例为0~2计数

count<=count+1'b1;//计数器加1

end

else begin

count <=1'b0;//计数器赋零

clk_even<=~clk_even;//输出时钟反相end

endmodule

②奇数次分频器代码

module odd_division(clk,rst,clk_odd);

input clk,rst;//定义输入时钟和复位信号

output clk_odd;//定义输出时钟

reg[3:0]count1,count2;//定义两个计数器

reg clkA,clkB;//定义两个中间时钟

wire clk_odd,clk_re;//定义输出时钟和反相输入时钟为连线型变量

parameter N=5;//定义参数为5,即5分频电路

assign clk_re=~clk;//将输入时钟反相,赋值给clk_re

assign clk_odd=clkA|clkB;//给出输出时钟的表达式clkA和clkB相或

always@(posedge clk)

if(!rst)

begin count1<=1'b0;clkA <=1'b0;//复位时钟clkA和计数器count1

end

else if(count1<(N-1))//开始 0~N-1 计数

begin count1<=count1+1'b1;

if(count1==(N-1)/2)//如果计数器count1=(N-1)/2,时钟clkA反相

begin clkA<=~clkA; end

end

else begin clkA<=~clkA;count1<=1'b0; /*否则时钟clkA反相,计数器count1归零*/

end

always@(posedge clk_re)//反相时钟工作

if(!rst)

begin count2<=1'b0;clkB<=1'b0;//复位时钟clkB和计数器count2

end

else if(count2<(N-1))//开始 0~N-1 计数

begin count2<=count2+1'b1;

if(count2==(N-1)/2)//如果计数器count2=(N-1)/2,时钟clkB反相

begin clkB <= ~clkB; end

end

else begin clkB<=~clkB;count2<=1'b0;

//否则时钟clkB反相,计数器count2归零

end

endmodule

[1]乔庐峰.Verilog HDL数字系统设计与验证[M].电子工业出版社,2009:106-125.

[2]王金明,杨吉斌.数字系统设计与Verilog HDL[M].电子工业出版社,2002:182-235.

[3]潘 松,黄继业,潘 明.EDA技术实用教程:Verilog HDL版[M].4版.科学出版社,2010:300-340.

[4]李俊一,牛萍娟.基于Verilog HDL设计的多功能数字钟[J].微计算机信息.2006,22(11):44-50.

[5]Sanir Palnitkar,夏宇闻,胡燕祥.Verilog HDL数字设计与综合[M].2版.电子工业出版社,2009:240-260.

[6]约瑟夫·卡瓦纳,陈亦欧.Verilog HDL数字设计与建模[M].电子工业出版社,2011:305-326.

[7]沈 理.Verilog RTL模型[J].同济大学学报:自然科学版,2002,30(10):28-33.

[8]李勇坚,何积丰,孙永强.Verilog操作语义研究[J].软件学报,2002,13(10):53-62.

[9]刘小平,何云斌,董怀国.基于Verilog HDL的有限状态机设计与描述[J].计算机工程与设计,2008,29(4):56-60.

[10]俞莉琼,付宇卓.有限状态机的Verilog设计与研究[J].微电子学与计算机,2004,21(11):20-25.