一种高精度带隙基准电压源电路设计

2013-09-26李俊李新

李俊,李新

(沈阳工业大学 信息科学与工程学院,辽宁 沈阳 110870)

基准电压源广泛应用于A/D、D/A转换器、开关电源以及各种通信电路,它的电源噪声抑制能力与稳定的温度特性是影响A/D,D/A速度与精度的重要因素,甚至影响整个系统的性能,良好的基准电压源设计才能满足需要[1]。带隙电压基准(BGR)技术日趋成熟,具有较高精度,较低功耗的BGR在电路中被广泛应用[2-3]。

利用双极型晶体管的基区-发射区电压差ΔVBE在不同电流密度偏置下具有正温度系数,而其本身的基区-发射区电压VBE具有负温度系数,这两个电压线性叠加,得到较合适的近似零温度系数的基准电压源[4]。该带隙基准电压源电路增加了启动电路和PTAT电流产生电路,其中PTAT电流产生电路是该基准源的核心,通过对电路的分析与研究,给出了基于0.5 μm高压BiCMOS工艺下的带隙基准电压源的设计和仿真结果。

1 传统的带隙电压基准源

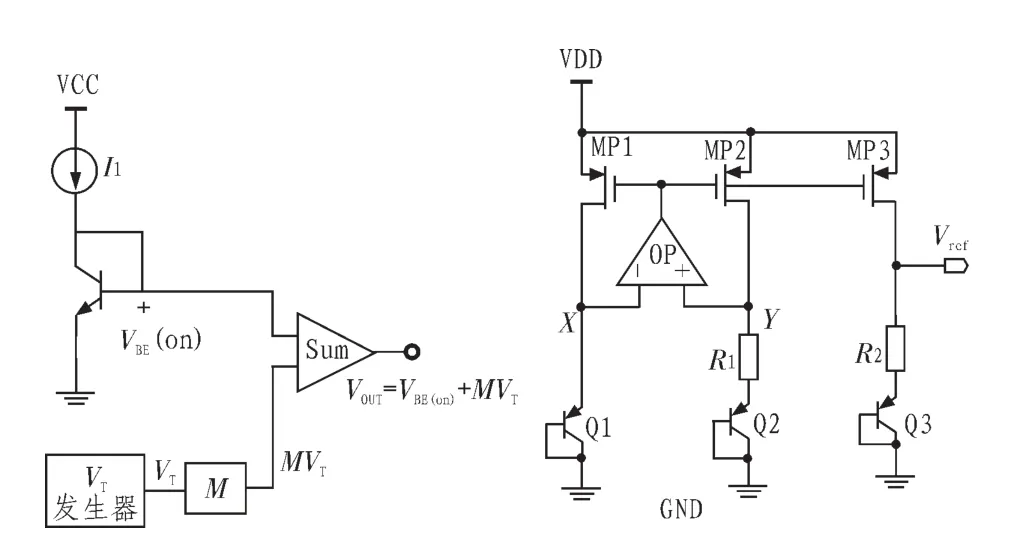

传统的带隙电压基准源原理图与电路结构如图1所示。

图 1(a)中,以 VBE(on)和 VT为基准的偏置源会有相反的TCF,输出电流可能以 VBE(on)和VT的某种复合电压作为基准源,如果复合方式得当,可使输出温度系数为零,该电路输出电压为:

图1 传统带隙基准电压源Fig.1 Traditional bandgap reference

从而确定要求的M值。

对于图1(b),已知两个双极晶体管工作在不相等的电流密度下,它们的基极-发射极电压的差值与绝对温度成正比。在图 1 中,如果 MP1,MP2是同样的晶体管(IS1=IS2),且偏置的集电极电流分别为nI0和I0,忽略它们的基极电流,那么

通过确定VBE(on)的温度系数,使输出电压与温度无关,即

双极晶体管的偏置电流实际上是与绝对温度成正比(PTAT)的,假设 MP1与 MP2为相同的管子,要使 ID1=ID2,电路必须保证 VX=VY。 所以,ID1=ID2=(VTlnn)/R,结果,使 ID3产生同样的特性,并将PTAT电压ID3R2加到基极-发射极电压上,因此输出电压为

只要保证(4)式中两项和是零,VBE3的值以及Q3尺寸的选择都有几分任意。实际上,由于晶体管之间的不匹配,以及R1的温度系数,ID5的变化会偏离理想的等式,给输出电压Vref带来误差。传统电路还存在电源电压较高,基准电压输出范围有限等问题,因此需要不断的改进与提高。

2 带隙基准电压源电路设计

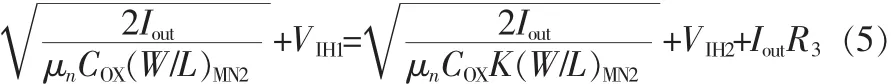

基于0.5 μm高压BiCMOS工艺下的带隙基准电压源电路如图2所示,电路由启动电路和带隙基准电压产生电路两大部分组成。

图2 带隙基准电路Fig.2 Circuit of bandgap

在与电源无关的偏置电路中,重要的问题是“简并”偏置点的存在,使电路有两种可能的状态:一种是工作状态,另一种是电路中没有电流流过,这是所不希望的状态[5]。增加启动电路,使该电路在电源上电时,能驱使电路摆脱简并偏置点,正常启动并稳定工作。图2中左半部分即为该带隙基准电压源的启动电路部分, 主要由 R1、R2、MP1、HAP1和 HAP2构成,其中HAP1与HAP2为高压非对称PMOS管,HAP1与HAP2构成电流镜,由于两者尺寸相同,HAP2的漏极电流与HAP1的漏极电流相等。当电路未进入工作状态时,HAP1与HAP2导通处于开启状态,通过增加VDD端电压,使得R1上压降逐渐增大,因此通过1的电流增加;由于1与2构成的电流镜的作用,通过R2的电流与R1上的电流相同,所以R2上电流也随着VDD端电压上升而升高,R2两端的电压也随之升高;当VDD增加到一定程度后,R1远离地端的电势将逐渐升高到该工艺下高压非对称PMOS管的截止电压,并保持稳定,此时R1上的电流也趋于稳定,R2上电流也将趋于稳定,在R2远离HAP2端将得到一个较稳定的开启电压,经计算并仿真测得这个电压为5.92 V。

对于电压产生电路,PTAT电流产生电路是该电路的核心部分,应用了 BCD工艺下的PNP管。主要由MP2、MP3、HSP3、HSP4、HSN1、HSN2、MN1、MN2、R3、Q1、Q2构成。 其中 MP2、MP3、HSP3、HSP4、HSN1、HSN2、MN1、MN2、R3构成与电源无关的偏置,Q1、Q2产生与温度无关的基准。

在偏置电流电路中,IREF通过某种方式由Iout得到,如果Iout最终与VDD无关,那么IREF则不受VDD影响,即与电源无关。当忽略MOS管沟道长度调制效应时,有Iout=KIREF,因为每个以二极管方式连接的器件都是由电流源驱动的,所以IREF近似的与电源无关[6]。 图 2 中 MP3、HSP4、HSN2、MN2的宽长比分 别 是 MP2、HSP3、HSN1、MN1的 二 倍 , 其 中 MP2、MP3、HSP3、HSP4与 HSN1、HSN2、MN1、MN2分别构成共源共栅电流镜,生成与电源无关的电流偏置,影响电流精度的关键因素就是漏-源电压,漏-源电压的变化会严重影响漏极电流的匹配。对于普通电流镜电路,因它们的漏-源电压不同,从而失配与沟道调制效应会造成组成电流镜的两个晶体管的栅-源电压有差异,从而导致输出电流发生很大变化。采用共源共栅电流源结构的电路,优点在于它会有一个很大的输出电阻,这在镜像电流源中非常重要,能够提高输出基准电压的稳定性,此外该结构能够减小沟道调制效应的影响,能够改善电源抑制和初始精度等电路的重要性能[7]。图2中经过MP4,与HSP5最后从HSN3中流出的电流和VT有关,所以电阻R4的压降也与VT有关,在做仿真的过程中,通过对R4的阻值优化,最后选择合适的电阻值使VOUT输出带隙电压。

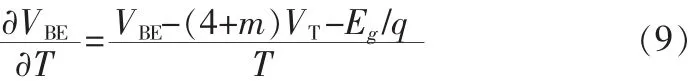

对于 MP2与MP3和MN1与 MN2,由于 R3的存在,根据电路图可写出VGS1=VGS2+ID2R3,假设MN2的宽长比是MN1的K倍,则有:

忽略体效应,则有:

于是得到Iout的表达式:

从式(7)可以看出,Iout与电源电压无关。 因此 MP2、MP3、HSP3、HSP4、HSN1、HSN2、MN1、MN2、R3共同构成了与电源无关偏置电流的产生电路。

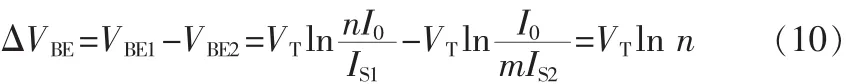

双极型晶体管的基极-发射极电压具有负温度系数,对于一个双极型晶体管可以写出CSBET其中TkT/q,设b为固定的比例系数,Eg≈1.12 eV为硅的带隙能量,则有

其中 m≈-3/2,又 VBE=VTln(IC/IS),将 VBE对 T 求导并结合式(8)推导可得:

式(10)给出了在一定温度T下基极-发射极电压的温度系数,从中可以看出,它与VBE本身的大小有关。当VBE≈750mV,T=300 K 时,∂VBE/∂T≈-1.5 mV/K, 可以看出 VBE具有负的温度系数。

当两个双极型晶体管工作在不相等的电流密度下时,假设基极-发射极电压分别为VBE1与VBE2,则二者的差值ΔVBE=VBE1-VBE2与绝对温度成正比。Q1与Q2为采用BCD工艺的pnp 三极管,对于 Q1、Q2有:

这样,VBE的差值就表现出正温度系数:

这个温度系数与温度和集电极电流的特性无关。

利用上面得到的正、负温度系数电压,结合公式(12)

通过确定α1和α2的值,即可得到零温度系数的电压源。

在设计的电路中,假设Q2的发射极面积是Q1的k(k>1)倍。Q1两端的电压等于Q2和R1两端的电压之和,则有:VBE1=VBE2+IBE2R3,可推出:

设 R4=LR3,IR4=2IR3,那么,输出电压为:

由式(13)与式(14)得

若获得温度系数为零的带隙基准电压,则:

3 电路仿真及结果分析

基于0.5 μm高压BiCMOS工艺,1.2 V带隙基准电压源基准电压的仿真结果如3所示。可以看出,通过给VDD端加上升的电压,电压从0 V上升到18 V,带隙基准电压源输出端的电压Vref随VDD端电压上升而逐渐升高,当VDD端电压上升到15 V左右时,电路进入工作状态,Vref端输出基准电压,此时,随着 的继续增加,ref不再变化,最后ref端电压保持在1.215 V。

图3 带隙基准电压Fig.3 Voltage of Band-gap

在做温度系数的仿真时,由于受到启动电路的影响,无法得到正确的温度系数曲线,在仿真时,通过将启动电路断路,使得基准电压随温度变化的曲线得以正常仿真。将带隙基准电压源电路在-40~85℃范围内进行仿真分析,得到带隙基准电压源的温度系数仿真结果如图4所示,可以看出,室温下带隙基准电压源的基准电压为1.215 0 V,85℃时带隙基准电压为1.216 05 V,可得该带隙基准电路的温度系数为7 ppm/℃。

图4 温度系数Fig.4 Temperature coefficient

4 结 论

通过对传统的带隙电压基准源[9]进行改进,增加启动电路,采用共源共栅结构的PTAT电流产生电路,设计了一种高精度、与电源和温度无关的具有稳定电压输出特性的带隙电压源。该设计电路在0.5 μm高压BiCMOS工艺下实现,结果表明在-40~85℃范围内该带隙基准电路的温度系数为7 ppm/℃,室温下的带隙基准电压为1.215 V。

[1]Hoi-Jun Yoo,Seung-Jun Lee,Jeong-Tae Kwon,et al.A precision CMOS voltage reference with enhanced stability for the applications to advanced VLSIs[C]//IEEE proceedings of International Conference,1993:1318-1321.

[2]Tadeparthy P.A CMOS bandgap reference with correction for device-to-device variation[C].Proc of the 2004 Int Symp Circ and Syst, Vancouver,Canada,2004:395-400.

[3]杨万杰.低供电电压基准电压源设计[D].湖南:国防科学技术大学,2011.

[4]史凌峰,王根荣,来新泉,等.新型过压保护电路设计[J].电子科技大学学报,2011,40(2):210-213.

SHI Ling-feng,WANG Gen-rong,LAI Xin-quan,et al.Novel over-voltageprotection circuitdesign[J].Journal ofthe University of Electronic Science and Technology of China,2011,40(2):210-213.

[5]R.Jacob Baker著.CMOS电路设计、布局与仿真[M].刘艳艳,张为,等译.2版.北京:人民邮电出版社,2008.

[6]毕查德.拉扎维,模拟CMOS集成电路设计[M].陈贵灿,程军,张瑞智,等译.西安:西安交通大学出版社,2003.

[7]Paul R.Gray,Paul J.Hurst,Stephen H.Lewis,等.模拟集成电路的分析与设计[M].张晓林等译.北京:高等教育出版社,2011.

[8]Razavi B.Design of analog CMOS integrated circuits[M].New York:McGraw-Hill,2001.

[9]李帅人,周晓明,吴家国.一种高精度低温漂带隙基准源设计[J].电子科技,2012(9):88-90,114.

LI Shuai-ren,ZHOU Xiao-ming,WU Jia-guo.Design of a highprecisionlowdriftbandgapreference[J].Electronic Science and Technology,2012(9):88-90,114.