Gbit收发器的特点及PCB制板建议

2013-09-13潘一飞

潘一飞,周 昊

(1.南京理工大学,南京,210094;2.南京陆军指挥学院,南京,210045)

0 引言

在计算机领域及其工业应用中,输入输出一直是非常重要的组成部分。但是,随着数字信号处理的信号越来越复杂,速度越来越高,可靠的板间数字通信也变得越来越困难了。如果还使用早期的并行总线系统,就会出现输入输出端口不够,端口间难以对齐等问题。而Gbit收发器以较大的数据流量,较少的输入输出端口数量,较小的电磁干扰和较低的价格成为当今解决高速大容量数据传输的一个重要方式。

1 Gbit收发器的特点

1.1 高速数据流

一些较大容量的可编程逻辑器件拥有20个以上的Gbit收发器,每个收发器带宽按10Gb/s来计算,总带宽可以达到200Gb/s。虽然这只是一个特例,但也可以看到Gbit收发器能够给我们带来的较大的带宽,可以用在高速大容量数据的传输上,比如高清的视频和音频等等。

1.2 端口数量少

当我们需要从一个器件上输入或输出高速的大容量数据的时候,往往首先会遇到输入输出端口数量不够的问题,而Gbit收发器能够用较少的端口给我们带来很大的带宽,下面是高清视频混合器应用中,使用并行数据流和使用Gbit收发器设计的串行数据流所用输入输出端口的比较:

?

可见Gbit收发器能够在很大程度上为我们解决端口数量的问题。

1.3 同步开关输出影响小

在使用并行总线系统的时候,我们一般都会使用同步开关输出,然而,很多开关的同时跳变往往会引起地面反射而引入大量噪声。为了防止噪声需我们往往会使用差分信号对,而这样又会使得输入输出端口加倍。

这种情况下可以考虑Gbit收发器,它是差分信号,端口又比较少,是很好的选择。

1.4 电磁干扰小

高速的串行链路往往要比并行总线链路辐射少,因为Gbit收发器的运行对信号完整性的要求特别高,就如一位专家所说:“电磁干扰的问题往往是信号完整性的问题。

1.5 价格低廉

用Gbit收发器的系统往往要比用并行总线的系统花费少一些,因为它的封装小,本身价格比较便宜。

对设计者来说,端口变少了,板子也容易设计。比如在一个视频混频应用中,并行总线系统需要比高速串行系统使用更多的集成电路,这样会使得整个板子的费用成倍增加。

2 印刷电路板设计

即使是有一个经验的印刷电路板设计者,对Gbit收发器的PCB设计也会十分小心和慎重。因为Gbit收发器速度非常高,对PCB布线有很高的要求,比如差分路径必须相匹配、PCB层数对阻抗的影响必须考虑、功率分布必须仔细严格地分析等,设计者往往要作数以万计的决策和平衡。为了帮助大家更好地进行Gbit收发器的PCB设计,下面提出几点建议:

2.1 材料选择

绝缘材料FR-4是当今PCB制版的主要材料,一些低损的替代品也是现成的。基本的原则是当传输的总长度小于50厘米,速度在3.125Gb/s以下的时候,FR-4可以满足要求。但是如果我们传输的路径比较长或者速度比较快的话,建议用高速材料(比如ROGERS 3450等)。

2.2 板材厚度

选定材料后就要进行板层的设计了,不同的PCB板层数就有不同的板层设计,但是我们必须牢记一点:Gbit收发器的走线层必须用相邻的电源层和地层包起来,防止外部电路和Gbit收发器走线电路相互影响,使得信号质量变差。

2.3 电源层和地层的设计

Gbit收发器中的这些模拟电压比较特殊,脉冲的宽度都是ps级别,因此要为每个模拟电源提供一个单独的平面;参考平面的话,要用隔离和过滤地平面;当信号领域没有达到千兆级的速度的时候,建议尽量不用数字电源平面。

2.4 过孔

Gbit差分路径尽量不要a跨层,如果确实需要层过度的话,我们必须格外小心。首先,我们必须把两个参考平面相连接以提供一个完整的返回路径,最好两个参考平面都是地平面,这样的话,返回路径就可以通过连接到最近的过孔来实现,既缩短了路径,也提高了可靠性。

如果参考平面不同(一个是地,一个是电源),那么在靠近传输过孔的地方,要放置一个0.01uF的电容,把不同参考平面的影响消除掉。

考虑高速信号从里层走到顶层的情况,这种情况下信号也会沿着过孔走到底层的焊盘,这对高速信号是有影响的。在这种情况下我们就需要使用背钻技术。如下图所示,在电镀以后,焊盘带来的影响就能够消除。

2.5 差分对之间的间隔

差分对与差分对之间不能紧紧地挨在一起,必须留有比较大的空间,最基本的原则是差分对与差分对之间的间隔至少是同一差分对正负信号线间隔的五倍。

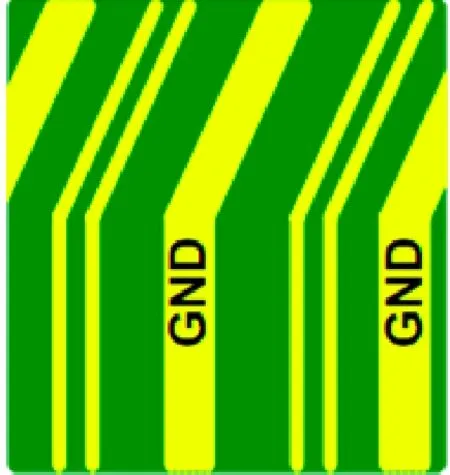

2.6 地隔差分对

如果不适用差分对间隔法的话,另一项技术就是地隔差分对法,就是在差分对与差分对之间用与差分对平行的地线相隔开,这样的屏蔽效果会更好,如下图所示。

图1 背钻技术示意图

图2 地隔差分对示意图

2.7 差分信号对

要想差分对运转的时候能够紧密耦合和高度匹配,差分路径长度是至关重要的。如果使用材料FR-4,差分路径差1/4厘米就能导致差分正负信号间差18ps,对Gbit信号来说,这已经能够影响到信号的完整性了。别以为1/4厘米听起来挺多的,如果你使用常规的布线方式从一个BGA(球栅阵列分装)到另一个BGA,差分对之间很容易就会有一个厘米左右的误差。所以建议大家一定要使用自动路径匹配PCB软件。总之,差分对之间的路径差一定要控制在1/8厘米以内。

2.8 差分布线的宽度和间隔

差分布线的宽度和间隔在PCB板的每一层都应该计算,当然制板厂家会给一些帮助和建议,但我们一定要做到心中有数,确保他们用的是比较专业的解决方案,再去根据他们的方案进行调整。一些制板规则甚至明确表示,这些参数的计算不应该让PCB制板厂家来计算。千万不要随便选一个差不多的PCB布线模型然后让生产厂家通过过蚀刻或者欠蚀刻来调整阻抗,这样做往往会带来很大的问题和隐患。最好是我们自己有专业的解决方案或拥有丰富经验的设计者。

[1]李大友.微型计算机接口技术[M]. 清华大学出版社,1998

[2]毛二可,龙腾.高速实时数字信号处理技术探析[J].电子产品世界,1998

[3]Lattice SemiConductor Corporation.Programming and Logic Analysis Tutorial..2005

[4]王幸之.单片机应用系统电磁干扰与抗干扰技术[M].北京航空航天大学出版社, 2006

[5]崔文进,高辉.可编程逻辑器件(PLD)在电路设计中的应用[J]. 电工技术. 2001(10)

[6]王建.基于SIP的视频会议系统的设计与实现[D].北京交通大学 2009

[7]张桂华.电磁干扰及抑制与防护[J].淮北职业技术学院学报. 2006(03)