卷积码的仿真和性能分析

2013-08-16马骏

马 骏

(长春职业技术学院工程技术分院,吉林长春 130033)

随着现代通信技术和计算机技术的迅速发展,每天都在不断涌现新的通信业务和信息业务,同时用户对通信业务质量和数据传输速率的要求也在不断提高。由于通信信道固有的噪声和衰落特性,信号在经过信道传输到达通信接收端的过程中不可避免地会受到干扰而出现信号失真,所以需要通过采用差错控制码来检测和纠正由失真引起的信息传输错误。

由于解码是在接收机进行解调之后执行的,所以信道编码是一种后检测技术。信道编码通常有两类:分组码和卷积码。分组码是把单个码字作为孤立的独立单元,编码过程所加入的冗余度、相关性局限于单个码字内,而码字之间是彼此无关的。卷积码的出现改变了这种状况。卷积码不是把信息序列分组后再进行单独的编码,而是由连续输入的信息序列得到连续输出的已编码序列。它的编码器也是每输入k个信息比特后,编码得到n个比特输出,但k和n通常很小,所以时延较短,特别适合以串行形式进行传输。与分组码不同,卷积码编码后的n个码元不仅与当前段的k个信息有关,还与当前的(N-1)段信息有关。卷积码的纠错性能随N的增加而增大,而差错率随N的增加而指数下降。在同样的复杂度下,卷积码相对于分组码可以获得更大的编码增益。

1 CDMA中卷积码的基本原理

卷积码不是把信息序列分组后再进行单独地编码,而是由连续输入的信息序列得到连续输出的编码序列。卷积码又称连环码,它和分组码有明显的区别。(n,k)线性分组码中,本组r(r=n-k)个监督元仅与本组k个信息元有关,与其他各组无关,也就是说分组码编码器本身并无记忆性。卷积码则不同,每个(n,k)码段(也称子码,通常较短)内的n个码元不仅与该码段内的信息元有关,而且与前面m段的信息元有关。通常称m为编码存储[1]。

卷积码(又称连环码)是由伊莱亚斯(P.Elis)提出的一种非分组码。它把k比特信息段编成n比特的码组,该码组不仅同当前的k比特信息段有关,而且还同前面的(N-1)个信息段有关联(N为大于1的整数)。通常,把卷积码记作(n,k,N),其中:k为输入码元数,n为输出码元数,N为约束长度,表示编码器的存储器级数。卷积编码属于信道编码,主要用来纠正码元的随机差错,它是以牺牲效率来换取可靠性,利用增加监督位,进行检错和纠错。卷积码的编码原理如图1所示。

图1 卷积码的编码原理

数字化移动信道中传输过程会产生随机差错,也会出现成串的突发差错。卷积码既能纠正随机差错,又具有一定的纠正突发差错的能力。纠正突发差错主要靠交织编码来解决。在CDMA移动通信系统中采用了卷积码和交织编码。因此,下面讨论这两种码的编码原理和纠错原理。

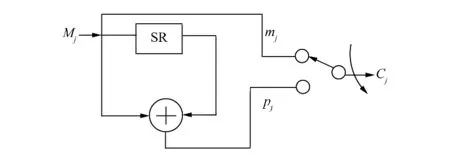

卷积码也是分组的,但它的监督元不仅与本组的信息元有关,而且还与前若干组的信息元有关。这种码的纠错能力强,不仅可纠正随机差错,而且可纠正突发差错。卷积码根据需要,有不同的结构和不同的纠错能力,但都有类似的编码规律。图2所示为(3,1)卷积码编码器,它由3个移位寄存器(D)和2个加法器组成。每输入1个信息元mj,就编出 2 个监督元 pj1,pj2,顺次输出成为 mj,pj1,pj2,码长为3,其中信息元只占1位,构成卷积码的一个分组(即 1 个码字),称作(3,1)卷积码[2]。

图2 (3,1)卷积码编码器原理图

由图2可知,监督元pj1,pj2不仅与本组输入的信息元Mj有关,还与已存入到寄存器的信息元mj-1,mj-2和mj-3有关。关系式为:

式(1)为卷积码的监督方程。

图3所示为(2,1)卷积码、约束长度k=2的编码器,它可在4比特范围内纠正一个差错。每输入一个信息元 Mj,编码输出为 mj,pj,其中 pj为式中mj-1为mj之前的信息元。假定输入信息元序列为 100(1为先输入),经过编码输出为110 100(其中1为最先输出)。下面具体分析卷积码编码过程。编码开始前,先对移位寄存器进行复位(即置0)。当输入第一个信息元“1”时,输出为1,由于pj=1⊕0=1,输出端开关接到pj,输出又为1。输出端开关速率是信息元速率的2倍,即每输入1个信息元,开关同步地转换1次。因此,上述编码过程可写成:

所以输出为11;

所以输出为01;所以输出为00。

图3 (2,1)卷积码(k=2)编码器

2 卷积码的实现

2.1 卷积码编码实现流程

程序开始先输入所要编写的器件,连接后卷积码进行计算,随后进行编码,并通过串并转换输出结果。然后进行引脚锁定,锁定成功后就进行下载,下载完毕,程序结束。图4所示为卷积码的总体流程图。

图4 卷积码的总体流程图

2.2 卷积码在CDMA中的应用

数字通信系统进行数据传输时,由于噪声干扰的影响,不可避免地会在接收端产生差错。为了在已知信噪比的情况下达到一定的误码率指标,在合理设计基带信号,选择调制、解调方式,并采用均衡措施的基础上,还应采用差错控制编码等信道编码技术来降低误码率。分组码和卷积码是差错控制编码的两种主要形式,在编码器复杂程度相同的情况下,卷积码的性能优于分组码。因此,在诸如GSM、IS95和CDMA2000等无线通信标准中,都应用了卷积码[3]。

本文设计的编码器原理图如图5所示,它为(2,1,6)卷积码编码器(图中T为移位寄存器)。k=1(一个输入端),n=2(两个输出端),N=6(5级移位寄存器)。

图5 编码器原理图

若输入信息序列为U=(u0u1u2…),则对应输出为两个码字序列:

对应的编码方程可写为:

式中:“*”表示卷积运算;G(1)和G(2)表示编码器的两个冲激响应。编码输出可由输入信息序列U和编码器的两个脉冲冲激响应的卷积得到,故称卷积码。由于编码器有5级寄存器,所以冲激响应至多可持续到6位,图1所示的卷积码编码器的两个冲激响应可写成:

若输入信息序列为:

U=(11010101),

则:

经过并串转换,最后输出的码字为:

C=(11110010001100100001000101)

2.3 仿真结果及分析

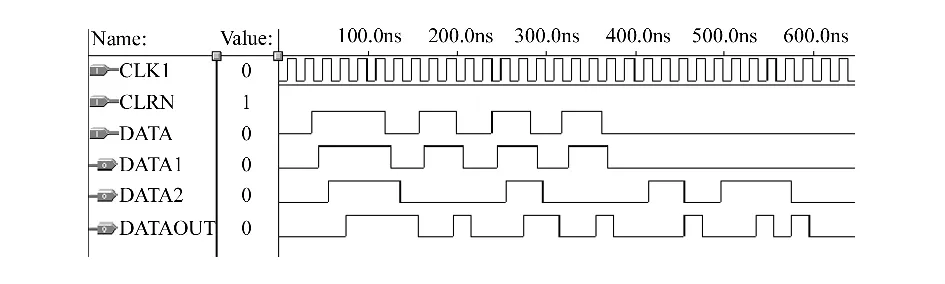

利用MAX+PLUS2开发工具进行编译和仿真,(2,1,6)卷积码编码器仿真波形如图6所示。

图6 (2,1,6)卷积码编码器仿真波形

图6 中“DATA”是数据输入端,系统输入的数据比特若为“11010101”,经卷积码编码器后,延时约80ns后“DATAOUT”输出的数据比特为“11110010001100100001000101”,仿真结果表明,编码器输出数据与理论设计完全一致。仿真结果见表1。

表1 (2,1,6)卷积码编码器仿真结果

2.4 卷积码的引脚锁定

卷积码编码器的引脚锁定如图7所示。

图7 (2,1,6)卷积码编码器引脚锁定

若目标器件是EP1K30,本实验根据模式1,引脚锁定为:用键1和2(PIO8― PIO11,PIO12―PIO15)控制DATA(十六进制),状态时钟CLK1接clock1,CLRN 接 clock0, 在 程 序 中 把“11110010001100100001000101”转换为十进制的数。锁存输出显示为数码8到数码1(PIO16―PIO47)。锁定好后下载到实验箱中,然后看实验箱上的结果和仿真的结果是否一致,包括和理论结果的比较,最后就可以确定下载成功。

3 结束语

本文对卷积码进行了仿真,并对卷积码的性能进行了分析,由于是在不同情况下选择卷积编码方案,所以卷积编码的性能也有所不同,因此卷积编码器的研究还有待于进一步深入,以期找到更多性能优良的解决方案。未来CDMA移动通信系统的发展,卷积编码器的研究是热点。

[1] 周海贤,许国良,姚伟.基于OCDMA的新型卷积码译码方案[J].通信学报,2009,34(3):26-28.

[2] 黄新林,王刚,刘春刚.基于FPGA的卷积码分组译码方法[J].吉林大学学报:工学版,2009,26(2):177-182.

[3] 龚建荣.现代电子技术[M].北京:人民邮电出版社,2008.