基于Cadence的数据采集系统信号完整性仿真与优化

2013-08-13李鹏飞孟令军乔文生

李鹏飞,孟令军,乔文生,于 磊

(中北大学a.电子测试技术国家重点实验室;b.仪器科学与动态测试教育部重点实验室,山西 太原 030051)

责任编辑:时 雯

20世纪70年代初发展起来的新型半导体集成光电器件,经过30多年的发展,IC输出开关速度不断提高,电子系统的规模越来越大,工作频率不断提高,信号传输速度也越来越快,为了保证信号传输的质量,出现了对信号完整性的考虑和设计上的优化。另外,对低功耗的高速信号传输器件(如FPGA)常见的内核电压为1.2 V,对外界环境的要求也越来越高,如系统能容忍的噪声裕量,这也突出了信号完整性问题。对于高速数据采集系统,数字逻辑电路的频率达到或超过50 MHz,信号传输速度较高,延迟等就相对减少,建立时间、保持时间均在皮秒级[1],从而增加了设计的复杂度。因此在高速数据采集系统设计时采用了对关键信号进行信号完整性的仿真,保证关键信号的传输质量,从而得出更为合理的设计。本设计采用具有较强高速信号仿真功能的Cadence软件,完成叠层参数、信号拓扑结构的建立以及布线等造成的影响、信号间的串扰等。

在高速数据采集系统设计过程中,信号完整性上主要解决3个问题:对关键信号建立正确合理的拓扑结构;满足系统相应时序间的配合要求(信号的建立时间、最小脉宽、保持时间以及相位叠加等);进行信号优化设计。

1 数据采集系统结构及原理

数据采集(DAQ)是指从传感器和其他待测设备等模拟和数字被测单元中自动采集非电量或者电量信号,送到上位机中进行分析、处理。本系统采用ADS8508芯片,是一种具有12位的模数转化和250 kHz高采样率的ADC芯片,然后将该信号送到FPGA中,本系统采用的FPGA选用Altera公司的Cyclone II系列EP2C8Q208。FPGA作为系统的核心组件,控制采集通道的换置、A/D转换器的启/停、数据转换后在内部FIFO中存放等。图1为多路数据采集系统电路连接框图。

图1 高速数据采集系统电路连接框图

该系统实现数据的多路选择、采集、预处理和编码功能。模拟信号源于上游各路传感器的模拟信号,经信号调理电路进行信号调理,通过多路模拟开关进行多路切换选通,将选通的多路信号输入模数转换器ADS8508,转换得到的模拟量传送到采集控制单元(FPGA)中。此外,采集控制单元还对数字信号进行适当的数据预处理,数据被存储在FPGA内嵌的FIFO[2]中等待Ft245读取。同时根据对FPGA内建的寄存器操作来实现采集系统的其他功能,如复位、标定等。

2 信号完整性分析

信号完整性即信号在信号线上的传输质量。问题的主要根源是信号上升时间的减小。即使布线拓扑结构设计保持不变,如果采用了信号上升时间很小的IC芯片,现有设计也将处于临界状态或者停止工作。在高速数据采集设计中主要考虑的信号完整性问题包括布线、阻抗匹配、串扰等。

2.1 布线

布线对信号完整性的影响主要包括延时和容性负载反射。实际操作中PCB布线会遇经过孔、焊盘、短的stub线等,这样会不可避免地引起PCB布线长短的不一致,造成信号传输的延时。此外,布线与过孔等相互之间均会产生寄生电容,必然对信号造成影响。走线中途的电容对信号的影响要从发射端和接受端两个方面分析,对起点和终点都有影响。因此发生容性负载反射,对信号产生影响。

在高速信号中传输信号,延时是影响信号完整性的一个考虑因素,在电子系统中,当传输信号在PCB走线上的延时超过相应信号的最小建立时间、最小脉宽、保持时间以及相位叠加等就会造成时序错误,造成信号传输质量下降。信号传输延迟主要取决于导线的长度和导线周围介质的介电常数。现今常见的PCB材料为FR4,其传输速度可达180 ps/in(1 in=2.54 cm)。对于同一块高速信号传输的PCB板,解决延迟问题可以通过以下途径:缩短信号收发端间的布线距离;对于时序相关的信号线布线长延时相差不能超过最小建立保持时间、最小脉宽以及保持时间等,从而保证信号传输质量。

在信号传输过程中,信号遇到寄生电容时,电容会快速充电,充电电流和信号电压上升快慢有关,充电电流公式为:I=C×dV/dt。在电容充电初期,阻抗很小,小于走线的特性阻抗[3]。信号在电容处发生负反射,这个负电压信号和原信号叠加,使得发射端的信号产生下冲,引起发射端信号的非单调性。同理,信号到达接收端后,发生正反射,反射回来的信号到达电容位置,同样发生负反射,反射回接收端的负反射电压同样使接收端信号产生下冲。

2.2 阻抗匹配

阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。信号传输过程中负载阻抗等于信源内阻抗(模与辐角分别相等),可以实现信号传输的完整性。

驱动源输出信号,经过的互连线可以等效为一个具有阻抗的网络。信号利用阻抗网络进行信息传播时,互连线构成的阻抗网络会随着信号的电压、电流变化引起瞬态阻抗的变化。这样会造成信号相位叠加的不一致性,造成部分能量会被反射,剩余的能量仍会继续传输。因此,在高频电路中合适的阻抗匹配是保证信号完整性不可缺少的一个考虑因素。

2.3 串扰

信号串扰是信号高速传输时,没有电气连接的信号线之间的电压和电流感应产生的电磁耦合现象,即能量传输网络间的耦合,造成高速信号传输上的失真。信号线之间的电压和电流感应产生的耦合可以等效为天线,产生交变磁场,处于磁场作用区域范围之内的其他信号线会感应出信号电压。串扰的强度取决于器件及导线的几何尺寸和相互距离。

3 数据采集系统仿真设计与优化

多路信号采集系统采用Cadence中的SigXplorer软件对进行信号完整性仿真及优化。为了验证系统方案的可行性,对系统前端信号进行调理、多路选择、信号隔离前后进行分步仿真研究,实时监测信号变化。

3.1 布线对信号完整性影响

多路信号采集系统中采用的模数转化芯片为ADS8508,PCB板设计时为保证单一网络的信号质量应尽量减少布线造成的延时,保证信号的完整性。本系统采用ADS8508芯片,当ADS8508正常工作时转化得到的数字信号在FPGA发出的Dataclk信号下降沿传送[4]。因此,对系统关键信号Dataclk进行信号完整性仿真及优化设计,分别选取布线长度 100 mil(1 mil=0.025 4 mm),1 000 mil,1 000 mil布线宽度为5 mil,8 mil,5 mil进行信号完整性测试比较。

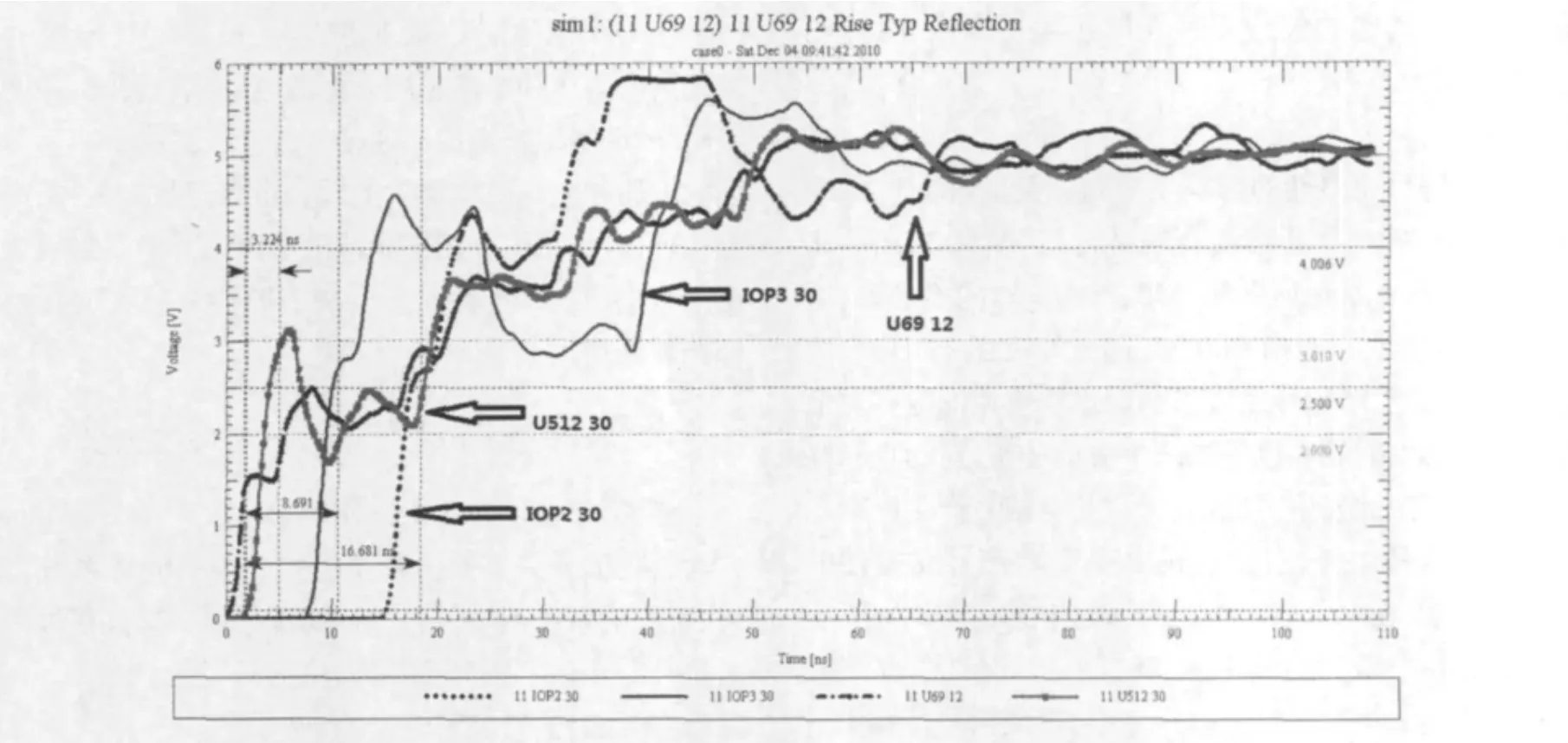

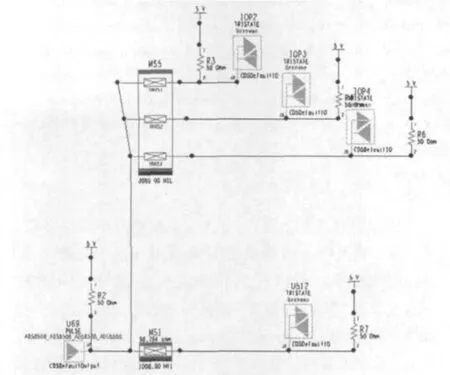

图2为ADS8508到FPGA布线的Dataclk信号中利用SigXplorer软件对进行仿真原理图。图3为ADS8508到FPGA布线的Dataclk信号中利用SigXplorer软件对进行仿真波形整体比较图。由图3可知,布线长度越长信号的质量越差,布线长度为100 mil、宽度为5 mil时,信号延时约为3.224 ns;布线长度为1 000 mil、宽度为8 mil,信号延时约为8.691 ns;布线长度为1 000 mil、布线宽度为5 mil时,信号延时约为16.681 ns,信号失真最大。

图2 Dataclk信号拓扑结构图(截图)

根据图2、图3可知,U69为ADS8508发出的信号波形图,U69i为PCB布线理想状态下0 mil时信号波形图,U512为ADS8508将信号传递给FPGA第77引脚信号波形图,假定布线10 000 mil时信号波形图,此时信号失真较小。IOP3为PCB布线50 000 mil时信号波形图,IOP2为PCB布线100 000 mil时信号波形图,显然PCB布线越长信号延时越大、完整性越差。

3.2 阻抗匹配大小对信号完整性

阻抗匹配(Impedance matching)主要用于传输线上,来达至所有高频的微波信号皆能传至负载点的目的,不会有信号反射回来源点,从而提升信号完整性以及电磁兼容性。

图3 Dataclk信号仿真波形图(截图)

在多路数据信号隔离采集系统PCB设计中,阻抗匹配是通过改变阻抗力来进行比较。要匹配一组线路,首先把负载点的阻抗值、传输线的特性阻抗值进行归一化。通过不同阻抗匹配比较,给出阻抗匹配对信号的影响程度,信号传输过程中负载阻抗和信源内阻抗之间的特定配合关系。

图4为晶振Clk信号到FPGA布线的中利用SigX-plorer软件对进行阻抗匹配仿真原理图。图5为晶振Clk信号到FPGA布线的中利用SigXplorer软件对进行阻抗匹配仿真下降沿放大波形图。

由图4、图5可知,阻抗匹配越大信号的质量越差,阻抗匹配为10 kΩ时,信号衰减最明显,幅度小于1 V。

图6为ADS8508的Dataclk信号到FPGA布线的中利用SigXplorer软件对进行信号串扰仿真原理图。

图7为ADS8508的Dataclk信号到FPGA布线的中利用SigXplorer软件对信号进行串扰仿真整体波形放大图。

图4 Clk信号阻抗匹配拓扑结构图(截图)

图5 Clk信号阻抗匹配下降沿放大波形图(截图)

图6 Dataclk信号串扰拓扑结构图(截图)

由图6、图7可知,信号单独走线的质量远比信号相互间串扰走线高。信号U512为单独走线,IOP2/3/4为互相并行走线[5],显然当信号并行走线时,信号完整性较差。只要有电流的存在,就会有磁场存在;电流发生变化,磁场也发生变化,电磁兼容性就降低。

4 结束语

本设计采用FPGA作为控制核心单元进行高速数据采集,通过对信号完整性相关知识的了解,利用EDA工具(Cadence)对高速数据采集的关键信号进行了设计仿真及优化,分析和解决了实际电路中常见的几种信号完整性问题。通过对高速采集电路板级关键信号的仿真与优化,解决信号完整性、电磁干扰等问题,提高了信号的传输质量,保证了数据采集的精度。

图7 Dataclk信号串扰仿真波形放大图(截图)

[1]李新,张琳.利用Cadence Allegro进行PCB级的信号完整性仿真[J].现代电子技术,2002(6):83-85.

[2]张磊,雷震.高速电路设计和信号完整性分析[J].电子技术应用,2001,27(6):70-73.

[3]李晓娟,刘学斌,胡炳,等.基于FPGA的CCD相机高速数据记录系统[J].科学技术与工程,2007,19(7):4879-4884.

[4]李德明,张法碧.一种基于FPGA的双音多频信号设计[J].电视技术,2011,35(21):48-50.

[5]朱志强.信号完整性仿真自动化技术基于Cadence软件的应用与研究[D].西安:西安电子科技大学,2007.