基于FPGA的雷电定位系统高精度时标设计*

2013-08-13肖坤峰孙秀斌杨崧令张广元

肖坤峰 ,孙秀斌 ,杨崧令 ,张广元

(1.成都信息工程学院 电子工程学院,四川 成都610225;2.中国气象局大气探测重点实验室,四川 成都610225)

雷电是伴随着强对流天气过程而发生的一种长距离放电现象,因其强大的电流、炙热的高温、猛烈的冲击波及强烈的电磁辐射等综合物理效应而能够在瞬间产生巨大的破坏作用。据不完全统计,我国每年因雷电灾害造成人员伤亡 3 000~5 000人,财产损失 50~100亿元。为了降低雷电灾害造成的损失,开展雷电探测方法的研究具有重要意义[1]。

利用接收到的闪电电磁脉冲对雷电进行探测,在甚低频段一般采用磁定向法(MDF)、到达时差法、磁定向和到达时差综合法(IMPACT);在甚高频段一般采用窄带干涉法或到达时差法[2]。在基于到达时差法的雷电定位系统中,其定位精度主要取决于系统中时间标记的精度。本文利用GPS全球定位系统的同步授时技术和可编程逻辑器件为探测站提供高精度的同步时间标记,并得到雷电脉冲到达各站之间的时间差,进而确定闪电发生的位置。

1 时差定位原理

图1 闪电辐射源与探测站的位置

如图1所示[3],假设闪电辐射源位于 S(x,y,z),探测站A、B、C、D 的空间位置分别为(xi,yi,zi)(i=0,1,2,3),其中 A站为中心站,其他3站为辅助站,则定位方程为:

其中,ri为辐射源与各站之间的距离;Δri为辐射源到达辅助站与到达中心站之间的距离差,τi为对应的时间差;c为电磁波传播速度。

将r0看作已知量,可以得到如下矩阵表达式:

式中:

如果H满秩,则利用Chart算法即可确定闪电发生的位置。

2 时标系统结构框图

现有的GPS系统提供同步脉冲输出(1 PPS)、UTC串行时间信息输出两种对时方式。同步脉冲输出时同步时钟每隔1 s的时间间隔输出一个精确的同步脉冲,该同步脉冲上升沿与UTC调协时间的秒变化同步。被授时系统在接收到同步脉冲后进行对时,以消除系统内部晶振时钟的走时误差。UTC串行时间信息是将UTC时间信息以串行数据流的方式输出。被授时装置每秒接收一次串行时间信息,即可获取GPS同步UTC时间。

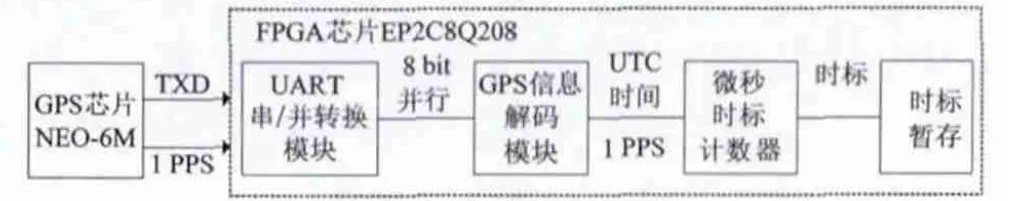

如图2所示,时标系统由GPS芯片NEO-6M[4]和FPGA芯片EP2C8Q208组成。NEO-6M通过CFG_COM0和CFG_COM1的电平设置串口输出波特率,TXD输出UTC串行时间,PPS则输出1 PPS秒脉冲。FPGA首先将接收到的串行UTC数据进行串/并转换;然后对得到的并行数据进行解码,提取同步UTC时间,同时检测秒脉冲,通过秒脉冲上升沿启动微秒时标计数器进行计数,并根据系统时钟将时标存入暂存寄存器中用以进行时间标记。

图2 时标系统框图

3 FPGA硬件逻辑设计

Altera公司的CYCLONE2系列FPGA芯片EP2C8Q208包含8 256个逻辑单元和两个PLL锁相环。时标系统通过Verilog硬件描述语言在FPGA内实现对GPS信息的串/并转换、数据解码、微秒时标计数和时标暂存等。

3.1 UART串/并转换模块

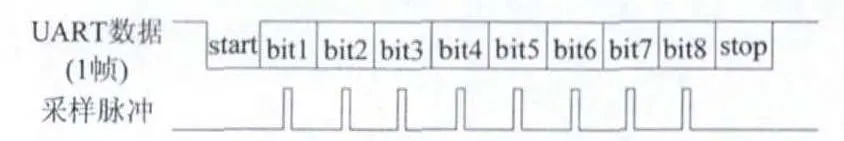

GPS芯片通过UART串口TXD发送NMEA0183格式的GPS信息[5-8]。UART串口发送数据格式如图3所示[9]。

图3 UATR数据格式

UART串/并转换包含下降沿检测、波特率发生器、并/串转换三部分。首先通过边沿检测捕捉UART数据格式开始位的下降沿,然后启动波特率发生器产生数据位采样脉冲进行串行数据采样,将串行的8 bit数据全部接收并检测停止位,若检测到停止位则将8 bit数据并行输出。

(1)下降沿检测

RXD信号线上电平由高变低表明1帧UART数据开始传输,边沿检测是用寄存器保存上一时钟周期RXD上的电平CURRENT,并与当前RXD上的电平NEXT进行逻辑运算。当下降沿到来时CURRENT为1,NEXT为0,逻辑运算之后的结果 RXD_START为 1,即表明检测到数据传输起始位,则启动波特率发生器产生数据位采样脉冲序列。图4所示为下降沿检测RTL图。

图4 下降沿检测RTL图

(2)波特率发生器

采用20 MHz晶体振荡器来产生波特率为9 600 b/s的数据位采样脉冲,通过计算(20×1 000 000)/9 600得计数值约为2 084,即计数器CLK_CNT值为1 042时(此时数据最稳定)产生一个周期的采样脉冲RXD_CLK。当8 bit数据位均采样完时,则停止波特率发生器,并等待捕捉下一帧数据的起始位。图5所示为波特率发生器RTL图。

图5 波特率发生器RTL图

(3)串/并转换

UART串行格式的每一帧数据中有8 bit数据位,经9 600 b/s的波特率发生器产生的采样脉冲序列进行数据位采样后依次存入一个8 bit的寄存器中,并在检测到停止位时通过输出端口并行输出8 bit数据到GPS信息解码模块,同时将标志位置为1,该标志位表明1帧数据转换完成,等待下一帧数据转换。

3.2 GPS数据解码模块

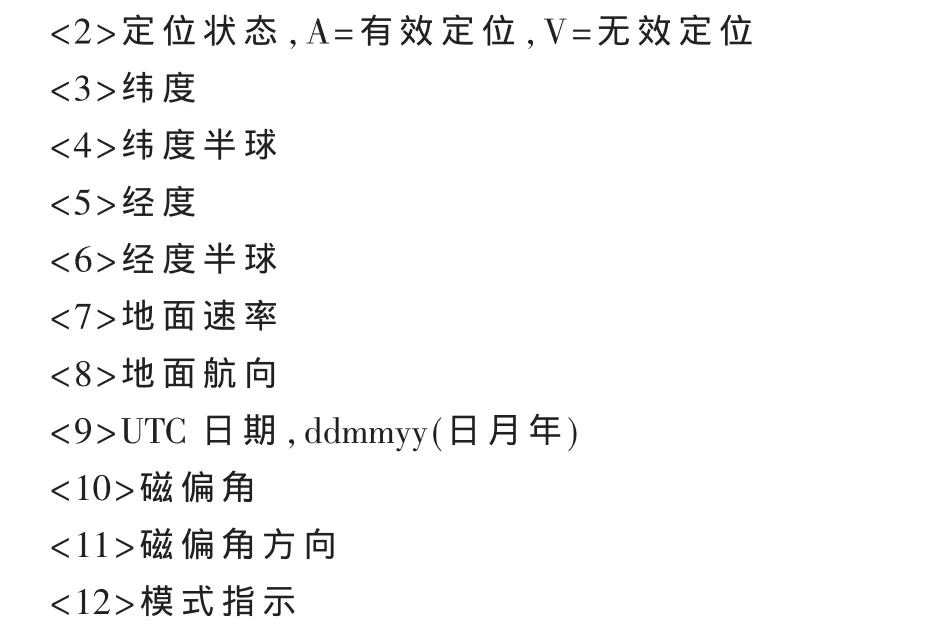

GPS发送的NMEA0183数据格式中,时标系统只需对GPRMC帧进行解析,得到UTC日期和时间信息。

GPRMC帧的构成如下:

从该帧中提取的数据包括<1>UTC时间、<2>定位状态和<9>UTC日期。UART串/并转换模块输出的8 bit数据为ASCII码值,通过有限状态机实现ASCII码序列检测器的状态转换,完成对GPS数据的解码,流程如图6所示。

图6 GPS数据解码流程图

当序列检测器检测到SGPRMC帧头时,根据数据帧中逗号的个数来识别所需的信息,如第1个逗号之后的UTC时间和第9个逗号之后的日期,并检测第2个逗号后的定位状态。当定位状态为A时,则是有效定位,GPS才会输出秒脉冲。

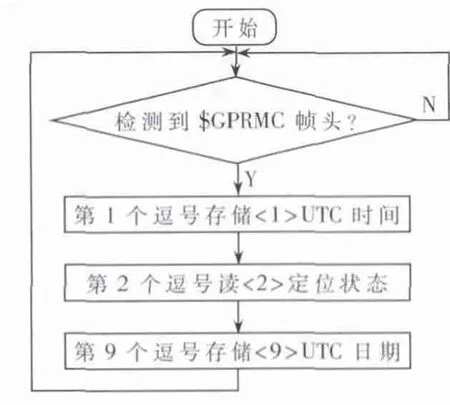

3.3 微秒时标计数器模块

GPS输出的UTC时间最小单位为秒,而基于到达时差法的雷电定位系统对时间精度要求较高。GPS秒脉冲的上升沿与UTC时间秒变化严格同步,精度一般为几十纳秒。利用系统时钟(10 MHz)在两个秒脉冲上升沿之间进行计数并与UTC时间组合,即可获取高精度的时间标记,如图7所示。

图7 微秒时标计数

秒脉冲是周期为1 s的方波,高电平持续约100 ms,其上升沿为秒脉冲输出的精确时刻。GPS的秒脉冲上升沿用边沿检测进行判断,当秒脉冲上升沿到来时将计数器清零并重新启动计数器进行计数,直至下一个秒脉冲上升沿到来。当采集到信号时,将当前微秒时标计数器的计数值与UTC时间组合输出,对信号进行时间标记。

3.4 测试与分析

时标系统中GPS芯片输出的秒脉冲信号如图8所示,可见该GPS接收机能够提供稳定的秒脉冲输出。

图8 GPS秒脉冲

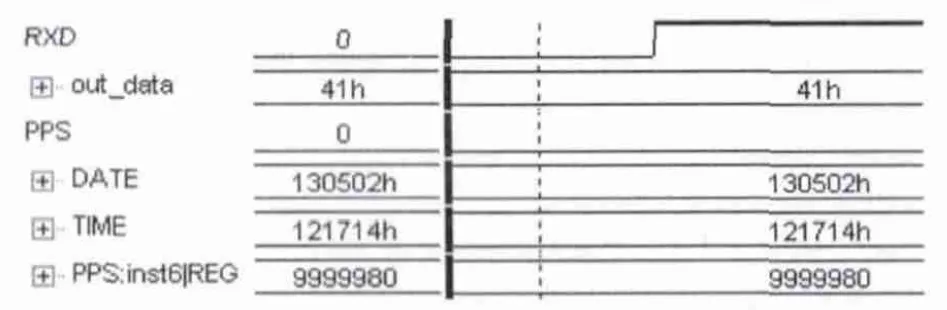

为了验证FPGA逻辑设计的正确性,利用Quartus II中的嵌入式逻辑分析仪Signal Tap对FPGA逻辑输出进行捕捉,如图9所示。

图9 FPGA逻辑输出

图9中,out_data表示 GPRMC帧中的<2>定位状态,其值为41h代表ASIIC字符A,表明GPS处于有效定位状态;若该值为56h则代表ASIIC字符V,表明GPS处于无效定位状态。DATE为<9>UTC日期,表示UTC日期为13年5月 2日。TIME为<1>UTC时间,UTC时间与北京时间相差8 h,表示UTC时间为12时17分14秒。REG寄存器的值为微秒时标计数器的计数值,其最大值稳定在 9 999 980左右,波动范围 1~2,该值与理论计数值10 000 000存在20的误差,此误差可能是由晶体振荡器的随机误差累积而引起。恒温高精度晶体振荡器具有很高的频率稳定度,晶振周期在短时间内保持不变,因此采用恒温高精度的晶体振荡器可以改善时标精度,使计数值更接近理论计算值。此外,GPS接收机秒脉冲也存在一定的随机漂移误差,选择性能更好的GPS接收机也有利于时标精度的提高。测试结果表明,该时标系统可以提供精度达微秒级的时标,能够满足雷电定位的需要。

本文通过对GPS接收机输出的时间数据进行解码,提取UTC时间,同时利用GPS提供的秒脉冲产生更精确的同步时间,并与UTC时间组成完整的时标。时标系统中的串/并转换、解码、计数和暂存等模块的硬件电路采用Verilog语言在FPGA上实现。在雷电定位系统中,采用该时标系统可以获得精度达微秒级的时间差,结合多站定位算法,可以有效地提高到达时差法的雷电定位精度,为雷电监测预警及其工程防护提供有力支持。

[1]李云敏,孙秀斌,杨崧令,等.云闪定位算法及误差分析[J].电子测量与仪器学报,2012,26(10):917-922.

[2]张义军,孟青,马明,等.闪电探测技术发展和资料应用[J].应用气象学报,2006,17(5):611-620.

[3]敖伟.无源定位方法及其精度研究[D].成都:电子科技大学,2009.

[4]U-blox.NEO-6数据手册[Z].2011.

[5]Navman.NMEA参考手册[Z].2005.

[6]曹洁,郭春禹.GSM模块对终端GPS数据的通信实现[J].电子测量与仪器学报,2010,24(11):1068-1073.

[7]贺良华,张杰,游钊.基于 FPGA的 NMEA解码和校正的算法设计[J].电力自动化设备,2010,30(2):127-130.

[8]李袆,王彪,黄海宁,等.基于 GPS授时的异地同步数据采集系统[J].测控技术,2006,25(3):40-42.

[9]蒋艳红.基于FPGA的UART设计与应用[J].计算机工程,2008,34(11):225-227.