基于边界控制的安全SoC芯片硬件结构设计

2013-08-13徐进辉戴紫彬何道君

赵 峰 ,徐进辉 ,戴紫彬 ,何道君

(1.解放军信息工程大学,河南 郑州 450000;2.北方信息技术研究所,北京 100072)

随着通信技术的发展,信息安全问题愈发突出。安全SoC是加密技术与片上系统SoC(System on Chip)技术相结合的产物,是执行密码运算、提供密码服务、保证数据安全的可信控制平台。采用安全SoC芯片作为密码处理设备具有安全性高、密码运算速度快、使用方便等特点。而随着侧信道能量攻击和电磁攻击等攻击技术的发展,安全SoC芯片的自身安全受到严重威胁,系统自身的安全成为未来信息系统设计的核心问题之一。参考文献[1]中对SoC芯片进行功能块划分,设计固件防火墙保护敏感信息的安全,可以对任何SoC设备进行保护。ARM公司2003年开发的Trust Zone技术[2]为用户提供了一个安全构架,能够抵抗多种安全威胁,但其结构要求微处理器提供特殊支持。

通过数据加密、在操作系统中植入安全特性等软件方法,在有限的嵌入式资源环境下大大增加了系统的复杂性和成本。由于其数据交互的实时性和开放性,使之无法从根本上实现真正的安全系统。增加安全硬件模块的方法灵活性较差,需要重新进行硬件设计才能满足新的安全功能,同时新增的硬件IP加重了设计开销,增加了系统功耗。

本文针对计算密集型任务和信息安全的系统问题,基于安全SoC芯片设计技术[3-4]和安全硬件结构思想,从系统、整体的角度来解决安全问题。

1 体系结构

1.1 总体结构

为了满足高性能密码处理需要,在SoC系统中集成更多的处理器核等硬件资源,MPSoC(MultiProcessor SoC)己成为片上系统发展的主流,越来越多面向特定应用的系统采用多核的方式来提升系统的计算能力[5]。多核系统中原来的软件工作量分到了多片处理器上,对单个处理器性能要求大大降低。而且可以灵活选择处理器以适应不同系统任务的需要,从而提高软件执行效率[6-7]。

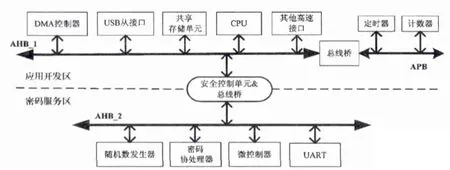

本文设计的多核SoC采用精简指令处理器+协处理器结构。如图1所示,通用RISC处理器负责数据流控制和数据分配,专用密码协处理器负责密码处理,两种类型处理器通过高带宽的多层系统总线连接,通过共享存储器的缓存区进行数据交互。整个芯片分为密码服务区和应用开发区,两个区域通过用安全控制单元和enhanced AHB-to-AHB(eH2H)总线桥[8]连接。从图1中可以看出,整个SoC相当于完整的个人终端计算机系统,而密码服务区相当于 TPM(Trusted Platform Module),是保障系统安全的关键。

图1 安全SoC系统架构

1.2 应用开发区

应用开发区连接各种通信接口,提供给用户进行开发。整个区域构成主处理器系统,在任务执行过程中,用户通过主处理器系统运行的操作系统对整个安全SoC芯片进行控制。主处理器系统负责整个应用开发区的设备管理、通信管理及控制任务的处理,并对应用程序进行调度和划分,是整个SoC系统的控制核心[8]。

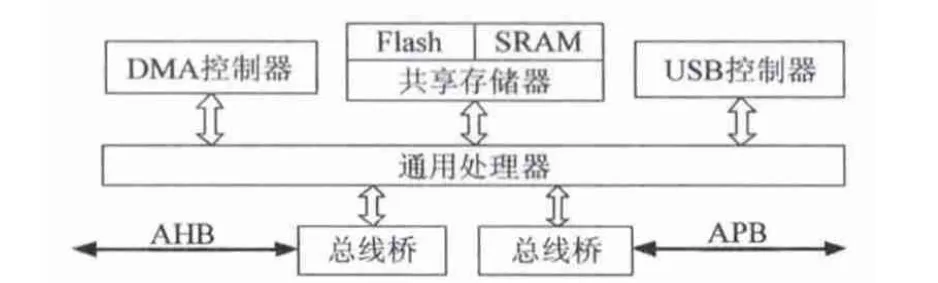

如图2所示,主处理器系统包括通用处理器、DMA控制器、高速系统总线、USB控制器、存储器控制器、低速外设总线与外部设备接口。DMA控制器接受通用处理器的配置控制,负责大批量数据的传输。存储控制器管理SRAM和Flash存储器,为提高存储控制器效率和工作频率,采用独立的通用存储控制器。USB控制器管理USB接口,负责与外部进行数据快速交换。

图2 主处理器系统

1.3 密码服务区

密码服务区提供密码处理服务,并存储密码算法、密钥等敏感信息。密码服务区构成协处理器系统,在应用开发区的请求下自动完成密码处理服务。

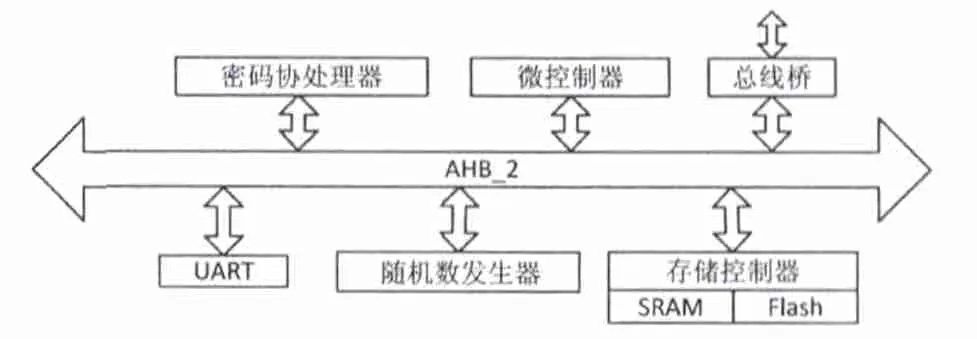

如图3所示,协处理器系统包括微控制器、局部总线、专用密码协处理器、随机数发生器、存储控制器和UART控制器。微控制器是密码服务区的控制核心,具有上电信息加载控制、数据调度控制等功能。随机数发生器提供协处理器加解密所需要的密钥。存储控制器主要存储密码算法、密钥和明文等敏感信息。协处理器系统通过UART接口注入算法配置信息、密钥、用户信息、设备信息等关键数据,并以密文的形式存放,主要完成主处理器系统划分好的加解密等计算任务,是整个SoC系统的计算核心。

图3 协处理器子系统

2 密码服务区的安全保护

2.1 安全威胁分析

SoC芯片面临的安全问题可归结为如下几个方面:

(1)SoC芯片的状态被非法读取或更改,如以各种手段破解敏感数据和用户密钥;

(2)SoC芯片被改造以欺骗应用终端或芯片发行方从而非法获得服务;

(3)SoC芯片被应用终端欺骗从而造成用户利益被损害。

上述几个问题中,解决好SoC芯片安全状态被非法读取或更改最为关键。在此基础上可以进行扩展以解决其他安全问题[2]。

为了保护密码处理过程中敏感信息的安全,方便用户使用和二次开发芯片,本文基于安全域划分技术在硬件层面设置专用的密码服务区和应用开发区,设计安全控制单元对来自CPU的总线请求进行安全访问控制过滤。

2.2 安全边界控制

融合安全机制和安全硬件结构的思想,采用安全边界控制——硬件隔离机制,限制应用开发区的程序对密码服务区的访问,保护敏感信息不被窃取。

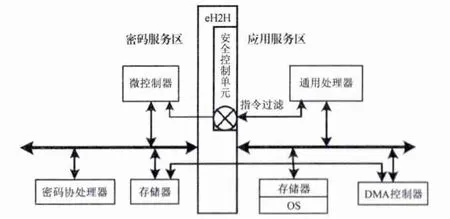

安全控制单元的工作原理如图4所示,应用开发区的数据通过DMA控制器快速传输到密码服务区进行密码处理,成功之后输出数据到共享存储器。由于恶意程序只能运行在应用开发区,而应用开发区对密码服务区的访问都要经过安全控制单元,安全控制单元过滤掉企图修改密码服务区的运行状态和对密码服务区进行数据读取的指令,从而保证了密码处理过程中敏感信息和解密数据的安全。

图4 硬件隔离机制

安全控制单元按照如下的安全规则拦截CPU的非法访问:

(1)如果应用开发区程序企图直接控制安全相关硬件模块,则阻止该访问,即安全相关的硬件模块对应的地址空间对于应用开发区程序是不可见的,应用开发区程序只能通关密码服务区的安全服务程序获得相应功能。

(2)如果芯片使用者企图通过CPU单元发出命令读取密码服务区的敏感信息或更改密码服务区的状态,则阻止该请求。

通常权限生成电路的设计方法主要有两种:

(1)查找表方法,即将地址和写使能信号作为输入,通过查表输出相应的控制信号。这种方法的优点是速度快,但需要事先将控制信号的值存储于表中,如果需要存储的内容较多,则可能消耗较多的硬件资源。

(2)比较器方法,即将对地址信号的读写操作与给定的权限范围进行对比,从而输出相应控制信号。这种方法由于要实现多次比较,耗费资源较大,也会带来较大延时。

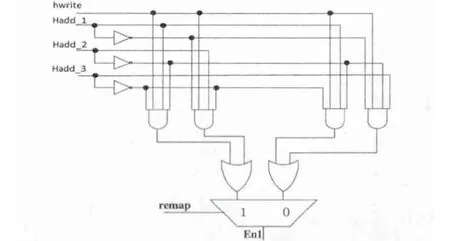

由于本文需要存储的控制信号量不大,而且要求尽可能地减小延迟,因此采用基于真值表的电路设计方法。将整个总线地址空间按设计要求进行划分,根据提出的地址分配表分别列出不同地址对应的访问权限真值表,从而设计对应的控制电路。

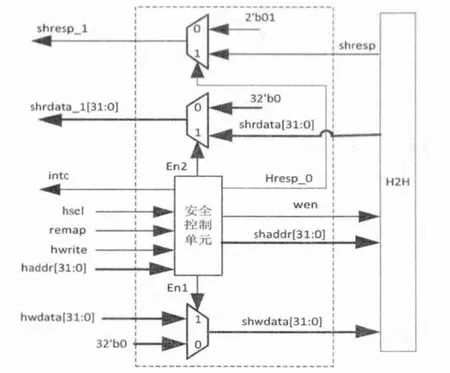

设计的安全控制单元如图5所示。当En1有效时,可以写入数据,否则输入数据为0。同理当En2有效时可以读取数据,否则读出数据恒为0。如果芯片进行了地址重映射,不论是存储器内部还是从设备地址重映射,安全控制单元都会在检测到地址重映射remap信号有效后对原来的地址权限做出更改。如果CPU的访问被隔离,安全控制单元会返回中断信号intc给中断向量控制器;置位传输响应信号shresp_0为01,告知CPU传输失败。

不同的地址分配表得出的硬件电路图不同,简化的En1硬件电路图如图6所示,hwrite为写使能,Hadd_1、Hadd_2、Hadd_3为地址分配空间的划分值。En1在remap信号的控制下对不同的地址有不同的权限值。密码服务区写信号wen En1与总线读写信号hwrite相与生成,shaddr地址信号则由总线地址锁存一级后直接生成。

图5 安全控制单元

图6 En1硬件电路

芯片的生命周期包括两个基本阶段,即调试开发阶段和发行使用阶段。在调试开发阶段,安全控制单元不发挥作用;当芯片有调试开发阶段进入发行使用阶段后,发行者在片内非易失存储中特定位置写入相关信息,安全控制单元就会按照上述安全规则拦截非法访问请求。

3 仿真验证

3.1 安全控制单元的功能仿真

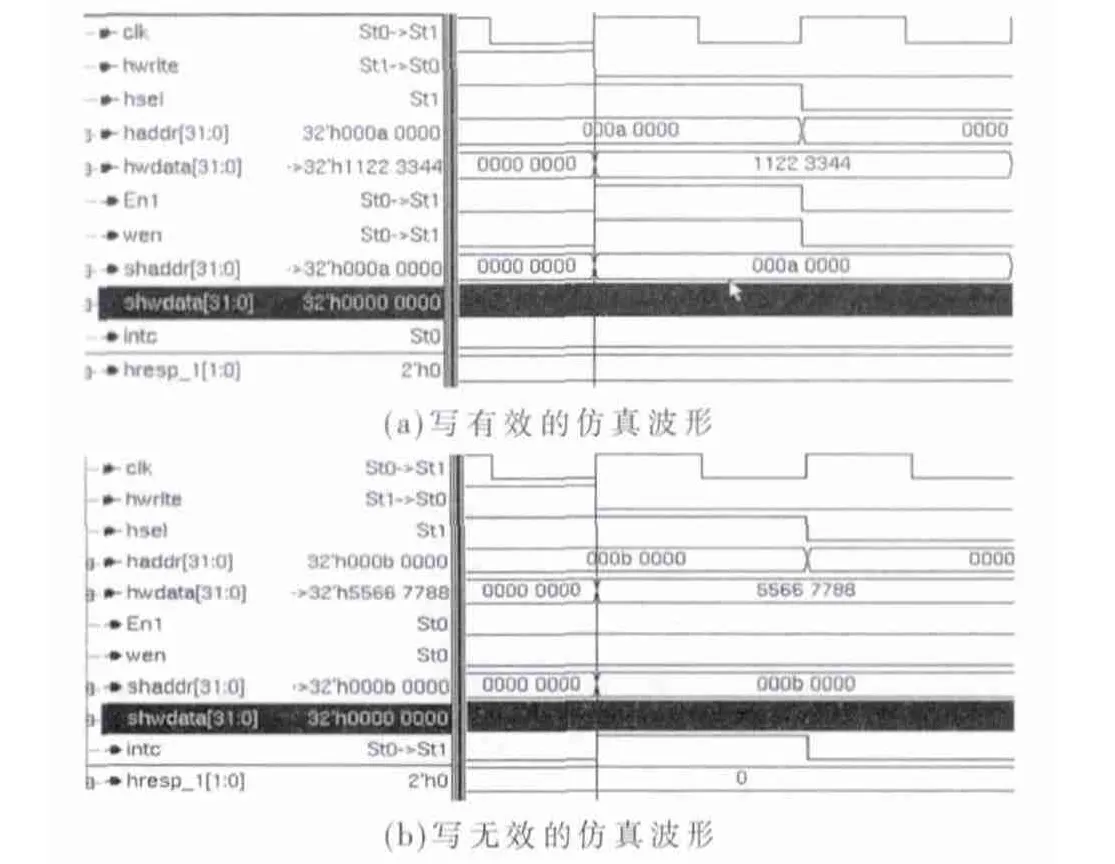

采用Verilog语言对SoC设计进行了RTL级描述,建立仿真模型,使用EDA软件对安全控制单元进行功能仿真。本文针对安全控制单元的仿真主要从两个方面进行:有效/无效的写操作、有效/无效的读操作。密码服务区的有效/无效写操作的仿真波形如图7所示。

在图7(a)中,对密码服务区进行了一次写操作,向地址0x000a0000写入数据0x11223344。根据设定的安全访问规则,由于具有该地址空间的写入权限,所以写使能信号有效,相应的数据被传送至数据输入端口,数据被正确写入。图7(b)中,向地址0x000b0000写入数据0x55667788,由于不具有对该地址空间的写入权限,因此写使能信号和En1无效,中断信号intc有效,相应的总线数据无法被传送至数据输入端口,数据锁定为0。

经过仿真验证读操作控制也可达到设计要求。

图7 仿真波形

综合上述仿真波形可以看出,设计的安全控制单元能够正确地实现边界控制,达到了保护密码服务区安全的目的。而且与软件方法相比具有先天的安全程度高、不容易被篡改、速度快等优点,有效提高了芯片的安全性和性能。与传统保护电路相比,最大优点在于避免了由于电路设计而引入额外的电路延时和面积增大,电路设计简单,功能完善,具有较高的实现价值,而且可以灵活更改以适应不同的安全需求。

3.2 性能分析

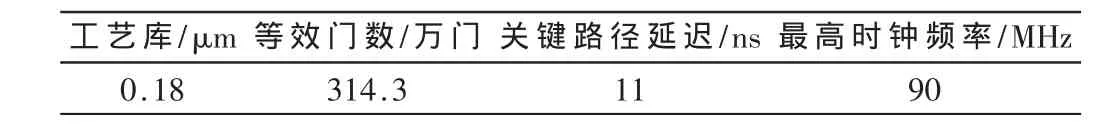

使用 EDA综合工具,采用0.18 μm CMOS工艺标准单元库及相应负载模型和RAM硬核对SoC进行逻辑综合,经过详细分析得出综合结果如表1所示。

表1 SoC综合结果

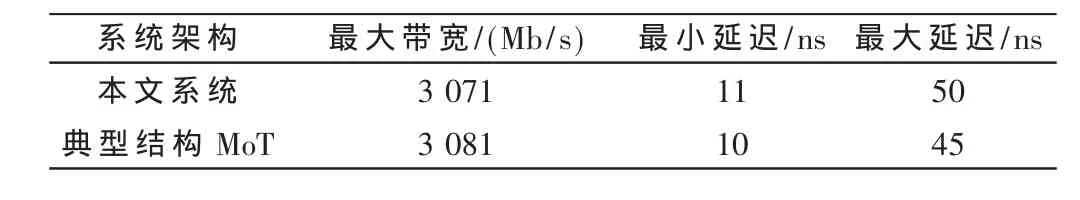

将本系统与典型的基于片上总线的片上互连方式[9](MoT)系统进行比较,主要比较平均带宽和平均延迟2个参数。所有带宽数据等效换算为系统在100 MHz频率下和32 bit数据位宽时的数据,结果如表2所示。可以看出,该SoC系统可在安全边界控制基础上实现较大的网络带宽和较小的延迟。

表2 互联架构实现性能比较

本文提出了多核异构安全SoC芯片的硬件结构,针对大批量数据处理和保护信息安全的需要,采用了层次化总线的互连结构进行优化设计。集成多个异构的处理器,将整个芯片划分为密码安全区和应用开发区,并采用安全边界控制——硬件隔离机制、安全存储管理等措施,可有效保证密码安全区的安全,提高整个系统的安全性和数据的完整性。

[1]KONDO H,OTANI S,NAKAJIMA M,et al.Heterogeneous multi-core SoC with SiP for secure multimedia applications[J].IEEE Journal of Solid-State Circuits,2009,44(8):2251-2259.

[2]童元满,陆洪毅,王志英,等.基于层次平台的安全SoC设计技术[J].计算机工程与应用,2008,44(17):10-14.

[3]Huang Wei,Han Jun,Wang Shuai,et al.The design and implement of a mobile security SoC[C].Solid-State and Integrated Circuit Technology(ICSICT),2010 10th IEEE International Conference 2010,Shanghai,2010:96-98.

[4]王雪瑞,何永强,公鑫.面向移动安全存储的密码SoC设计与实现[J].电子技术应用.2012,38(4):10-12.

[5]HALFHILL T R.The future of multi-core processors[EB/OL].(2007-12-31)[2013-07-08].http://www.Tensilica.com/uploads/pdf/Multicore_Microprocessor_Rept.pdf.

[6]刘继尧,刘雷波,伊首一,等.基于多层AHB架构的多核SoC 设计[J].计算机 工 程.2012,38(9):237-239.

[7]王超.异构多核可重构片上系统关键技术研究[D].合肥:中国科技大学,2011.

[8]赵为.面向媒体应用的多核SoC平台的设计与实现[D].浙江:浙江大学,2007.

[9]BALKA A O,Qu Gang,VISHKIN U.Mesh-of-trees and alternative interconnection networks for single-chip parallelism[J].IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2009,17(10):1419-1432.