基于CPLD的线阵CCD-TCD1501D驱动时序的设计与实现

2013-08-13林德辉

林德辉 ,谢 楠

(1.中国计量学院 机电学院,浙江 杭州310018;2.浙江水利水电学院 计算机与信息工程系,浙江 杭州310018)

电荷耦合器件CCD(Charge Coupled Device)作为一种光电转换图像传感器,在精密测量、非接触无损检测、文件扫描与航空遥感等领域应用广泛[1]。

线阵CCD正常工作的关键是其驱动电路的设计,即要产生CCD正常工作的时序。传统的时序生成方法有分立元件法、单片机实现的驱动法等,但均存在电路调试困难、时序波形难以满足线阵CCD使用要求的缺点。利用复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)产生CCD工作时序是目前常用的设计方法。CPLD具有集成度高、设计灵活等特点,能够保证驱动波形的严格匹配[2]。本文介绍了一种基于美国Altera公司的CPLD芯片EPM7128、利用VHDL语言编程实现TCD-1501D的驱动设计方法。

1 TCD1501D的驱动时序分析

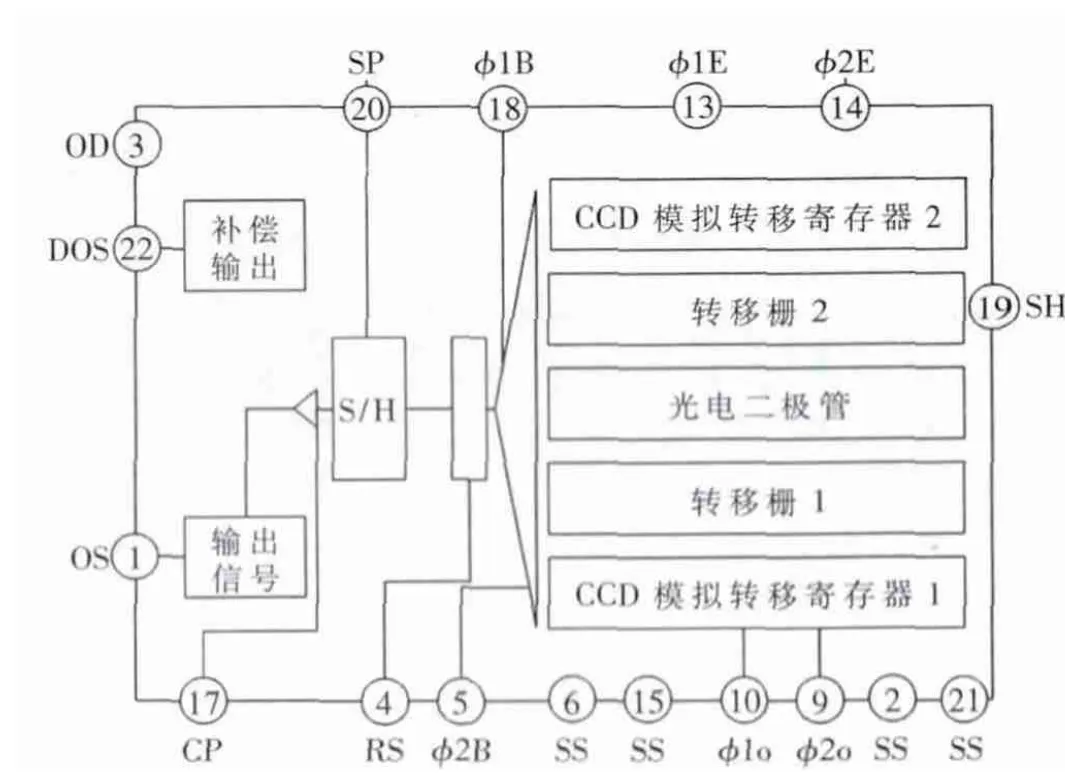

TCD1501D芯片是日本TOSHIBA公司生产的线阵CCD图像传感器,工作时有5 000个有效像元,其电路图如图1所示。

图1 TCD1501D电路图

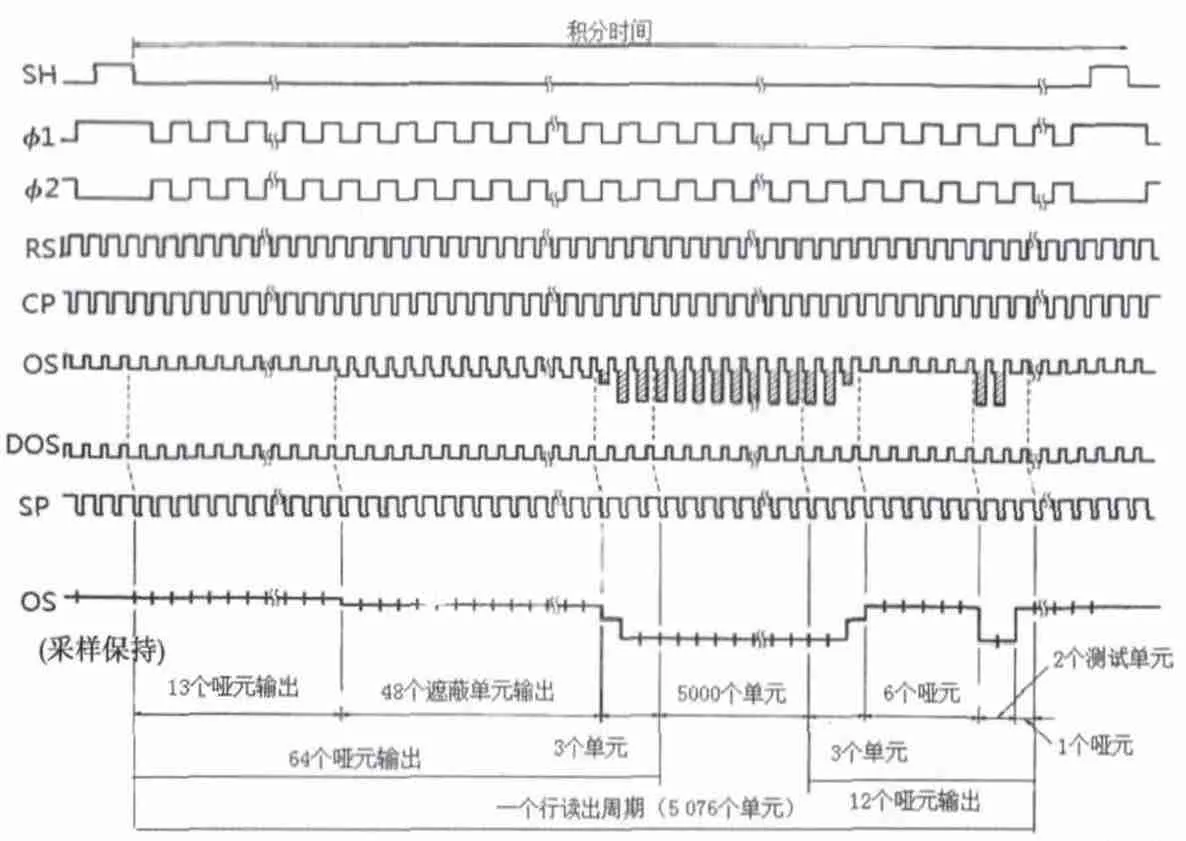

TCD1501D使用手册上要求驱动时序如图2所示[3]。

图2 TCD1501D的驱动时序图

由图2可以看出,TCD1501D工作所需的驱动信号有 10 路脉冲:φ1E、φ1o、φ1B、φ2E、φ2o、φ2B 6 路触发脉冲中 φ1E、φ1o、φ1B 时序相同(图2 中统一表示为 φ1),φ2E、φ2o、φ2B 时序相同(图2 中统一表示为 φ2),且 φ1、φ2两者反相;SH为转移脉冲,RS为复位脉冲,SP为采样保持脉冲,CP为箝位脉冲。这10路脉冲之间有着严格的时序关系,在时序分析阶段还需要参考图3所示的时序图。

图3 TCD1501D驱动脉冲的时序要求

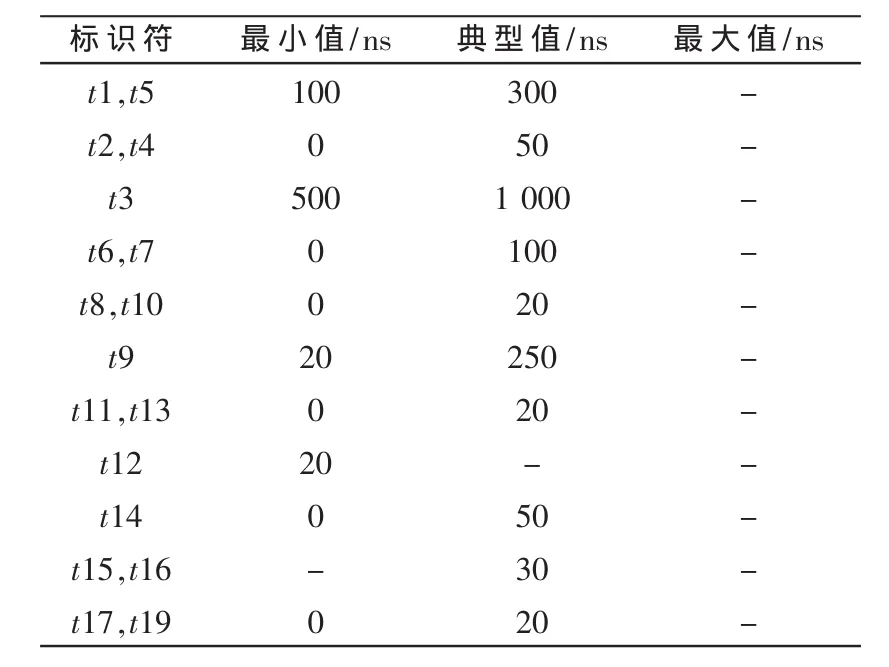

图3中时序的时间约束如表1所示。

表1 时序图中的时间约束表

根据图2、图3和图4即可进行时序波形的设计,由于 φ1E、φ1o、φ1B 时序相同,统一设为 φ1;φ2E、φ2o、φ2B 时序相同,统一设为 φ2。 本系统设计中硬件电路板上CPLD芯片EPM7128晶振时钟频率为16 MHz,每个时钟周期是62.5 ns。SH脉冲根据图3典型持续时间为 1 000 ns;φ1的第一个宽脉冲设计为 1 500 ns;RS工作频率为 1 MHz,对晶振时钟进行16分频即可实现,RS的占空比为75%,高电平持续时间为 750 ns,低电平持续时间为 250 ns;φ1、φ2 的工作频率为 0.5 MHz, 对全局时钟进行32分频即可实现,占空比为50%,且φ1、φ2反相;SP信号低电平持续时间为 62.5 ns,距离RS的下降沿为62.5 ns;CP的低电平持续时间为62.5 ns,即一个时钟周期。

2 基于CPLD的驱动时序的设计与实现

2.1 CPLD芯片的选型

本系统设计中采用Altera公司的EPM7128SLC84-15芯片,PLCC封装,84个引脚。其集成度高,逻辑密度达2 500个可用门,128个宏单元。芯片工作频率达147.1 MHz[4]。

2.2 电源电路

本系统中混合了多种电压,其中CCD为12 V供电,CCD的驱动脉冲电压为 5 V,而EPM7128电压为 3.3 V。在电源电路的设计中,采用外部直流稳压源为系统提供12 V和5 V电压,比较低的3.3 V电压由LT1764转换(5 V转 3.3 V)得到。

2.3 软件开发环境

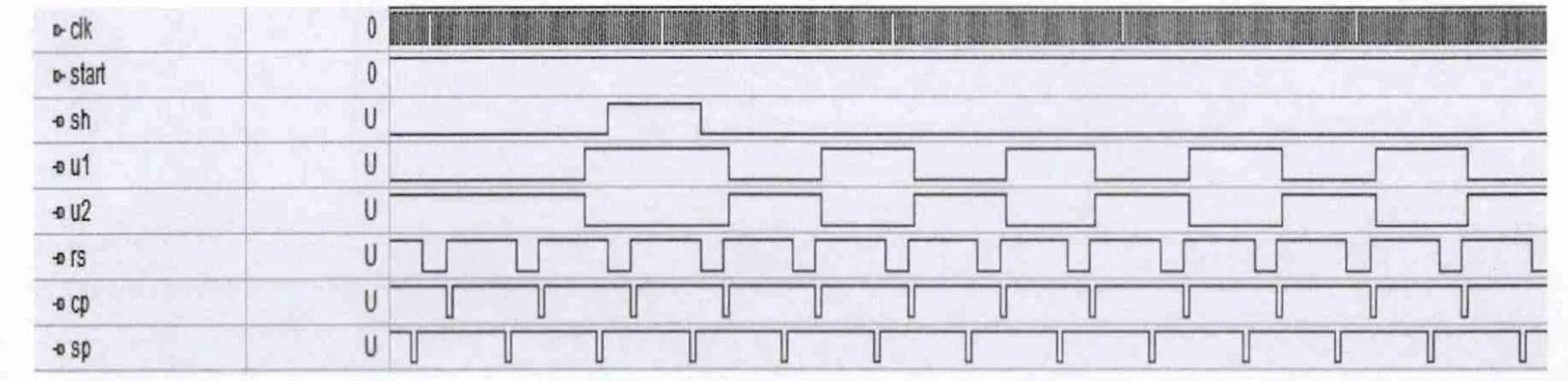

本系统中程序设计语言为VHDL,时序功能仿真软件使用Active HDL 9.1,下载软件使用Quartus II 5.0。整个系统功能仿真结果如图4所示。

放大后主要的6路输入波形如图5所示(实际上是10路,u1和u2相当于 φ1和 φ2, 这两路实际上是 6路信号),其中 clk为全局时钟,频率为 16 MHz,占空比为50%;start为启动信号,当start信号从低电平变为高电平时系统开始工作;rs为复位脉冲,sh为积分脉冲,cp为箝位脉冲,sp为采样保持脉冲。在利用Quartus II 5.0综合仿真的过程中需要绑定引脚,其中clk锁定在EPM7128SLC84-15芯片的83脚,其余信号只要选普通I/O即可。

3 实验结果

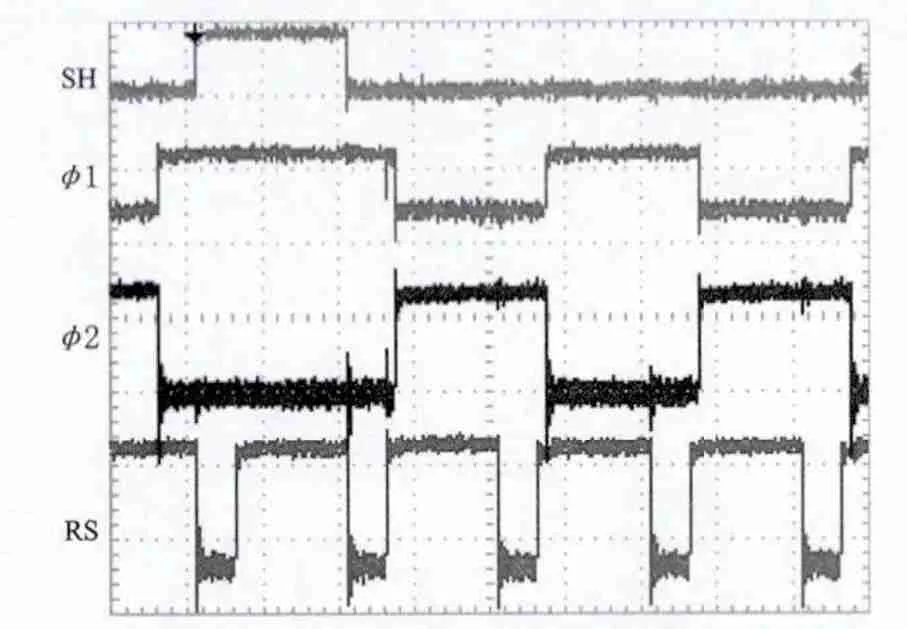

VHDL程序编译完成后通过JTAG口将生成的pof文件下载固化到电路板上的CPLD芯片中,就可以通过示波器在CPLD芯片的相应引脚上观看驱动波形。使用泰克公司的TDS2024示波器看到的驱动波形如图6、图7所示。图6为 SH、φ1、φ2和 RS的时序图,图7为 SH、φ1、RS和CP的时序图。从示波器上可以看出,波形和手册上要求的波形十分符合。

图4 系统仿真结果

图5 驱动时序功能仿真结果

图6 SH、φ1、φ2和 RS的时序图

图7 SH、φ1、RS和 CP的时序图

驱动设计完成后,CCD输出波形经反相驱动电路[5](以提高驱动能力,因为CPLD芯片输出为3.3 V,而CCD驱动脉冲为5 V)、放大电路、滤波电路等电路处理后即可正常工作。经调试,此系统已成功运用于卷纱机图像处理课题中,效果良好。此次设计中充分发挥了CPLD电路“可编程”的技术优势,具有灵活性强、集成度高、稳定性好的特点,相对于传统的驱动电路设计,极大地简化了设计过程和驱动电路结构。

[1]张旭.高速线阵CCD数据采集、传输与处理技术的研究[D].长春:长春理工大学,2008.

[2]潘松.EDA技术实用教程[M].北京:科学出版社,2006.

[3]Toshiba.TCD1501D datasheet[Z].2001.

[4]Altera.MAX 7000 programmable logic device family datasheet[Z].2001.

[5]辛凤艳,孙晓晔.基于FPGA和线阵CCD的高速图像采集系统[J].计算机技术与发展,2012,22(8):205-207,212.