DDC数字下变频ASIC电路设计

2013-08-13陈亚宁刘成玉徐叔喜

张 磊,陈亚宁,刘成玉,徐叔喜,汪 健

(北方通用电子集团有限公司微电子部,江苏 苏州 215163)

数字下变频器DDC(Digital Down Conversion)的主要作用是从输入的宽带高速数字信号中提取所需要的窄带信号,将其下变频到数字零中频,并降低数据的采样速率[1]。目前,数字下变频的实现方案主要有三种。第一种方案是使用通用的DSP处理器,用软件实现数字下变频。该方案灵活性强,但处理速度受限,需改进算法以提高速度。第二种方案是使用FPGA实现数字下变频,该方案也有较强的灵活性,但消耗的硬件资源较多。第三种方案是利用ASIC实现数字下变频的功能,该方案具有计算速度快和单片成本低等优点[2-3]。

国外对数字下变频的研究较早,市场上已经有很多成熟的数字下变频芯片。但是国内研究数字下变频技术起步较晚,技术较落后,没有成熟的数字下变频芯片[4]。在需要使用数字下变频模块的场合常采用FPGA厂商设计工具的IP核,使用十分不方便。因此,研究性能优秀、功能强大的数字下变频ASIC电路十分重要。

1 DDC数字下变频内部结构

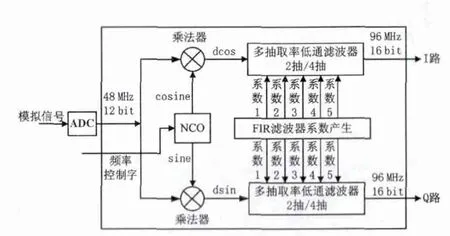

图1 DDC数字下变频内部结构

数字下变频电路主要是经过混频、抽取和滤波后,从ADC输出的数字信号中提取所需的窄带信号,降低采样速率,最终输出I、Q两路正交信号,以利于后续送入 DSP作进一步解调、解码等处理[5],其结构如图1所示。文中设计的DDC电路输入时钟为48 MHz,输入信号位宽为12 bit,中心频率为12 MHz,内部设置一个PLL锁相环,输出时钟频率为 96 MHz,输出I、Q两个支路位宽均为16 bit。电路内部主要由NCO(数字控制振荡器)、乘法器、FIR低通滤波器等模块组成,输入48 MHz信号分别与NCO产生的正、余弦信号相乘,混频产生两路48 MHz、12 bit的正交信号,分别进入各自的低通滤波器进行抽取、滤波,降低数据采样率,输出所需要的 I、Q两路正交信号。下面将分别介绍各个模块。

2 NCO设计

NCO数控振荡器主要用于产生正交的本地载波信号。NCO的主要优点是频率分辨率高,相位精度高,生成的正交信号正交特性好以及可编程等,NCO的频率和相位控制是数字化的,因此可产生高精度的本地载波信号。NCO产生离散正弦信号最有效、最简便的方法是查找表法,即事先根据各个NCO正弦波相位计算好相位的正弦值,并将相位角度作为地址存储该相位的正弦值数据。

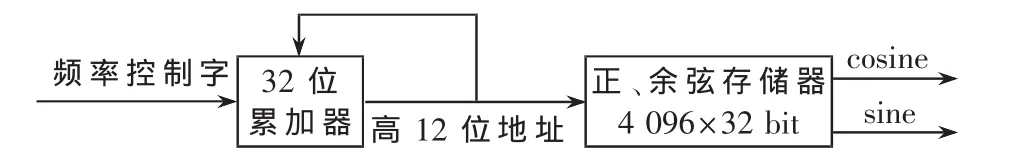

本文设计的NCO包括一个32位的相位累加器,根据输入的频率控制字产生相位累加值。取相位累加值的高12位为地址,将存储在存储器中的数据输出即可得到对应频率的正、余弦信号。DDS模块的输出频率fout是系统工作时钟fclk、相位累加器比特数N(频率寄存器位数)及频率控制字K(步长)三者的一个函数,其数学关系为NCO内部结构框图如图2所示。

图2 NCO结构框图

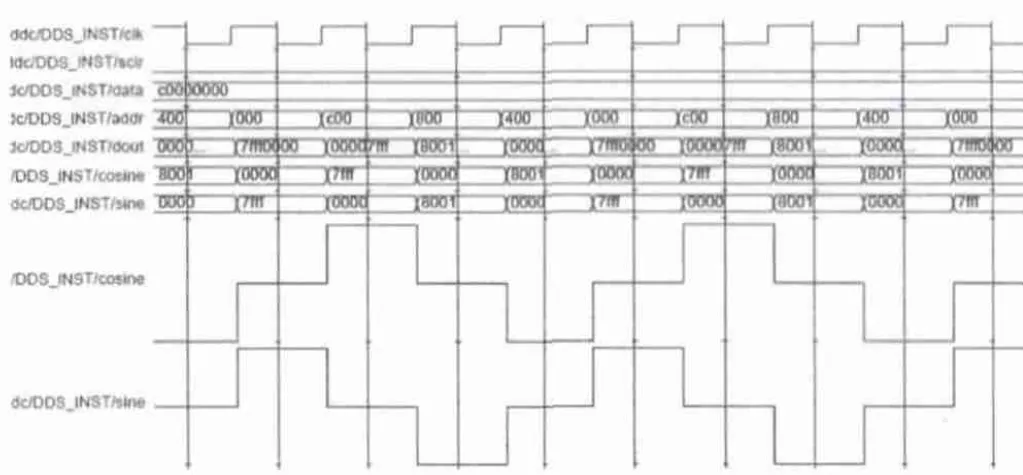

在电路设计中,本地振荡时钟为48 MHz,现需要产生12 MHz正交正、余弦信号,设计中累加寄存器位宽N=32,可计算出频率控制字 K=32′hC0000000。仿真波形图如图3所示。

图3 输出12 MHz中心频率正、余弦仿真波形图

3 乘法器设计

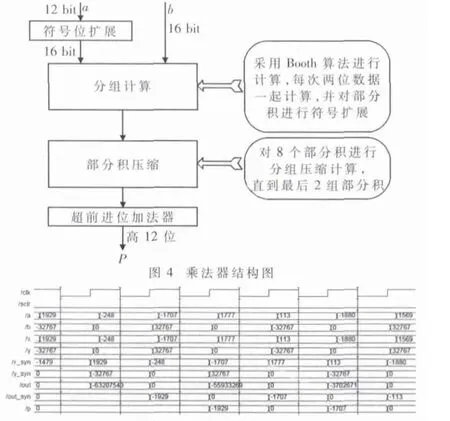

在混频时需要用到两个乘法器,NCO产生的16 bit正、余弦信号分别与外部输入的12 bit信号相乘,产生两路正交信号。电路设计中采用Booth算法设计一个12×16的有符号乘法器。

常用的乘法运算每次都只检查乘数1 bit的二进制数。为了加快运算速度,可以同时检查k bit二进制数,需要利用Booth算法,也称高基算法。Booth算法的提出主要是为了解决有符号数乘法运算中复杂的符号修正问题,所以本设计采用booth2编码,对于补码表示的两数就不需要考虑符号的问题。

16位有符号乘法器可以分为三部分:根据输入的被乘数和乘数产生部分积、部分积压缩产生和与进位、将产生的和与进位相加。这三部分分别对应着编码方式、拓扑结构以及加法器。

乘法器采用全并行设计,输入和输出都是并行的,电路较为复杂,但是速度极快。在电路设计初,首先将12 bit乘数a用符号位补齐成16 bit x,并将两个16位数x、y同步一个时钟周期,送入16×16乘法器设计,在乘法器运算结束后,同步其输出out并取输出结果的高12位作为混频信号p送入FIR滤波器。乘法器结构图如图4所示,仿真波形如图5所示。

图5 乘法器仿真波形图

4 FIR低通滤波器设计

由于AD在中频进行采样,采样速率有可能很高,而混频后得到的数据率与采样速率是一致的,后级的FIR滤波器根本无法达到这个处理速率,因此先通过抽取器进行抽取,使数据率快速降低,再由FIR进行滤波[6]。在此设计的FIR滤波器具体为40阶,采样频率为48 MHz,截止频率为6 MHz,输入信号位宽为12 bit,输出时钟频率为 96 MHz,输出位宽为 16 bit。

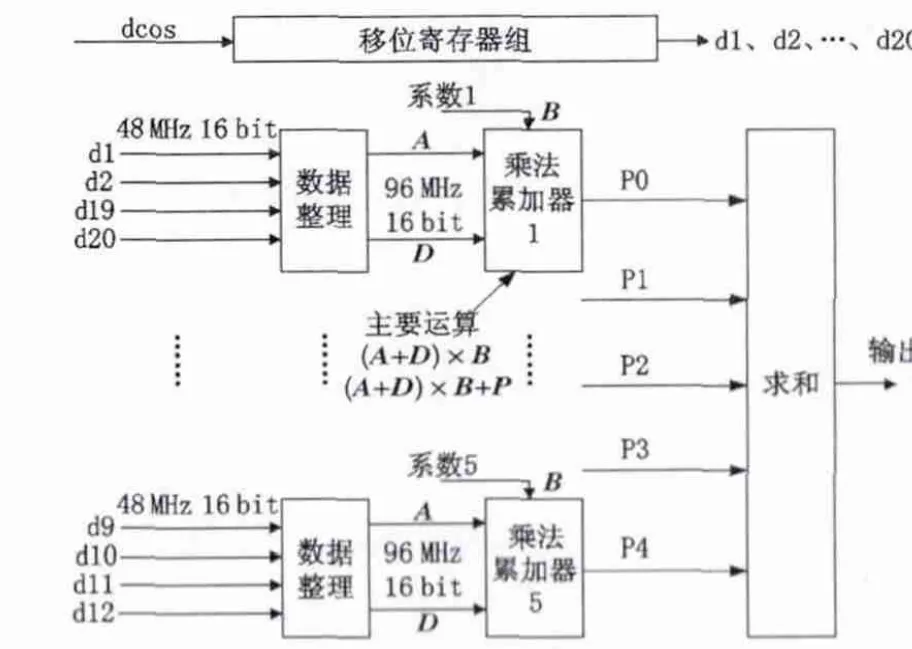

多抽取率低通滤波器内部主要包括20级移位寄存器组、数据整理单元、乘法累加器及求和单元。其中移位寄存器主要进行数据的延时,其功能相当于多个触发器的串联以实现多个周期的延时[7]。当2抽取时,延时2个时钟周期;4抽取时,延时4个时钟周期。数据整理是将两个48 MHz数据率的数据整合为一个96 MHz数据率的数据,使用flag进行区分。乘法累加器主要将数据整理后的对应数据进行预加后乘以系数。当选择信号sel为低电平时将对应数据预加并乘以系数;当sel变为高电平时,将对应数据预加并乘以系数后与上一周期的求和值累加。最后的求和单元主要将5个乘累加运算结果进行相加,并取最终结果的高16位输出,作为I支路和Q支路输出数据。FIR滤波器的结构框图如图6所示。

图6 多抽取率低通滤波器

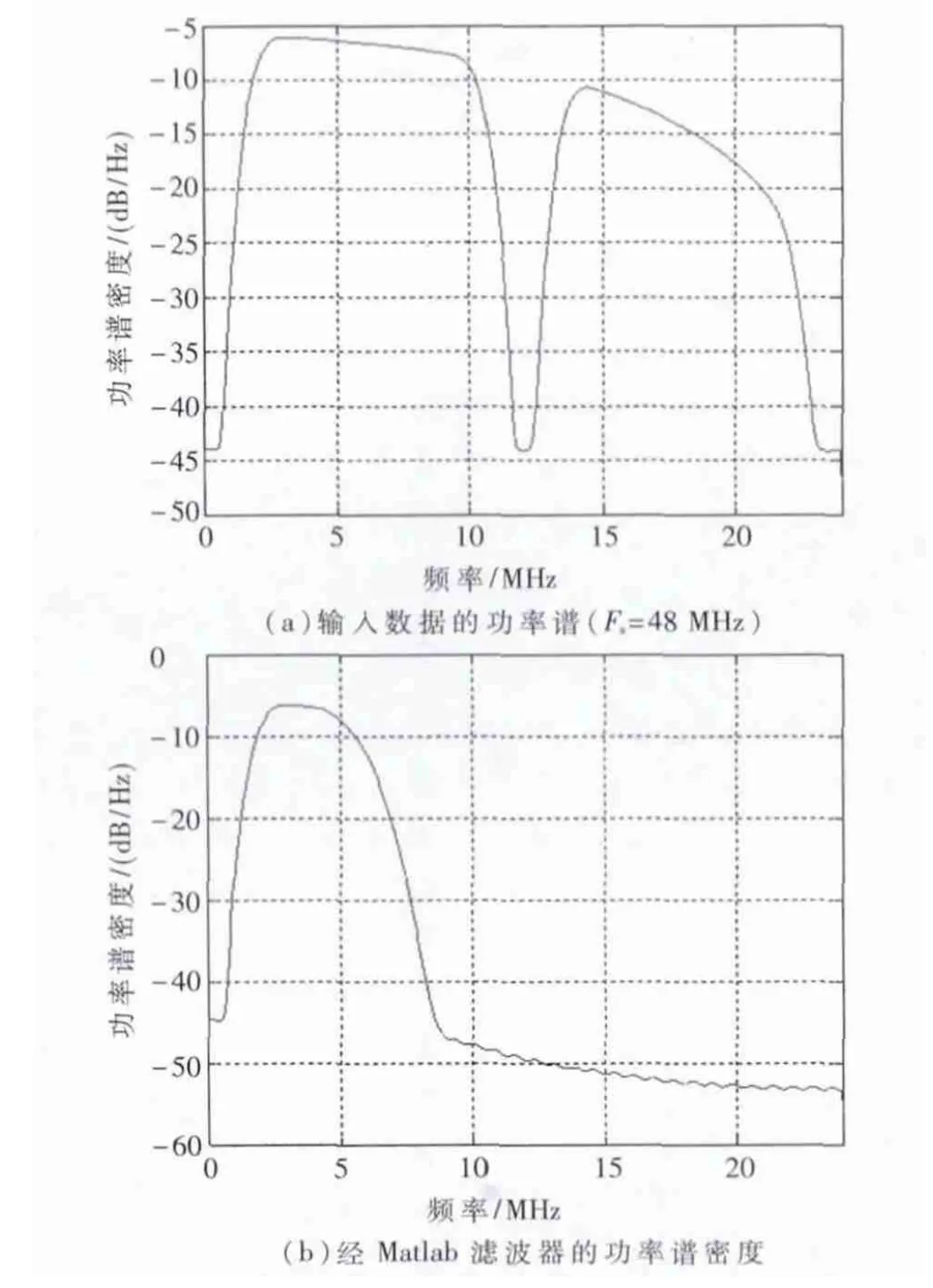

图7 滤波器Matlab设计滤波效果

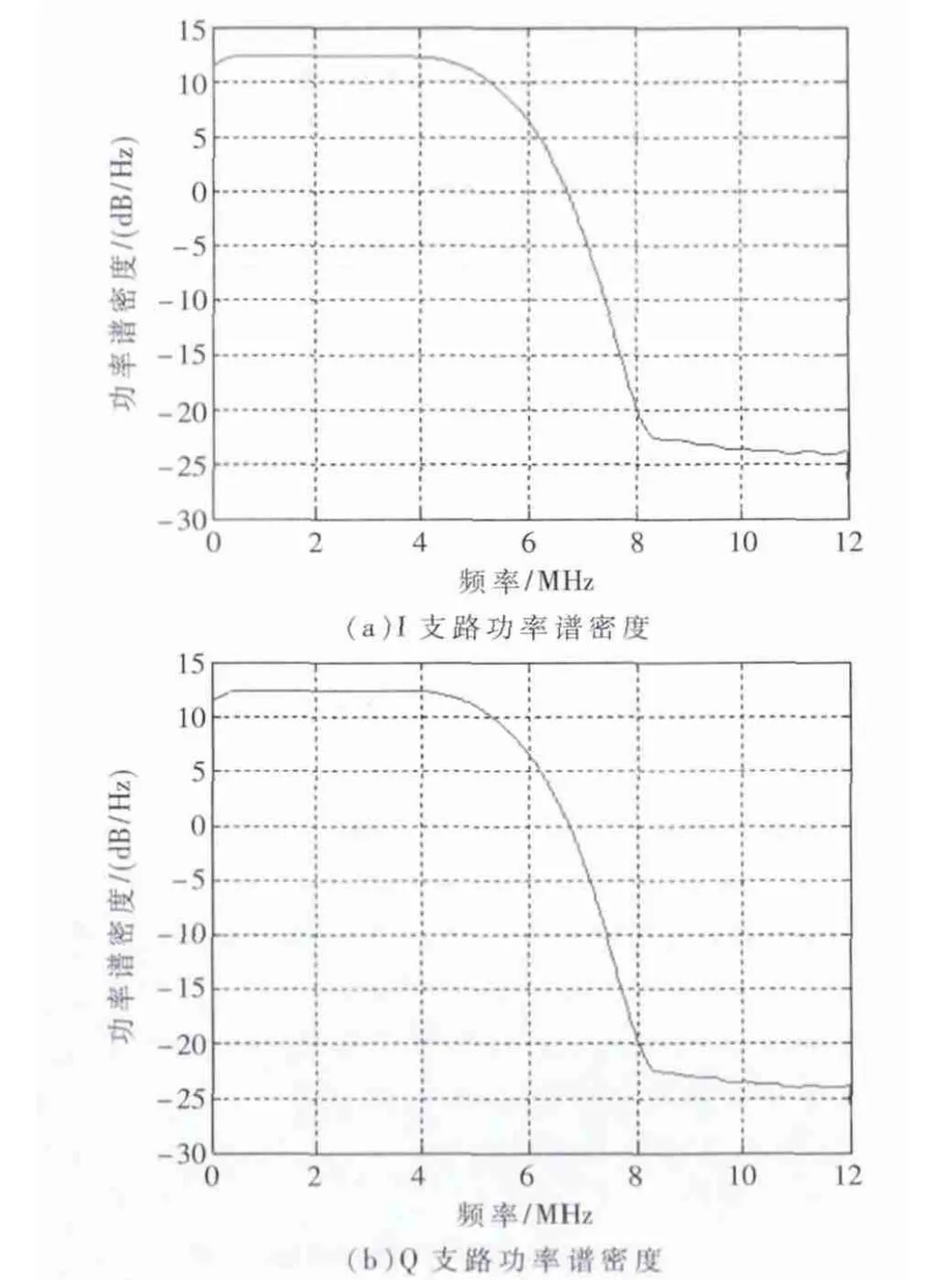

为了验证所设计滤波器的有效性,将仿真所产生的时域数据送入Matlab,给出滤波前后信号的功率谱密度[8],所得结果如图7、图8所示。由图7可以看出,在滤波器截止频率(Fcut=6 MHz)频带范围内,Matlab滤波器与信号功率谱相似;在截止频率以外,对信号形成良好的抑制。由于存在取整、四舍五入等量化误差,所以所设计的滤波器会引入一定的误差,如图8所示。

图8 ASIC设计滤波功率谱(6 dB截止频率Fpass=6 MHz,阻带起始频率 Fstop=8.3 MHz)

5 仿真结果和版图设计

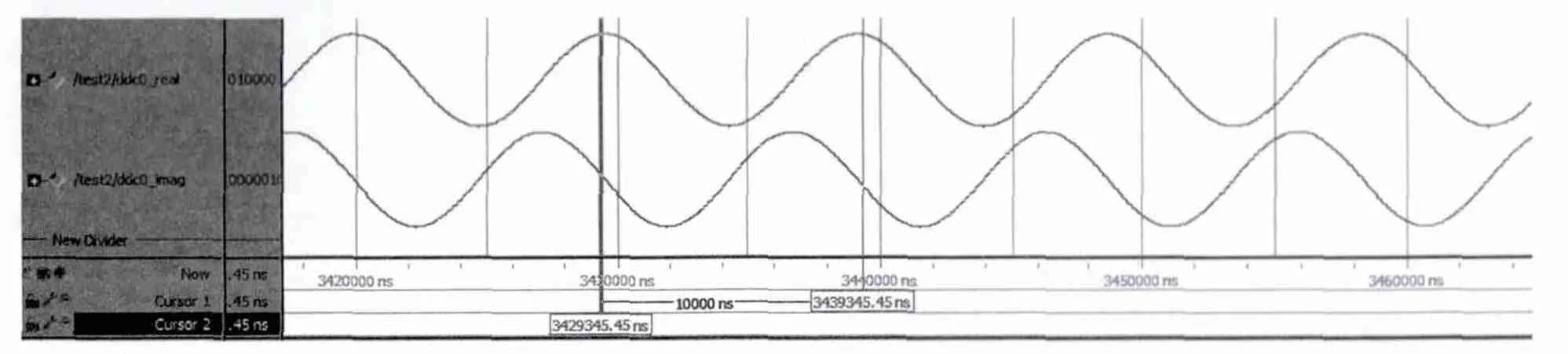

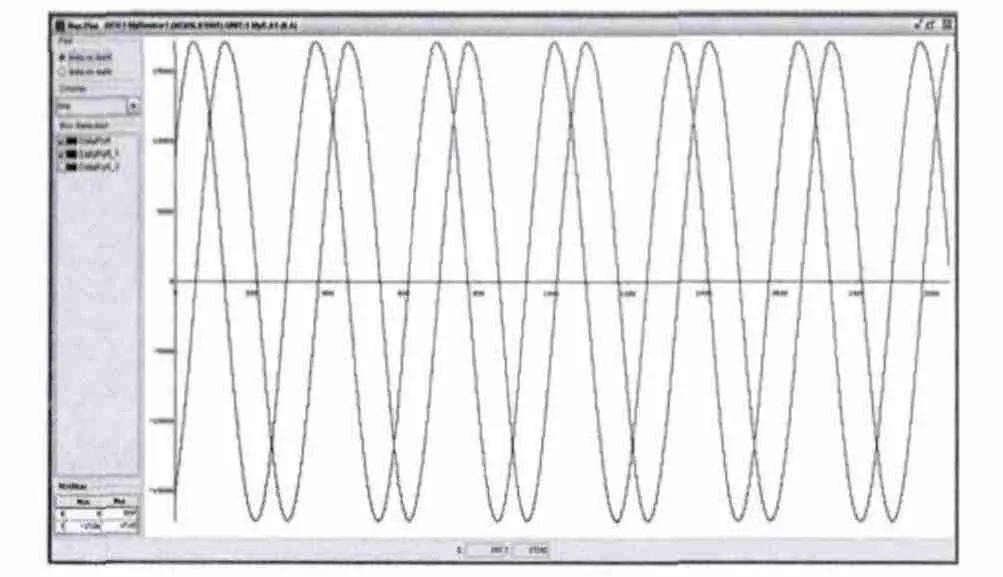

DDC数字下变频电路采用硬件描述语言Verilog实现各个模块的功能后,在testbench中输入一个位宽为12 bit、中心频率为12 MHz的信号,并且将NCO的频率控制字设置为11.9 MHz。在经过混频、抽取、滤波后,最后的I、Q支路应该输出0.1 MHz的正、余弦信号。从图9的仿真结果可见,实部的两个最高点间长度为10 000 ns,正好为0.1 MHz,符合设计要求。

在电路设计完成后,采用Synopsys的DC工具将硬件描述语言综合成门级网表,并交由后端完成版图设计。

图9 整体仿真波形图

6 流片测试结果

在电路流片完成后,对电路进行封装测试,使DDC电路的I、Q支路输出0.1 MHz的信号,将电路的实部、虚部输出信号输入至FPGA,使用96 MHz时钟进行一个节拍延迟,并利用ChipScope软件进行观测,电路测试波形图如图10所示。由图中可知,电路能够正常输出正、余弦信号波形,曲线也比较光滑,DDC数字下变频电路设计成功。

图10 ASIC电路测试波形图

本文主要设计了一个DDC数字下变频ASIC电路,该电路完全采用正向设计流程,0.13 μm工艺设计。从流片结果的测试情况看,电路性能指标满足要求,完全实现了基于不同抽取率的数字下变频功能。该电路能够广泛应用于军事雷达、无线通信等领域,以往只能通过国外电路或者高性能FPGA实现数字下变频。有了该电路,不仅减小了系统体积、降低了成本,而且解决了军用电路国产化的问题。

[1]张光义.相控阵雷达原理[M].北京:国防工业出版社,2009.

[2]王宇峰.数字下变频芯片的前端设计[D].长沙:湖南大学,2010.

[3]刘欣.基于CORDIC的数字下变频电路的ASIC设计与实现[D].成都:电子科技大学,2007.

[4]徐伟,王旭东.基于FPGA的高效灵活性数字正交下变频器设计[J].电子技术应用,2012,38(9):13-15.

[5]丛玉良,王宏志.数字信号处理原理及其MATLAB实现[M].北京:电子工业出版社,2009.

[6]Xu Changqing,Hu Saigui,Li Zhiping.A digital intermediate frequency receiver for inter-vehicle communications[C].In:Pro of the 2007 IEEE Intelligent Vehicles Symposium,Istanbul,2007:840-845.

[7]MALMIRCHEGINI M,HAGHSHENAS H,MARVASTI F.A novel iterative digital down converter[C].Pro.of the 2007 IEEE International Conference on Telecommunications,Penang,2007:442-445.

[8]Luo Feiteng,Chen Weidong.An economical TDM design of multichannel digital down converter[C].Pro.of ICSP2008,Heifei,2008:498-499.