基于VPX6-460的多处理器通信设计*

2013-08-13汪学刚

吴 静,王 洪,汪学刚

(电子科技大学 电子工程学院,四川 成都 611731)

传统的并行总线架构多采用VME标准,但共享总线会造成频繁等待和冲突,大大降低了系统运行效率,不适合大规模并行数据处理系统。随着现代雷达、图像等信号处理应用对信号带宽和数据传输速率要求的不断提升,基于VPX串行总线标准的通用信号处理器占有较大的优势[1-3]。本文首先介绍了基于VPX总线架构的系统设计,着重介绍了信号处理卡VPX6-460的硬件组成,并采用VxWorks实时操作系统实现了多处理器间的高速数据通信。

1 系统整体设计

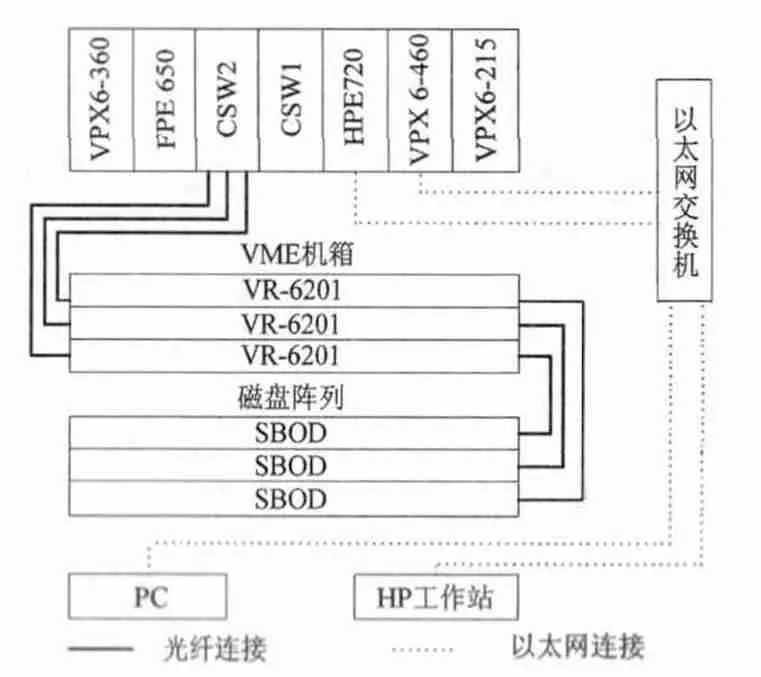

VPX定制机箱采用新型的高速串行总线标准VITA46,相对于VME总线架构而言,具有更大的数据吞吐能力和交换能力、更好的散热性能和更高功率的插槽,充分满足了信号处理系统对带宽和运算处理能力的要求[4-5]。图1所示为系统的基本框图。整个系统主要由多通道信号采集卡、多通道数据回收卡、信号处理卡以及高性能服务器等组成。系统以千兆以太网作为平台间的网络互连标准,并使用串行RapidIO和PCIe作为底板总线交换网络互连协议。VPX载板和模块化的信号采集子卡组成了系统的前端数据采集部分,VPX载板拥有的多个高速串行接口可以将采集到的并行数据转换成串行数据流,传送给后端的信号处理板进行复杂的后端处理[6]。

图1 系统组成结构框图

2 硬件设计

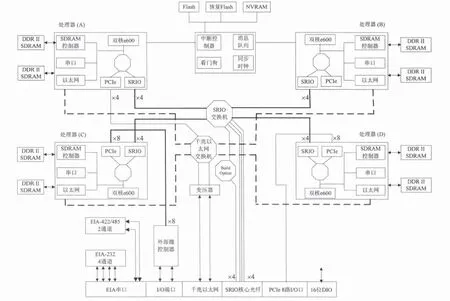

在整个VPX机箱中,嵌入式信号处理卡VPX6-460是一款多CPU并行处理器信号处理卡,其内部组成结构如图2所示。板上载有4块双核PowerPC 8641D处理器,共有8个e600处理器核,每个处理器配有512 MB的同步动态随机存储器DDR2SDRAM,还配有512 MB具有写保护的Flash和NVRAM。板上的千兆以太网交换机用来配置每个处理器的状态;4个处理器间通过串行RapidIO交换器实现串行数据互连,每个处理器的数据输入/输出速率都可达到双向12 Gb/s,同时有4路串行RapidIO连接到背板,可连接4个处理板,支持16个处理器间的全速数据交换;板上的XMC/PMC插座支持8路PCIe连接,可用于扩张外部的输入/输出接口。

3 软件设计

信号处理器的硬件部分构成了系统框架和硬件平台,而软件部分则用于实现各种功能,是整个系统的“灵魂”。VPX6-460是典型的“通用处理器平台+嵌入式操作系统”结构,选用的操作系统是美国Wind River公司最新研发的VxWorks6.8,主机上的开发环境是基于Eclipse软件架构设计的Workbench3.1,通过串口和网络接口实现主机与目标机间的交叉编译和交叉调试。VxWorks实时操作系统提供了专门的系统调用函数接口来连接中断向量和中断服务程序,内核可以自动提供有关中断处理中所需要的堆栈切换以及寄存器保护、回复等功能。VxWorks6.8提供的内部处理器通信IPC(Inter Processor Communication)函数库 Rel2.4.7支持多处理器间的通信,适用于底层串行RapidIO和以太网的链接,提供与连接无关的编程接口,从而简化了多处理器通信的程序设计,提高了程序的可移植性。

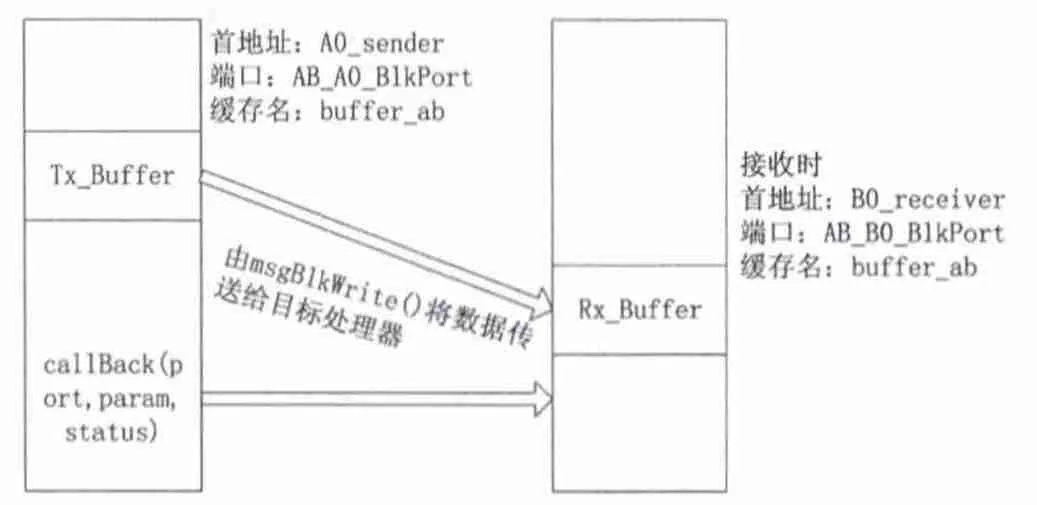

VPX6-460的各个处理器之间主要采用直接内存访问 DMA(Direct Memory Access)通信机制,可以同时传输批量数据。当DMA控制器接收到来自输入/输出口的DMA请求时,CPU就会转让总线控制权给DMA控制器,在完成数据传输后,DMA控制器会归还总线控制权。整个传输过程由DMA控制器负责而不需要CPU的参与,有效地减少了CPU的占用时间,大大提高了系统性能[7-8]。图3所示为VPX6-460上两个处理器间通信的基本原理框图。

图2 多CPU信号处理卡VPX6-460内部组成结构

图3 多处理器间通信的基本原理框图

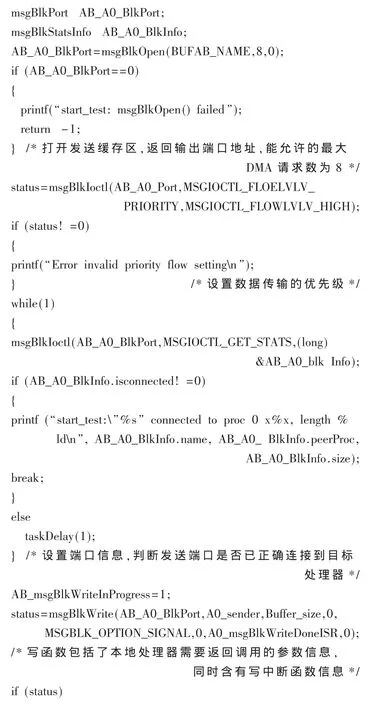

在本地处理器上创建由指针A0_sender指向的缓存区buffer_ab,相应的发送端口为 AB_A0_BlkPort,由函数msgBlkWrite()将成片数据写入到目标处理器上,由目标处理器的新建缓存区存储接收数据,接收端口为AB_B0_BlkPort,缓存区名也为 buffer_ab,使用相同缓存名可以实现数据共享。由于DMA写操作是异步实现的,即无论DMA请求是否已被执行,msgBlkWrite()都会立即返回,因此本地处理器需要调用函数callBack()返回写操作的完成时间和状态等信息。同时,在完成数据传输时,DMA控制器要释放总线控制权,通过发送端口的写中断服务程序告知本地处理器已完成数据传输,接收端口以读中断服务程序告知目标处理器已完成数据接收。部分程序如下:

本文在介绍了VPX6-460硬件组成的基础上,结合VxWorks操作系统的特点以及系统所支持的通信机制,详细分析了不同处理器间的数据传输方式,并给出了具体的软件实现方法。该程序的高度可移植性使其具有很高的应用价值。

[1]杜文凤,王博文.基于嵌入式的实时通信协议栈研究与设计[J].电子技术应用,2013,(39)1:29-31.

[2]刘昊昱.一种基于VxWorks技术的通用信号处理平台设计[J].电子技术应用,2003,(29)6:13-15.

[3]宋秀兰,吴晓波.多处理器通信设计[J].浙江工业大学学报,2010,38(4):426-429.

[4]廖明燕.基于 MSP430的多处理器通用技术研究[J].微处理机,2006,2(1):86-91.

[5]何先波,李薇.嵌入式系统软件开发技术基础[M].北京:清华大学出版社,2011.

[6]史鸿声.基于 PowerPC的雷达通用处理器设计[J].雷达科学与技术,2011,9(2):140-144.

[7]李世光,孟强强.基于多串口的热量表系数修正软件的设计[J].微型机与应用,2012,31(18):1-4.

[8]翁省辉,喻武龙.Liunx下SANE Driver自动化测试工具的设计与实现[J].微型机与应用,2012,31(1):4-6.