基于交叉双平面技术的图像采集存储系统

2013-08-13刘文怡王金陵

魏 敏,刘文怡,王金陵

(中北大学a.电子测试技术国家重点实验室;b.仪器科学与动态测试教育部重点实验室,山西 太原 030051)

责任编辑:薛 京

在飞速发展的信息时代,人们对高速信息的需求日益增强,在卫星通信、雷达通信、信号测量等领域,信息的采集、存储与分析一直都是人们面临的重要课题[1]。然而,由于图像数据传输速度快、信息量大,对采集存储技术提出了更高的要求[2],因此,需要设计出一种具有采集与存储速度快、容量大、体积小、抗干扰能力强、可靠性高的图像数据采集存储系统。常用的页编程和双平面页编程技术已经无法满足要求,而利用平均速度为22.8 Mbyte/s的交叉双平面页编程技术[3],为高速、大容量图像数据的采集、存储提供了全新的设计方案。

1 总体方案设计

1.1 系统组成

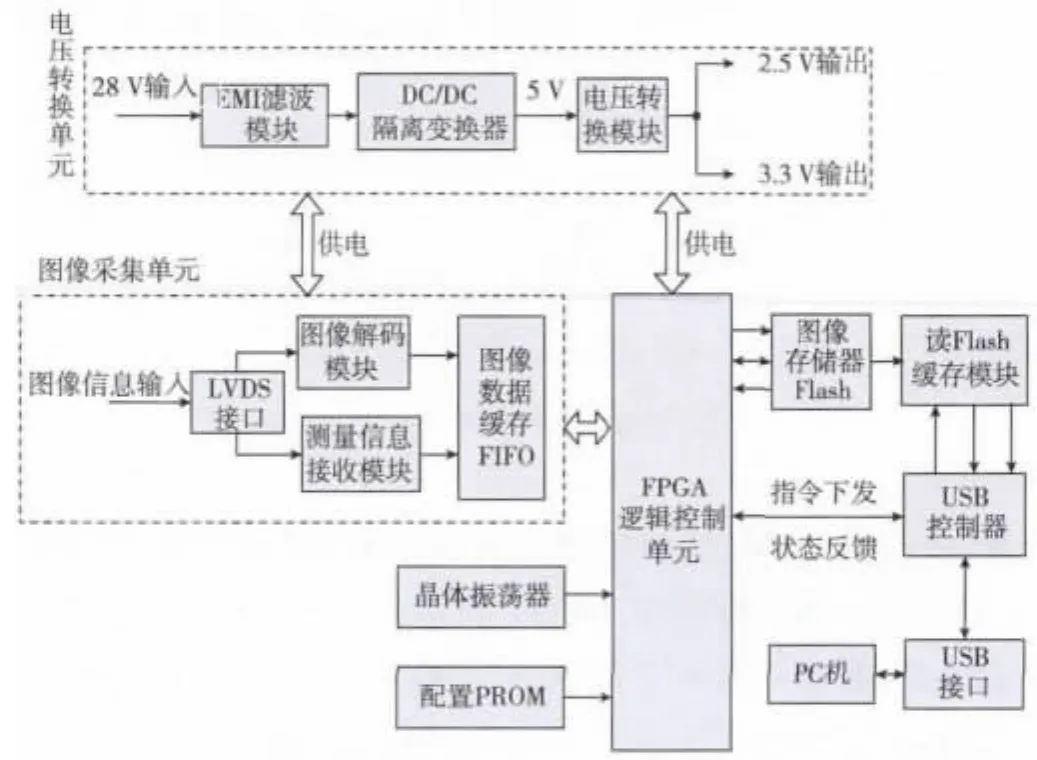

本文介绍的采集存储系统主要是为了完成对图像信息的采集、编码及存储。系统采用模块化设计的思路,各个模块既相互独立又相互配合构成了整个系统。本系统主要由电源转化单元、图像采集单元、FPGA逻辑控制单元、图像存储单元和USB接口单元组成。其中图像采集单元选用LVDS接口作为数据输入接口,满足图像信息高速传输的要求。FPGA逻辑控制单元采用Xilinx公司生产的Spartan-3系列中的XC3S400芯片作为逻辑控制芯片,实现系统对硬件电路高集成度的要求。图像存储单元则选用三星公司容量为4 Gbyte的NAND型Flash芯片K9WBG08U1M,并利用交叉双平面页编程技术对Flash进行写操作。而USB接口单元采用Cypress公司EZ-USB FX2系列CY7C68013-128AXC,该芯片采用GPIF数据传输方式提高读数效率。系统总体框图如图1所示。

图1 系统总体框图

1.2 系统原理

本系统接收的图像信息包括两种,一种为图像数据,另一种为测量数据。两种数据由LVDS接口接入并分别通过FPGA控制的图像解码模块和测量信息接收模块对其采集、解码。由于测量数据传输速度快,在数据存储之前,将数据通过FGPA内部的FIFO进行缓存。当FPGA中的Flash写控制信号监测到内部FIFO半满信号和图像数据接收完成信号,则将两种数据按照交叉双平面页编程技术写入到图像存储器Flash中,最后数据通过USB接口发送至计算机显示。在此过程中,系统命令的下发均通过计算机中的上位机完成。同时,FPGA芯片及其他芯片所需的3.3 V和2.5 V电压均由电压转化模块提供。

2 系统硬件电路设计

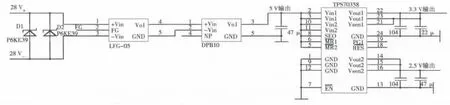

2.1 电压转化单元设计

电压转化单元主要包括EMI滤波模块、电源模块、电压转换模块3个部分。28 V输入电压通过EMI滤波模块及DC/DC隔离变换器产生5 V电压,再由电压转换芯片TPS70358将5 V电压转化为所需的3.3 V和2.5 V。选用的电压转化芯片TPS70358是一种具有双端口电压输出、低噪声的线性稳压器[4],其硬件电路图如图2所示。

图2 电压转换模块硬件电路图

EMI滤波模块对系统输入的28 V电压进行EMI滤波处理,这不但能够抑制系统自身产生的EMI噪声,同时可以为FPGA及其他系统芯片提供无衰减的直流输入电压,滤除由电网进来的各种干扰信号,使设备不受EMI噪声干扰[4]。

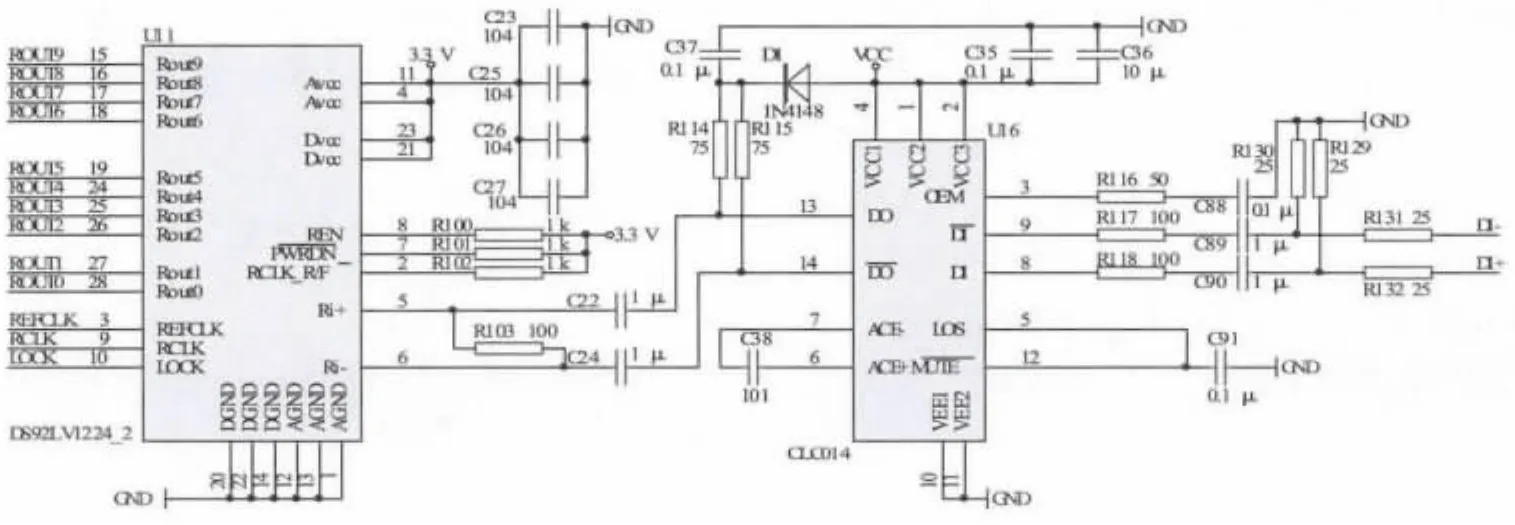

2.2 图像信息采集设计

本系统的图像数据和80包的测量信息均经过LVDS接口接收,LVDS接口芯片采用10位低压差分信号解串器DS92LV1224,它能将接收到的LVDS差分数据流转换为10位的并行数据,同时又可以重建并行时钟(RCLK)[5]。LVDS传输模式接收电路设计如图3所示。

图3 LVDS接收电路

由于经LVDS接口接收的两种数据传输码率不一样,图像数据的像素时钟为15 MHz,测量数据发送的波特率为115 200 bit/s,FPGA逻辑控制单元无法直接对这两种数据进行混合编帧,这时需要将两种数据先存进FPGA内部FIFO进行缓存,经时序匹配后,将信息存入FPGA内部建立的写Flash缓冲器中,当FPGA中的Flash控制模块监测到写Flash缓冲器半满信号时,则开始将信息存入Flash。

3 系统时序设计

3.1 图像信息采集

图像信息由LVDS接口接入,经解串器DS92LV1224解码后转化为4路图像数据信号,1路帧同步信号、1路行同步信号、1路像素时钟和1路测量数据。

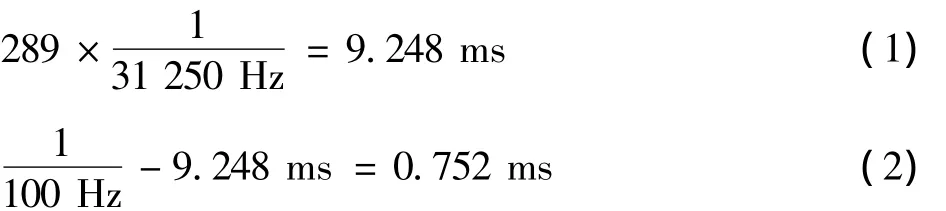

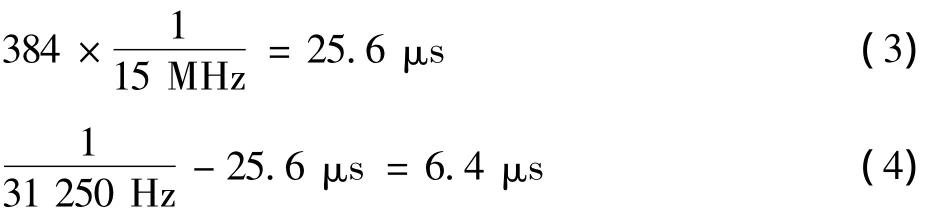

对于图像数据而言,帧同步信号的频率为100 Hz,高电平有效,每一帧有289行有效数据,行同步信号的频率为31 250 Hz,高电平有效,每一行有384个有效像素,像素时钟为15 MHz,上升沿时数据发生改变。帧同步信号高低电平时间、行同步信号高低电平时间计算为其中,式(1)为帧同步信号高电平时间;式(2)为帧同步信号低电平时间;式(3)为行同步信号高电平时间;式(4)为行同步信号低电平时间。接口信号时序如图4所示。

图4 接口信号时序图

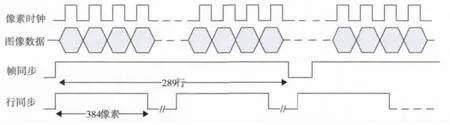

对于测量数据而言,每接收一帧图像数据就串行接收80包的测量数据,其中每一包测量数据包含10位,串行传输的码率为1 152 000 bit/s,因此接收80包数据所需时间为

由此可知,接收80包测量数据是可以在图像数据帧同步信号高电平时间内完成的。在FPGA内部构建一个256×8 bit的片内异步FIFO,设写FIFO时钟为29.5 MHz,因此80包测量数据写FIFO的时间经计算为

则可在图像数据的帧同步信号高电平接收80包数据,低电平将测量数据写入FIFO。当一帧图像数据接收完成后,将80包测量数据和一帧图像数据进行混合编帧后,传输至Flash存储单元。

3.2 图像信息存储

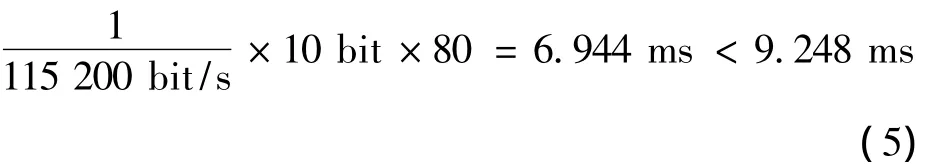

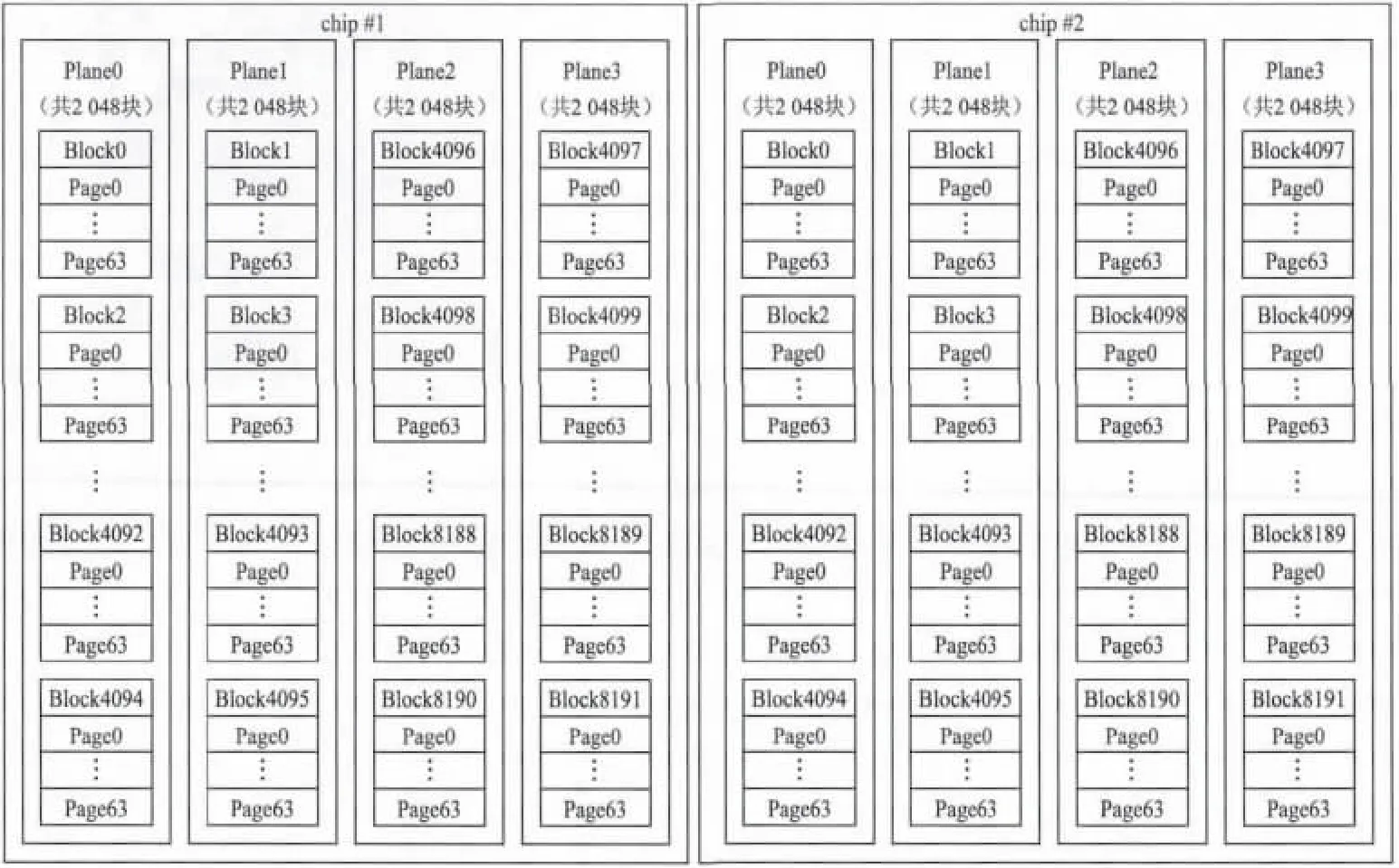

由于图像传输速度快,因此选用交叉双平面页编程方式,选用的Flash芯片K9WBG08U1M的内部平面结构图如图5所示。

图5 K9WBG08U1M内部平面结构图

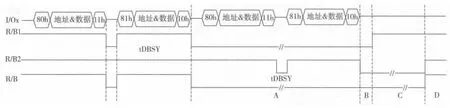

定义chip#1的plane0和plane1为第0组、plane2和plane3为第1组,chip#2的 plane0和plane1为第2组、plane2和plane3为第3组。当对第0组进行操作时,也可对其他3组分别执行写命令操作、写地址操作和写数据操作。交叉双平面页编程时序如图6所示。

图6 交叉双平面页编程时序(截图)

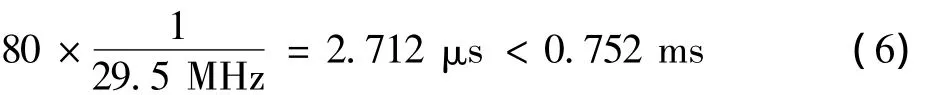

在VHDL程序中定义信号choose(2:0)对8个plane进行控制。choose(0)为0表示选择平面组中的偶平面,为1表示选择平面组中的奇平面;choose(1)为0表示操作第0组和第2组,即Flash的前4 096块,为1时表示操作第1组和第3组,即Flash的后4 096块;choose(2)为0操作chip#1,为1操作chip#2。将2片Flash的R/B1和R/B2信号进行相与,得到判断整个Flash的工作信号。该信号可以表示交叉双平面技术写Flash的4种状态,如图6所示,其中A状态表示对第1片进行页编程,同时第2片Flash已准备好;B状态表示两片Flash都在页编程;C状态表示第1片Flash已完成页编程,第2片Flash正在执行页编程;D状态表示两片Flash均完成页编程,并均做好下一轮页编程准备。

4 测试结果

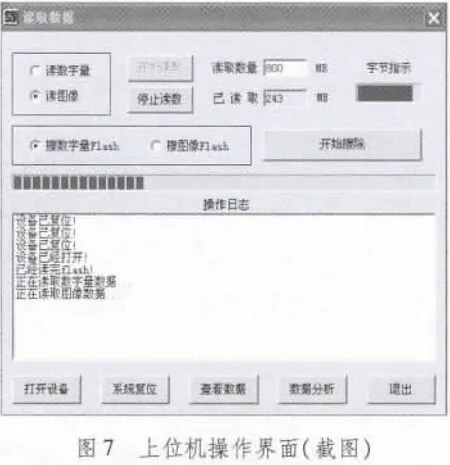

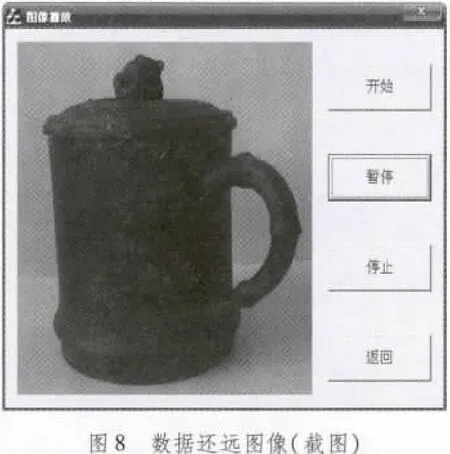

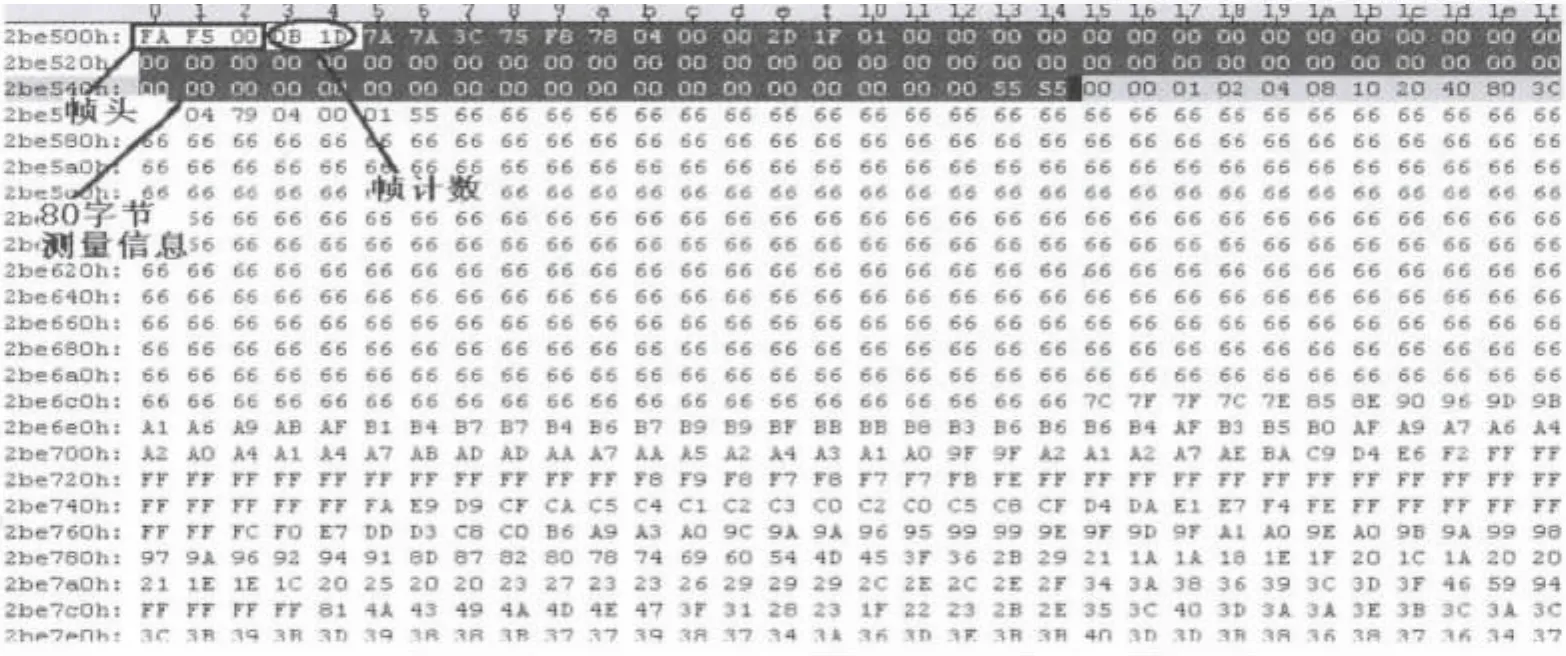

本设计以采集存储系统为主体,配合地面测试台以及上位机软件完成闭环自检试验[6]。系统上电后,地面测试台对系统发送特定帧结构的图像数据和80包的测量信息。图像数据每帧为289×384 byte,记录时间要求大于300 s,传输帧率为100 f/s(帧/s),因此图像存储器的容量为:(289×384 byte)×(300 s÷10 ms)≈3.1 Gbyte。利用交叉双平面页编程技术有效提高Flash的存储速度,经多次反复测试,本系统Flash的写入速度达到30 Mbyte/s。上位机软件操作界面如图7所示,上位机软件对第2 845帧图像数据还原的图像如图8所示。测试设备发送的原始数据如图9所示。

图9 图像原始数据(截图)

5 结论

基于交叉双平面技术的图像采集存储系统实现了对高速、大容量图像数据的采集、存储功能。该系统针对图像信号传输的高速、大容量数据特征,设计了电源转化单元、图像采集单元、FPGA逻辑控制单元、图像存储单元和USB接口单元,可以将图像信号实时采集接收并完整准确送入Flash进行存储,并在之后将存储数据回读至计算机还原图像。该设计充分利用了交叉双平面页编程技术,为图像信息的采集存储提供了一种全新的实现手段。

[1]刘蕴才.无线电遥测遥控[M].北京:国防工业出版社,2001:7-8.

[2]杨立宏.基于Flash的红外相机数据高速存储[D].长春:长春理工大学,2009.

[3]朱岩.基于闪存的星载高速大容量存储技术的研究[D].北京:中国科学院研究生院,2006.

[4]韦斯顿.电磁兼容原理及应用[M].杨自佑,王守三,译.2版.北京:机械工业出版社,2006:601-660.

[5]张健,吴晓冰.LVDS技术原理和设计简介[J].电子技术应用,2000(5):59-61.

[6]郭铮,刘文怡,冯妮.基于FPGA多通道高速数据采集存储器设计[J].电视技术,2012,36(17):55-57.