基于FPGA视频处理的低温设计缺陷分析与排除

2013-08-13郑辛星张肖强

郑辛星,张肖强,杨 静

(1.芜湖职业技术学院自动化控制系,江苏 芜湖 241003;2.南京航空航天大学电子信息工程学院,江苏 南京 210016)

责任编辑:魏雨博

在电子设备产品设计过程中,由于参与设计的人员经验不足,研制周期较短,产品的细节设计往往有不尽如人意之处,这些看似无关紧要的细节设计缺陷,直接影响着产品正常使用。本文分析了一起由于电路细节设计缺陷原因,而引起工业级显示器在低温下图像上下抖动的故障,并根据分析提出了解决方案,经随后的低温试验证明,提出的解决方案可以有效解决图像上下抖动故障。

1 低温抖动故障

新研制某型号工业级显示器进行小批量试产时,有若干台显示器在低温试验中偶尔出现图像上下抖动故障的现象。随着低温试验时间加长,图像上下抖动故障现象出现的频率更高,现象更明显。图像上下抖动故障现象造成的根本原因是场同步信号的衰减、丢失、受到干扰、频率不稳定、同步信号失真等原因[1]。

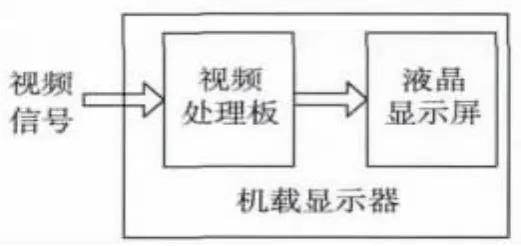

对于本显示器视频信号通道如图1所示,视频信号进入显示器后,先进入视频处理板进行视频格式转换,然后送入液晶显示屏进行显示。将有故障显示器的视频处理板更换到无故障显示器中后,在低温试验中出现图像上下抖动故障,将无故障显示器的视频处理板更换到有故障显示器中后,低温试验中无故障出现,因此可以将故障的原因定位到视频处理板上。

图1 显示器视频信号通道示意图

2 视频处理板

在工业视频显示系统中,由于工业视频格式的特殊性和工业显示器结构尺寸的限制等原因,视频信号源产生的图像分辨率与选用的液晶显示屏分辨率不相同。视频处理板的主要作用是,将视频信号源的图像分辨率转换成液晶屏分辨率。

目前的视频处理系统主要有基于专用芯片、基于DSP和基于FPGA三种方式[2]。基于FPGA的方式具有开发周期短、设计灵活、外围电路简单、成本低、电路面积小等优点,被广泛应用到视频处理系统中[3]。因此,本项目采用Xilinx Spartan-3系列FPGA作为视频处理板的主处理器。

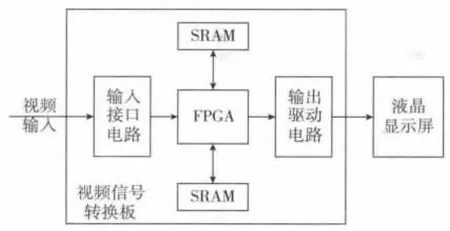

视频处理板的工作原理框图如图2所示。视频输入信号从输入接口电路输入,然后送入FPGA进行视频分辨率转换,转换后由输出驱动电路发送给液晶显示屏。

图2 视频处理板工作原理框图

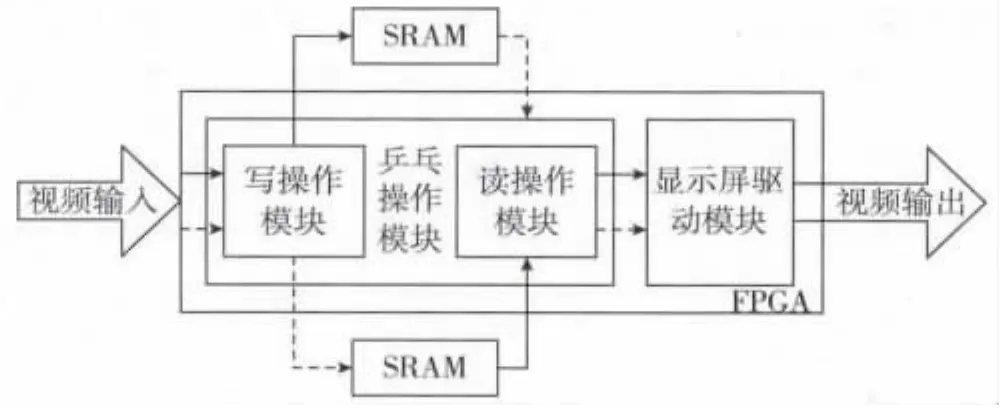

FPGA内部的逻辑电路原理框图如图3所示,视频信号源进入FPGA后,由FPGA内的乒乓操作模块根据视频信号源同步信号时序写入数据缓存SRAM中。图中的虚线和实线分别表示奇场和偶场信号操作流程。显示屏驱动模块首先将视频图像按照液晶显示屏分辨率进行缩放,然后生成液晶屏正常显示所需要的场同步信号、行同步信号和数据使能信号,并根据这些信号时序将缩放后的图像数据送入液晶屏进行显示。

图3 FPGA内部逻辑电路原理框图

3 故障原因分析

首先,用示波器对视频处理板上各个测试点的场同步信号进行检测,观测到场同步信号波形在低温下与常温下基本一致,未发现有异常现象。

然后,对FPGA内部电路设计进行分析。通过分析发现,显示屏驱动模块存在两处设计缺陷:1)未使用视频信号源的DEN(数据使能信号)进行判断是否输入有效图像数据,而是主观认定有效图像数据出现在VSY(场同步信号)上升沿之后的第3个HSY(行同步信号)周期内;2)使用视频信号源的HSY作为检测视频信号源的VSY后肩宽度(注:场同步信号的后肩宽度定义为场同步信号上升沿到出现有效图像数据的距离,通常用行周期个数表示)的检测时钟信号,这不符合FPGA同步电路设计思想,可能产生信号误判现象[4]。这两个不当之处有可能是造成显示器在低温下图像抖动的主要原因。

如图4所示,VSY的后肩宽度为2个HSY周期,即DEN高电平开始出现在VSY上升沿之后的第3个HSY周期内,DEN高电平表明此时视频数据总线上发送的数据为有效图像数据。在原FPGA设计中,使用HSY作为检测VSY后肩宽度的时钟信号。当VSY上升沿发生后,使用HSY上升沿连续3次检测到VSY为高电平,则认为视频数据总线开始传送有效图像数据。

图4 视频控制信号时序图

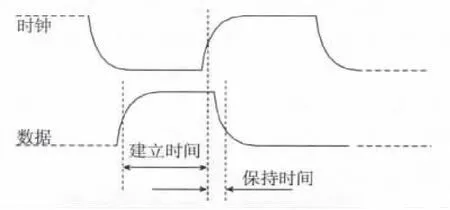

由数字电路基础知识可以得知,时钟在检测信号时需要一定的建立时间和保持时间[5]。建立时间和保持时间如图5所示。根据FPGA数据手册[6]可以得知,所使用的FPGA需要建立时间和保持时间分别在2 ns和1 ns之内。

图5 建立时间和保持时间

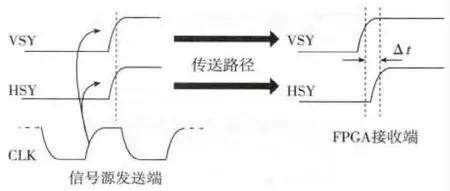

如果在视频信号源中VSY和HSY是由一个系统时钟产生,如图6所示,在产生时,VSY的上升沿和HSY的上升沿几乎是同一时刻的。在常温工作时,由于VSY和HSY传送路径不同,因此信号延迟时间有差异,两者到达FPGA输入管脚时上升沿相差了Δt,Δt正好大于等于HSY检测VSY所需要的建立时间,因此在VSY上升沿后,第一个HSY周期的上升沿检测到VSY的状态为高电平,即在VSY后肩时期内,HSY可以连续3次检测到VSY为高电平,FPGA可以正确接收有效图像数据。

图6 VSY上升沿和HSY上升沿关系的变化

当工业显示器处于低温环境中,由于元器件的工作参数随着温度的变化,VSY和HSY传输路径上的信号延迟时间也发生了相应的变化,特别是传输路径上的关键器件多数为CMOS器件,由文献[7]可知CMOS器件的信号延迟时间将随着温度的降低而减少。因为VSY和HSY传输路径不同,因此两者信号延迟时间受到温度影响不同,使得FPGA输入端两者上升沿之间的时间差Δt小于所需要的建立时间。

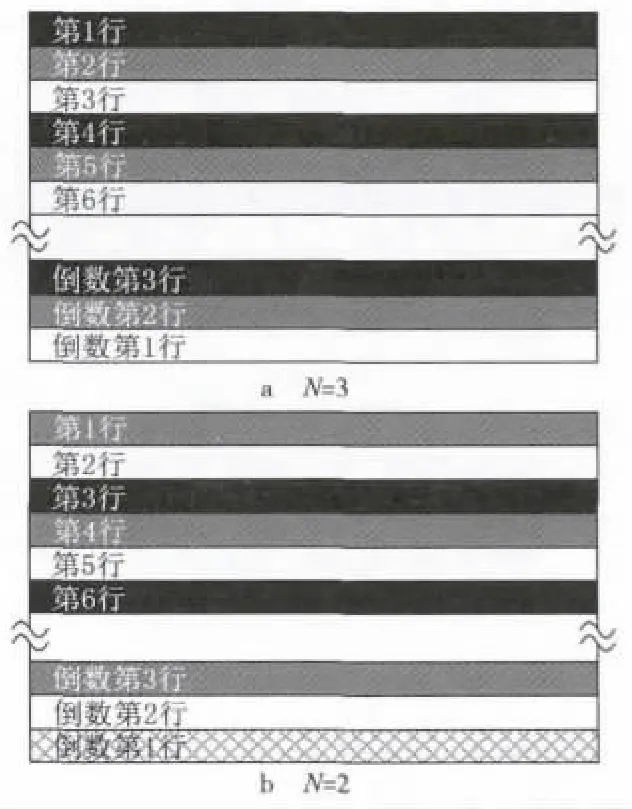

当被检测信号的稳定时间小于所需要的建立时间时,检测电路检测到的被检测信号状态为不定状态,即检测电路输出可能为高电平状态,也可能为低电平状态,或处于高低电平之间的中间状态[5]。因此,当图6中所示的VSY上升沿和HSY上升沿之间的时间差Δt小于FPGA所需要的建立时间时,用HSY检测VSY后肩宽度得到的高电平个数N将是一个不定值,即N有可能为2,有可能为3。但在FPGA原程序中,在VSY上升沿之后,HSY连续3次检测到VSY为高电平时,才开始接收有效图像数据,这样在N=2的情况下,接收到的有效图像数据丢失了一行。

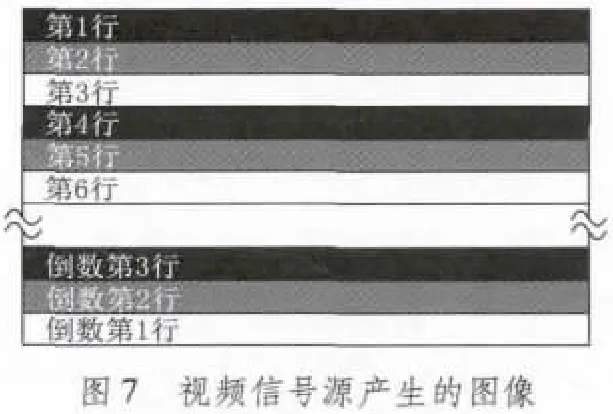

假设视频信号源产生的图像如图7所示,液晶显示屏显示图像如图8所示。图8a为N=3时液晶显示屏显示的图像,图8b为N=2时液晶显示屏显示的图像。由此可以看出图8b是从图7输入图像的第二行开始显示,因此,在低温试验中,显示器的显示画面会偶尔出现上下跳动现象。其中,图8b的最后一行显示图像的颜色取决于视频信号源产生的无效图像数据的数值。

图8 N=3和N=2时显示的图像

由于元器件的个体差异,受到低温影响不同,在无故障显示器中,VSY上升沿和HSY上升沿之间的时间差Δt在低温下仍能够保持大于等于需要的建立时间。

4 解决方案

针对以上分析,对FPGA原程序做以下修改:

1)程序严格按照FPGA同步电路设计思想,将整个FPGA内的电路系统划分为两部分:图像输入电路部分和显示驱动电路部分,每一部分分别使用一个系统时钟,图像输入电路采用信号源送来的信号源时钟作为系统时钟,显示驱动电路采用本地晶振时钟作为系统时钟。所有时钟触发信号都必须以本系统的系统时钟信号为触发信号,两个时钟域之间的数据交换采用SRAM乒乓操作方式进行数据交换。

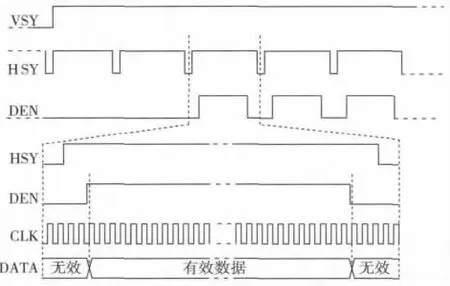

2)在图像数据输入电路中,采用系统时钟检测视频信号源的DEN状态来判断图像数据是否有效。如图9所示,当系统时钟CLK检测到DEN为高电平时,则认为视频总线上的图像数据DATA为有效图像数据,电路开始接收图像数据,并将图像数据存储到SRAM中。当CLK检测到DEN为低电平时,则认为视频总线上的图像数据DATA为无效图像数据。

图9 采用系统时钟CLK检测DEN状态示意图

根据以上两个方面对FPGA程序进行修改,并将修改后的FPGA程序重新综合与布局布线,生成FPGA比特流文件。将新的FPGA比特流文件下载到有故障的视频处理板中,将视频处理板装入显示器后在放入低温试验箱进行低温实验。在实验中,所有显示器都没有再出现过图像上下抖动故障的现象。因此,试验表明本文对此次出现的图像上下抖动故障现象的分析是正确的。

5 结论

通过本文分析,表明本次故障的主要原因在于FPGA程序中对场同步处理不当引起的,即在低温下使用信号源的行同步信号作为检测时钟来检测信号源的场同步信号,得到相邻两场的场同步信号后肩宽度不一定相同,两者之间可能相差一个行同步周期时间,即引言中所述的同步信号失真的情况。同时,表明了同步电路设计思想在FPGA程序设计中的重要性。

[1]储霞.电视发射机图像抖动故障分析[J].电视技术,2001,25(3):26.

[2]宋海吒,唐立军,谢新辉.基于FPGA和OV7620的图像采集及VGA显示[J].电视技术,2011,35(5):45-47.

[3]向厚振,张志杰,王鹏.基于FPGA视频和图像处理系统的FIFO缓存技术[J].电视技术,2012,36(9):41-43.

[4]李向涛,仵国锋.FPGA 同步设计技术[J].无线通信技术,2003,12(3):58-61.

[5]汤山俊夫.数字电路设计[M].关静,胡圣尧,译.北京:科学出版社,2006.

[6]Spartan-3 FPGA Family:Complete Data Sheet[EB/OL].[2012-10-30].http://www.xilinx.com/bvdocs/publications/DS099.pdf.

[7]周鹏,冯一军.CMOS电路低温特性及其仿真[J].低温物理学报,2005,27(4):331-336.