MPC8379E与DDR2之间的PCB布线及仿真设计

2013-07-13程增艳

程增艳,吴 骏

(中船重工七二二研究所 湖北 武汉 430079)

MPC8379E是Freescale公司开发的PowerQUICC II Pro系列的高性能处理器。其内部工作频率最高可达1.33 GHz,在该工作频率上处理性能可达3065 MIPS。一级Cache分为数据Cache和指令Cache各32 kB,二级Cache最大可配置为512 kB。支持DDR1和DDR2,最高支持533 MHz传输速率的DDR2 SDRAM,同时该处理器还支持PCI、PCI-X、PCIE、SRapid IO和4个GbE接口[1]。

内存是计算机系统中至关重要的部分,处理器的每一步操作和操作系统的运行都需要依赖内存,如果内存不能正常访问整个系统就不可能运行。DDR2技术自从面世至今,凭借其出色的性能广泛运用于各种计算机主板和嵌入式设备。本文阐述了MPC8379E与DDR2之间的PCB布线及仿真设计。

1 DDR2设计原理

一个DDR2系统包含控制器和存储器两部分。从时序上分析DDR2系统是一个源同步时序。所谓源同步时序,就是选通信号(即时钟信号)不是通过独立的时钟源发送,而是由驱动芯片发送。DDR2信号分为以下几组源同步时序信号:Data vs&Data Strobe(读方向和写方向);Data Mask vs&Data Strobe (读方向和写方向);Data Strobe vs&Clock;Address/Command/Control vs&Clock[2]。

与传统的公用时钟技术相比,源同步技术显著提高了总线速度的最大值。由于公用时钟总线中存在器件延时和PCB走线延时,而且PCB走线的长度也不可能超过某个最大的极限值,这为总线的最快运行速度设置了难以逾越的理论极限。而源同步设计取决于数据信号和选通信号之间的延时差,而不是数据信号的绝对延时,因此源同步总线没有理论上的频率极限。然而数据信号和选通信号的延时差与许多因素相关,如同步开关噪声、走线长度、走线阻抗、信号完整性以及缓冲器特性等,在实践中,还是对应存在许多频率极限。

本设计中选用Micron公司的MT47H64M16HW-3LIT芯片作为DDR2颗粒,该芯片支持外部数据传输率400 MHz或533 MHz,用户根据不同的需求可以配置参数从而实现不同的速率。本系统采用5片该型号DDR2颗粒进行位扩展组成64位数据总线和8位ECC(Error Checking Correcting)效验的工作方式。为了叙述方便将MPC8349E与DDR2接口的信号线分为以下4组[3]:

数据组(MDQS/MDQS#[0:8]、MDM[0:8]、MDQ[0:63]、MECC[0:7]);

地址组(MBA[0:2]、MA[0:15]、MRAS#、MCAS#、MWE#);

命令组(MCS#[0:3]、MCKE[0:3]、MODT[0:3]);

时钟组(MCK/MCK#[0:5])。

2 DDR2 PCB布线规则

PCB布线时,按照数据组、地址组、控制组、时钟组及电源的顺序依次布线,相互之间的线间距应该控制在25 mil以上。对于单端信号线,阻抗控制在50~60 Ω内,对于差分信号线,阻抗控制在 50~100 Ω 内[4]。

规则一,对于数据组,要求各小组之内走线在同一层并拥有相同数目的过孔,走线长度差异控制在20 mil内,线间距控制在10 mil以上,所有的信号线走线必须以完整的地层作为参考。不同小组之间,走线长度差异控制在100 mil之内。同时5个小组内部也有对应关系,即MDQS/MDQS#[0]、MDQ[0:7]、MDM[0]为一组对应关系,依次类推。

规则二,对于地址组和命令组,信号线长度差异控制在100 mil之内线间距控制在10 mil以上。走线以1.8 V电源平面或完整的地层作为参考层。

规则三,对于时钟组,差分信号对内走线差异控制在10 mil内,尽量在同一层走线,如果需要换层,2根差分信号线应该一起换。

3 使用Cadence进行DDR2仿真

在高速设计中,如果处理不当,有可能会导致整个系统的失败,所以必须重视高速设计中的仿真。从 PCB的设计角度来讲,要做到严格的时序匹配,以满足波形的完整性,这里有很多的因素需要考虑,所有的这些因素都是会互相影响的。但是,它们之间还是存在一些个性的,由于篇幅有限,本文讨论其中的 PCB叠层、阻抗、互联拓扑和时序因素[5]。

3.1 PCB 的叠层(stackup)和阻抗

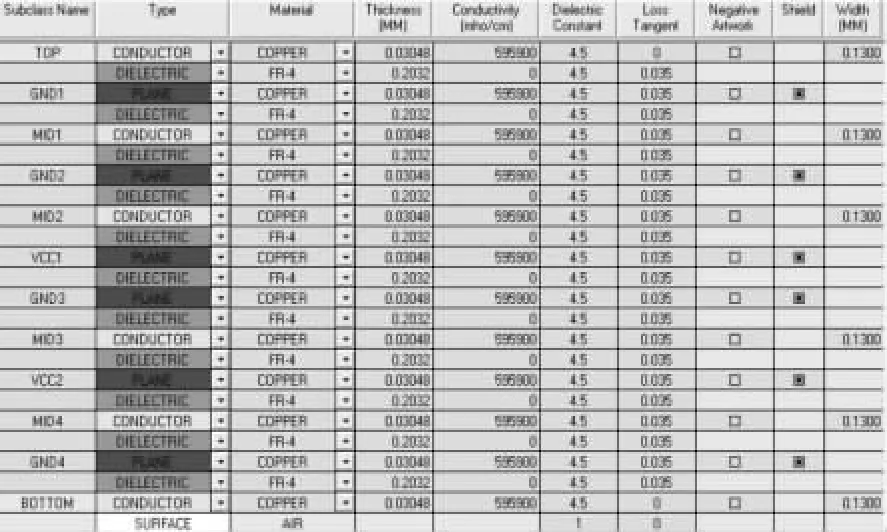

根据BGA出线的要求,然后考虑走线密度,信号的参考平面(电源层和地层),有几组交叉的(线宽间距),最终确定布线叠层。通过设置不同层数的PCB仿真得到波形,对比发现采用12层的PCB波形信号质量最好。因此本系统采用12层板, 其中 2、4、7、11 层是地层;6、9 层是电源层;1、3、5、8、10、12层是信号层。本系统的叠层如图1所示[6]。

图1 层叠设计图Fig.1 Stickup design graph

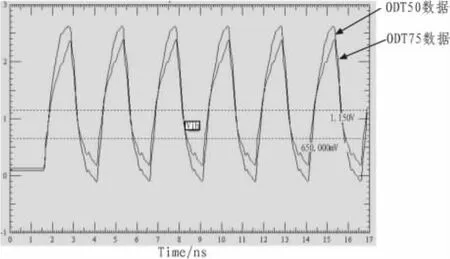

在仿真设置中,DRAM的仿真模型设置3种:U48B_IT_DQHALF_ODT50_533,U48B_IT_DQHALF_ODT75_533,U48B_IT_DQHALF_ODT150_533。 分别对应 ODT 为 50 Ω, 75 Ω,150 Ω的仿真模型。选择ODT为50 Ω和75 Ω进行仿真,波形如图2所示。

图2 ODT为50和75 Ω对应的仿真数据信号波形图Fig.2 Simulation data signal waveform graph:ODT=50 and ODT=75

从仿真结果的信号波形可以看出波形的差异,ODT50模式下波形效果最佳。通过上述拓扑仿真图,ODT模式选择为50 Ω。由于 DDR2的设计时阻抗必须是恒定连续的,因此,单端走线的阻抗匹配电阻 50 Ω必须被用到所有的单端信号上,并做到阻抗匹配;而对于差分信号,100 Ω的终端阻抗匹配电阻必须被用到所有的差分信号终端,比如CLOCK和 DQS等信号。另外,所有的匹配电阻必须上拉到VTT(0.9 V),PCB基板材料选用FR-4,要求单端阻抗控制在50 Ω(±10%)。

3.2 互联通路拓扑

目前的拓扑结构通常有:点到点(基本上目前高速信号所用的拓扑结构);多点(菊花链型、树型、星型等等,多用于低速多负载)。本系统中CPU连接5片DDR2颗粒,地址信号和控制信号为一驱五的拓扑结构,选用菊花链还是星型对称拓扑进行布线,涉及到布线层数和信号质量等问题。我们需要的拓扑结构是既能占用最少的布线通道和布线层数,同时又能保证良好的信号质量。以下是菊花链拓扑结构预布局,用Cadence仿真抽取到的拓扑结构如图3所示。

图3 DDR菊花链拓扑结构设计图Fig.3 DDR daisy chain topology structure design graph

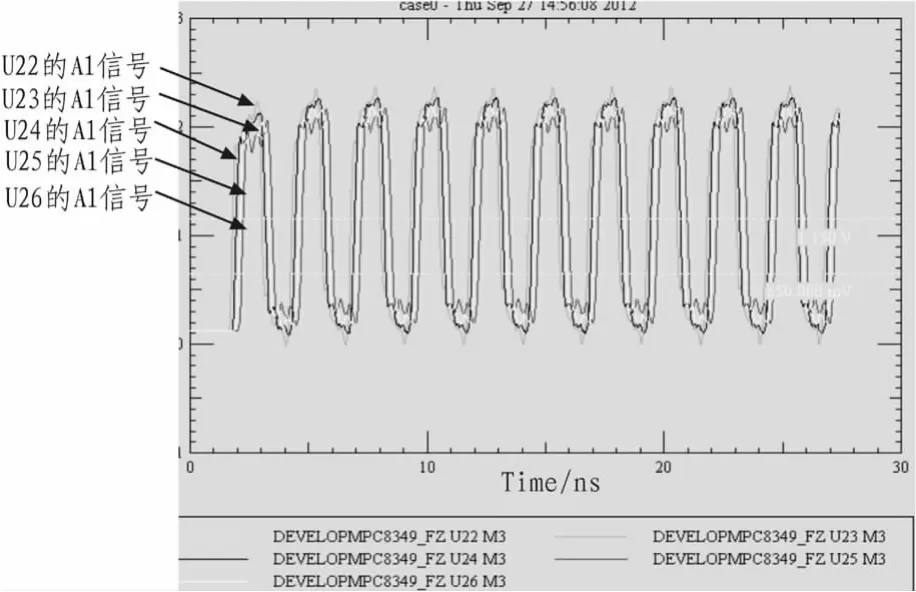

SI仿真扫描得到的典型状态下负载端波形如图4和图5所示。其中图4为5片DDR2颗粒地址信号(A1)接收负载波形,满足信号的单调性、小的过冲及小的振荡。

图4 菊花链拓扑结构状态下A1接收端负载波形Fig.4 A1 receiving terminal load waveform for daisy chain topology

图5为数据信号(D4)接收负载波形,从图中可以看出信号的波形满足其完整性(良好的单调性、小的过冲及小的震荡)的要求。

图5 菊花链拓扑结构状态下D4接收端负载波形Fig.5 D4 receiving terminal load waveform for daisy chain topology

上述仿真的结果显示菊花链拓扑结构可以满足系统对信号完整性的要求,因此,在本设计中的5片DDR2采用菊花链式拓扑结构。

3.3 时序分析

时序电路根据时钟的同步方式的不同,通常分为源同步时序电路 (Source-synchronous timing)和共同时钟同步电路(common-clock timing)。本系统采用源同步方式仿真,源同步时序电路也就是同步时钟由发送数据或接收数据的芯片提供。

对数据和时钟信号进行拓扑抽取,成功抽取后的结构放在同一界面,如图6所示。

进行仿真,仿真后的波形如图7所示。

对时钟信号和数据信号的波形进行测量,得到数据线和时钟线间的延时约0.28 ns,而DDR2芯片datasheet给出的指标为0.38 ns,可以满足源同步系统设计要求。

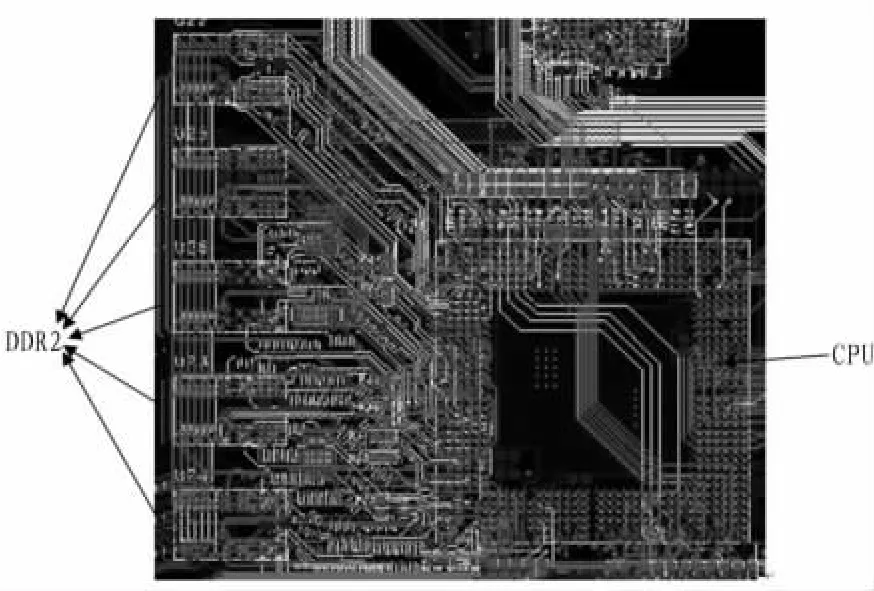

依照上述布线规则和仿真结果,设计的PCB效果如图8所示。

4 结束语

图6 时序仿真拓扑结构Fig.6 Topology of timing simulation

图7 时序仿真波形Fig.7 Timing simulation waveform

图8 DDR 2布线效果图Fig.8 PCB layout graph of DDR 2

本系统通过Cadence进行了布线前仿真以及布线后仿真,取得良好效果,设计生产完成的模块投入使用后,CPU系统在最高工作频率下工作稳定。本系统中MPC8379E与DDR2之间的布线是整个系统成功的关键,上面介绍的只是其中关键的规则以及重要网络走线,制作中还会遇到很多问题,需要在实际运用中加以体会和总结。

[1]Freescale Semiconductor.MPC8349EA PowerQUICC II Pro Integrated Host Processor Hardware Specifications.[EB/OL].[2011-09-13].http://cache.freescale.com/files/32bit/doc/ref_manual/MPC8349EAEC.pdf.

[2]Micron Technology.MT47H64M16 DataSheet.[EB/OL].[2007-11-11].http://www.micron.com/~/media/Documents/Products/Data%20Sheet/DRAM/1Gb_DDR2.pdf.

[3]JESD79-2E, DDR2 SDRAM Specification.USA:Joint Electron Device Engineering Council[S].2008.

[4]许晓平,孙晓彦,程传胜.PCB设计标准教程[M].北京:北京邮电大学出版社,2008.

[5]张木水,李玉山.信号完整性分析与设计[M].北京:电子工业出版社,2010.

[6]Cadence Inc.Allegro PCB SI UserGuide[M].Berlin:Cadence Inc,2007.