基于TMS320C6455的红外与可见光实时图像融合系统硬件设计

2013-07-06王鹏,李飚,刘斐

王 鹏,李 飚,刘 斐

(国防科技大学ATR国防重点实验室,长沙 410073)

随着信息技术高速发展和计算机技术的日新月异,数字图像处理技术已深入广泛地应用于各行各业当中,同时也对图像处理技术提出了更高的要求[1-7]。单一传感器的图像处理已经不能满足现有技术发展,如何实时、快速地将不同传感器获得的同一场景的多幅数字图像融合处理已成为当前图像处理领域的一大热门研究课题。但在这些数字图像处理系统中,一个突出的问题就是数据量庞大,数据处理相关性高,实时实现比较困难。因此,图像处理速度成为影响实时性的主要因素,这就要求实时图像处理系统必须具有强大的运算能力。本文主要论述以 TI公司TMS320C6455DSP为处理器的图像处理系统整体设计方案。

1 图像融合系统原理及系统硬件设计

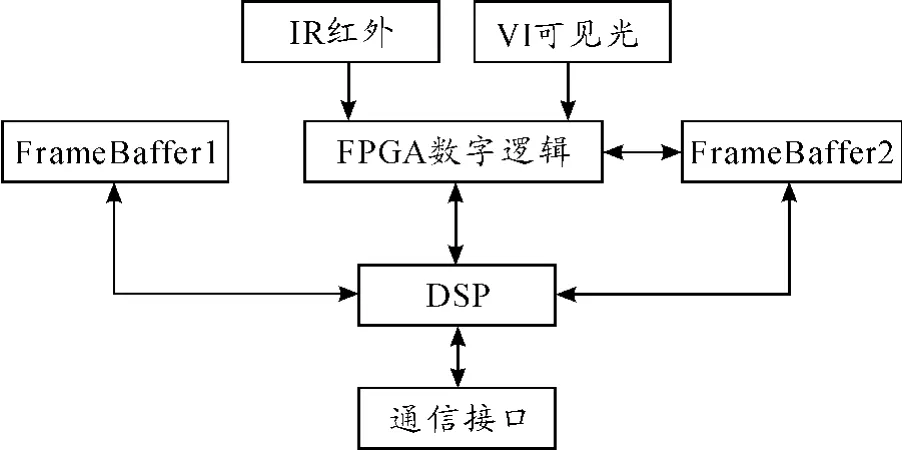

图像处理系统主要用于图像的预处理、图像配准、图像融合等,图像处理系统的设计理念是基于现有的理论基础和算法,将其应用于实际中,使理论与实际结合,同时有效地验证理论与算法的一致性。图像处理系统主要解决准确性和实时性2个方面的问题。由于高速数字处理技术的日益成熟,DSP芯片的不断更新,使图像处理系统的处理速度不断得到提升,图像处理系统的准确性和实时性得到进一步完善[8]。可见光与红外图像融合系统的重点在于图像融合系统的设计,图1是图像融合系统的原理框图。

如图1所示,系统接收到红外图像和可见光图像后,令FPGA数字逻辑对红外图像和可将光图像进行预处理,并通过FrameBaffer对预处理过的可见光图像和红外图像进行帧存,利用DSP对帧存的数字图像进行提取、配准和图像融合,并通过DSP系统对图形进行进一步的目标检测、识别,并通过通信接口将图像识别信息输出。

图1 图像融合系统的原理框图

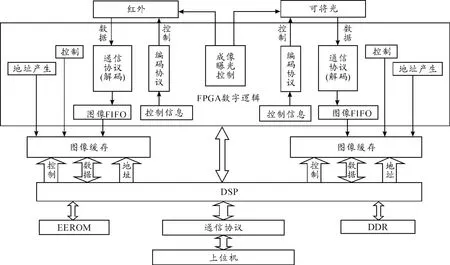

根据系统原理框图,本系统的硬件设计主要分为4个模块:FPGA模块、程序存储-引导模块、图像存储模块、DSP处理模块。图2是系统的硬件设计框图。

图2 图像融合系统硬件设计框图

2 系统中各功能模块的作用

2.1 DSP 模块

本系统中的核心器件是DSP,DSP的性能直接影响到图像处理平台的性能。由于在进行图像处理过程中要处理大量的数据且计算复杂,而且要求计算结果精度高,因此,必须依据系统选择合适的DSP芯片。在选择过程中主要考虑以下因素:

1)在本设计中主要处理的图像信号的每个像素的灰度值占用2个字节,即16bit,在数据位数相同的情况下,定点DSP芯片和浮点DSP芯片的运算精度相同,且定点DSP芯片功耗、成本、体积较浮点DSP芯片小,易于实现,稳定性好。因此,本设计中选择定点DSP芯片完全满足设计要求[9-10]。

2)选择具体的DSP芯片。DSP芯片的运算速度是反映DSP芯片性能的重要指标,它也是在选择DSP芯片时的考虑因素。DSP芯片的运算速度采用DSP的指令周期、单周期的乘加次数或采用数字信号处理中的基准程序。由美国仪器(TI)公司推出的高端芯片TMS320C6455具有较强的运算能力,其主频达到了1 GHz,具有1 ns的指令周期,每周期执行8条32位指令,最大峰值速度达到8 000 MIPS。TMS320C6455还带有 Seria/RapidlO(r)总线,互连速率高达25 Gbits/s,实现了极高的多处理性能,降低了系统消耗,比此前的外部存储器接口快12倍。TMS320CC6455片内是基于C64xx内核的L1/L2存储结构,片上集成有大量的存储空间,L1P为32 k字节,L1D为32 k字节,L2为2M字节,比此前C64x器的存储器容量件翻一番,其中L1P和L2都可直接映射到存储空间,能满足本设计的实时性要求[9-10]。

TMS320CC6455的外围总线包括1个内部集成电路总线(I2C)、2个多路缓冲串口总线(McBSPs)、2个64位通用定时器(可以配置成4个32位定时器)、1个可配置的16位或32位主机接口(HPI16/HPI32)、1个PCI总线、1个16管脚的通用输入/输出端口(GPIO)、1个10/100/1000M 以太网媒体访问控制器(EMAC)、1个32位DDR2 SDRAM接口。

工作原理:DSP经过上电复位后,利用写事件置位寄存器(ESR)启动 EDMA,EDMA通过 Pa-RAM获取地址信号,将所需数据及程序经过EMIF从外设存储器中读取并将其送入数据cache(L1D)和程序cache(L1P)中,CPU通过2条地址总线(DA1和DA2)向DMC提交数据访问申请后,访问程序cache(L1P)和数据cache(L1D),并经过取数总线LD1和LD2将数据送入CPU中进行处理;待CPU将数据处理完毕后,CPU通过2条地址总线(DA1和DA2)向DMC提交数据访问申请后,将所得数据通过存储总线ST1和ST2将数据写入数据cache(L1D);通过EDMA将数据传输至系统的外设DDR中,供系统下一步的处理工作使用;利用DSP在运行中产生的控制信息和地址信息,将存储在缓存区的图像信息进行提取并传输至DSP进行处理,通过通信协议将处理过的图像信息调制传输至上位机;传感器的控制信息由DSP写入,通过调制后经过高速串行通信链路发送至传感器,实现对传感器的控制。

2.2 FPGA 模块

本处理系统中的FPGA选择使用美国赛灵思(Xilinx)公司的Spartan6系列。Spartan6是第6代Spartan系列产品,基于45 nm技术、9层金属布线、双栅极氧化层工艺技术生产,在前几代Spartan系统的结构基础上,利用了成熟可靠的Virtex高端系统构架。它提供的资源包括高级功耗管理、高效双寄存器6输入LUT、高达150 000个的逻辑单元、片上PCI Express硬件模块、高级片外存储器控制器MCB(memory controller block)、250 MHzDSP SLICE和3.125Gbit/s低功耗收发器等。Spartan6 FPGA为能为本系统提供最佳的低风险、低成本、低功耗和高性能的解决方案。

由于系统需要,在FPGA内部需要设计多个FIFO(先进先出寄存器),即以先读入的数据先寄存,先读入的数据先读取的方式。通过高速串行通信链路传输至FPGA中,将信号解调为16字节数据,以20 MHz/像素暂存。当FIFO写满时,将数据送入图像缓存,节省了等待和查询时间,能有效提高传输速度。

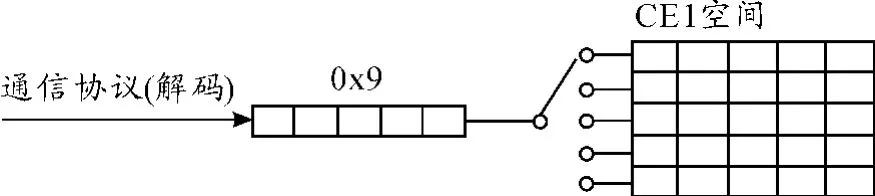

工作原理:成像曝光控制模块控制红外传感器和可见光传感器,并对传感器的曝光参数进行控制;而后传感器将图像信号传出,通过高速串行通信链路接收并传输至FPGA中;图像信号通过通信协议(解码)模块解调为16字节数据,以20 MHz速率将图像信息暂存于FIFO中;FIFO的读出和写入都是由FPGA来控制,当暂存数据达到N个像元后,FIFO的状态电路发出1个数据写满信号;FPGA根据FIFO的写满信号,将FIFO中的数据读出,按图像信息存储器DDR的地址顺序将数据写入进行存储,FIFO数据传输流程如图3所示。

图3 FIFO数据传输流程

2.3 图像存储模块

本系统的图像存储模块由DDR组成,主要用于对FIFO中的待处理图像信息的存储和经过DSP处理后的图像信息的储存。图像存储模块则采用Infineon公司的DDR-500 256M系列芯片,它具有2倍的内存预读写能力,由于其采用封装形式,具有良好的电器性能与散热性,且TMS320C6455带有的DDR2 SDRAM存储器接口,可以实现与32位存储器件的无缝连接。存储器的运行时钟直接由PLL2进行控制,时钟为PLL2输入时钟的10倍。DDR的刷新由 TMS320C6455自动控制。

工作原理:DDR通过DMA将信息传输至DSP,在传输信息之前首先由主控寄存器和副控寄存器设置DMA通道PRICTL寄存器的START=00b及SECCTL寄存器,并对DMA通道源/目的地址寄存器以及传输技术寄存器进行设置;然后对主控制寄存器START写入11b,以自动化方式启动DMA;图像数据通过DDR2 SDRAM接口传输至DSP的数据cache(L1D)中,供DSP的处理使用;当DSP将图像信息进行处理之后,已处理图像信息经过DMA写入DDR存储器中进行存储。

2.4 程序存储-引导模块

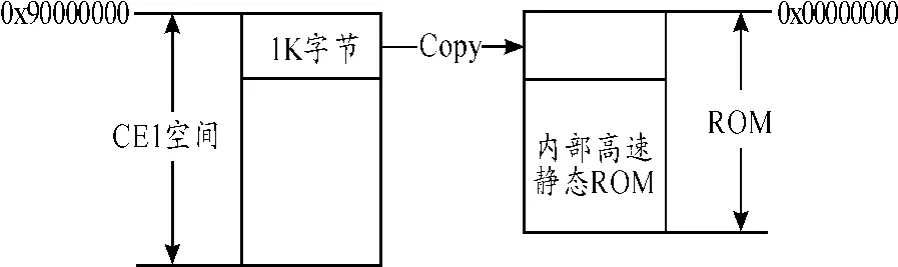

本系统的程序存储-引导模块是由EEROM电子抹除式可复写只读存储器构成。EEROM具有高性能、低功耗的特点。首先,一般的DSP外围的存储器的存取时间在70~150 ns,在本系统中直接让程序在EEROM中运行势必影响DSP处理器的运行速率和效率,DSP程序需要在速率更快的外部 DDR中运行。其次,当 DSP上电时,会将EEROM的前1k空间的内容复制至片内L2 SRAM中的0x800000到x8003FF地址空间,复制完成后DSP会从0x800000地址处开始运行,但需要搬运的程序的向量表、初始化段等往往超过1k大小,不能有效的在系统上电时自动引导应用程序运行,因此本系统采取DSP处理器的EMIF ROM/Flash boot模式进行DSP启动。图4为DSP EMIF ROM/Flash模式的启动过程。

工作流程:系统上电后固化在DSP内部ROM中的“boot loader”将EEROM的前1k空间的二次引导代码复制到片内L 2 SRAM的0x8000000到x8003FF地址空间;复制完成后DSP从0x800000地址处开始运行,也就是说DSP运行二次引导,此时,DSP将EEROM空间起始地址为0xB0020000的数据按照section指定的地址复制到DDR;复制完成后,二次引导代码跳转到程序初始化入口处(_c_int00),加载过程结束。

图4 DSP EMIF ROM/Flash模式的启动过程

3 结束语

数字图像处理的广泛应用及硬件技术的日新月异断推动数字图像处理技术的迅速发展,也促使数字图像处理系统的实时性和准确性得到不断提升。本文主要使用最新的数字信号处理芯片TMS320C6455,结合可编辑门阵列FPGA,探讨了了实时图像处理系统的设计原理及系统的硬件设计,并介绍了所属模块在系统中的功能。

[1]张建勋,谢婷婷.基于小波区域梯度的图像融合新算法[J].重庆理工大学学报:自然科学版,2012,26(10):51-55.

[2]宋英姿.基于第二代Curvelet变换的多聚焦图像融合[J].四川兵工学报,2010(3):115-116.

[3]黄宁宁,贾振红,何迪,等.改进的模糊熵与图像局部信息相结合的遥感图像分割新算法[J].激光杂志,2010(6):20-22.

[4]王建,刘肖,王国珲 .基于梯度变换的多传感器图像融合算法[J].重庆理工大学学报:自然科学版,2012,26(10):62-65..

[5]文江平,胡岩峰,王无敌,等.一种有效的SAR图像水陆分割方法[J].四川兵工学报,2010(2):108-110..

[6]张利红;梁英波.基于改进小波变换的医学图像融合算法研究[J].激光杂志,2012(5):23-24.

[7]张莲,秦华峰,余成波.基于人体手指静脉图像分割算法的研究[J].压电与声光,2008(2):233-235.

[8]李方慧,王飞,何佩琨.TMS320C6000系列DSPs原理与应用[M].北京:电子工业出版社,2004:60-156.

[9]孙兴,李捍东,田申.DSP6416在数字图像处理中的应用[J].贵州工业大学学报:自然科学版,2005(6):67-71.

[10]邢素霞.基于DSP与FPGA的红外与可将光实时图像融合系统硬件设计[J].北京:北京工商大学学报:自然科学版,2008(6)::44-47.