GPS接收机C/A码跟踪算法及环路控制策略

2013-07-05雷明东孙函子

胡 辉,方 玲,雷明东,孙函子

(华东交通大学信息工程学院,江西南昌330013)

目前,对高动态GPS接收机的研究重点集中在基带信号处理算法上。在高动态环境下,伪码相位随载体运动而发生较大的变化,通常设计中码跟踪环在没有载波跟踪环辅助的情况下很难可靠工作。因此需设计相应的伪码跟踪环路对动态引入的码相位误差进行精确的估计。

目前高动态伪码跟踪算法主要有开环算法和闭环算法两类。开环跟踪直接对输入信号的码相位进行估计,对载体动态变化适应能力强[1],但运算量大且环路复杂,难以适应实时处理的需要。闭环跟踪算法主要对伪码相位延迟进行估计,能获得精确的伪码延时测量值,且运算量较小。在高动态GPS基带信号处理算法中,通常采用闭环跟踪算法[2]。目前广泛应用的鉴相算法是超前-滞后鉴相算法[3-4]。该算法的性能依赖于信号幅度和载波环的性能,且运算量很大,很难满足系统对实时性的要求。针对上述问题,本文主要研究的是与高动态载波跟踪算法[5]相匹配的伪码跟踪算法,该算法是基于载波辅助技术的归一化非相干点积功率伪码跟踪环而进行研究的,此算法中还包括了预检积分时间可变的伪码跟踪环路控制策略。

1 GPS接收机伪码跟踪技术研究

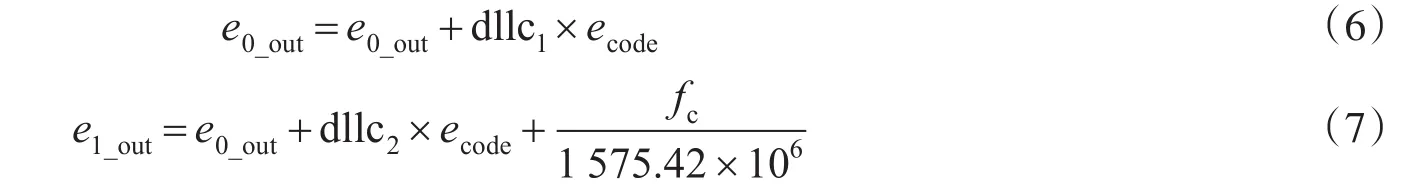

捕获以后,输入信号码相位和本地信号码相位误差在1个码片范围内,然而,GPS接收机伪码跟踪的目的是调整本地码相位使之与输入信号码相位精确对准,使码相位残差可以减小到百分之一个码片以内。伪码跟踪通常采用DLL环来实现[3,5-9]。GPS接收机码跟踪环主要由码环鉴相器,环路滤波器和码NCO构成,其结构如图1所示。相关器输出一般有六路相关值,即同相的超前(IE)、滞后(IL)和即时(IP)支路,正交的超前(QE)、滞后(QL)和即时(QP)支路。为了便于实现,图1中将超前和滞后支路合并。相关器输出四路相关值,分别为同相和正交的超前-滞后支路(IE-L,QE-L)和即时支路(IP,QP),即时支路如式(1)、(2)所示:

图1 GPS接收机码跟踪环的结构框图Fig.1 The structure diagram of GPS receiver's code tracking loop

采用的归一化的非相干点积功率型鉴相器的鉴相函数如式(3)所示

由式(3)知,其中ecode为伪码相位残差,ecode只与伪码相位偏差ε(k)有关。2δ=d,d即超前与滞后支路的相关间隔。归一化消除了鉴相函数对幅度的敏感性,也消除了环路对数据位跳变的敏感性。将自相关函数公式带入式(3)化简可得式(4)

由鉴相特性函数式(4)可知,归一化的非相干点积功率DLL鉴相器工作范围与相关间隔d有关。其中,为鉴相范围。在高动态环境下,要折衷选择d。对于无辅助的码跟踪环路,为保证鉴相器的工作范围,d通常取1 chip。当采用载波跟踪环辅助码跟踪环时,d可以取得较小(d取0.5 chip),可有效减少环路中热噪声引入的误差。

2 伪码跟踪环路控制策略

2.1 预检积分时间可变的伪码跟踪环路控制策略

为兼顾码跟踪环的动态性能与噪声性能,必须合理地选择环路的预检积分时间。由码环热噪声公式可知,当d取0.5 chip时,化简热噪声误差公式如式(5)所示[9]。

式中:Bn为环路噪声带宽(Hz),为信号载噪比(dB-Hz);为双边带前端带宽(Hz),取值为为伪码周期(s),T为预检积分时间(s);fc为码片速率。

环路预检积分时间的增长受数据位跳变的制约,通常不超过20 ms。将预检积分时间增加到20 ms,在理想的情况下,对于相关间隔为0.5 chips的伪码跟踪环路而言,可以额外获得6 dB的热噪声颤动门限改善[9]如图2所示。

优良的伪码跟踪环路控制策略应为:在初始跟踪阶段,码跟踪环的更新时间选择1 ms,以便适应环路对动态应力的需求。进行位同步以后,估计出数据位跳变的位置,可将预检积分时间增长为20 ms,以提高伪码测量精度。

图2 环路热噪声与载噪比和预检积分时间的关系Fig.2 The relation table among the thermal noise,C/N0 and pre-detection integration time

2.2 载波辅助技术与环路带宽的设计

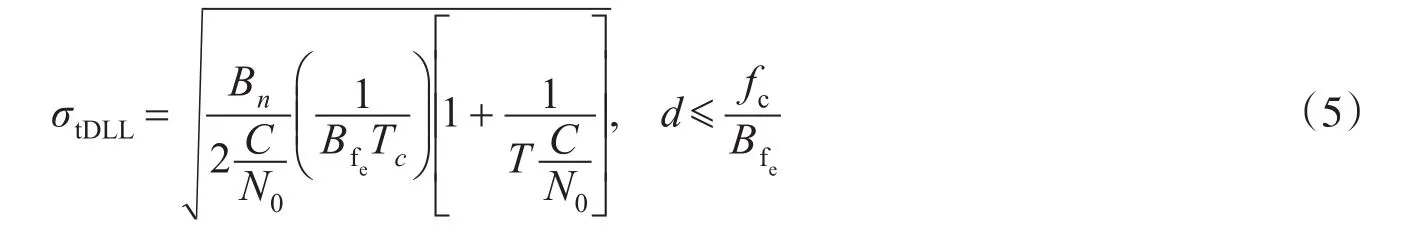

码环鉴相器输出的码相位误差ecode通过环路噪声带宽为Bn的二阶Jaffe-Rechtin滤波器,在载波跟踪环有稳定输出时,采用载波环辅助的码跟踪环的公式如式(6),(7)所示。

式中:e1_out为环路滤波器的输出是滤波器参数,ω0为环路的固有频率,fc是码片速率,为载波环对码环提供的辅助,该辅助降低了码跟踪环对动态的要求,而仅考虑其热噪声性能,Bn可选用更小的值,可有效减少环路中的噪声。

码跟踪环设计中,跟踪阈值的经验取值为

式中:σDLL为测量误差的均方根;σtDLL为热噪声引入误差的均方根;Re为因接收机的动态性导致码跟踪环引入的动态误差。

对于无载波环辅助的码环的设计,首先考虑载体动态引入的误差。

式中:m为环路阶数;ω0为环路的固有频率。m=2时,dRm/dtm为载体最大视线方向上的加速度动态,m=3时代表最大视线方向上的加加速度动态。

在采用载波环辅助码环技术时,环路跟踪门限主要由热噪声决定。对于非相干的DLL鉴别器,伪码跟踪环热噪声引入的误差公式如式(5)所示。

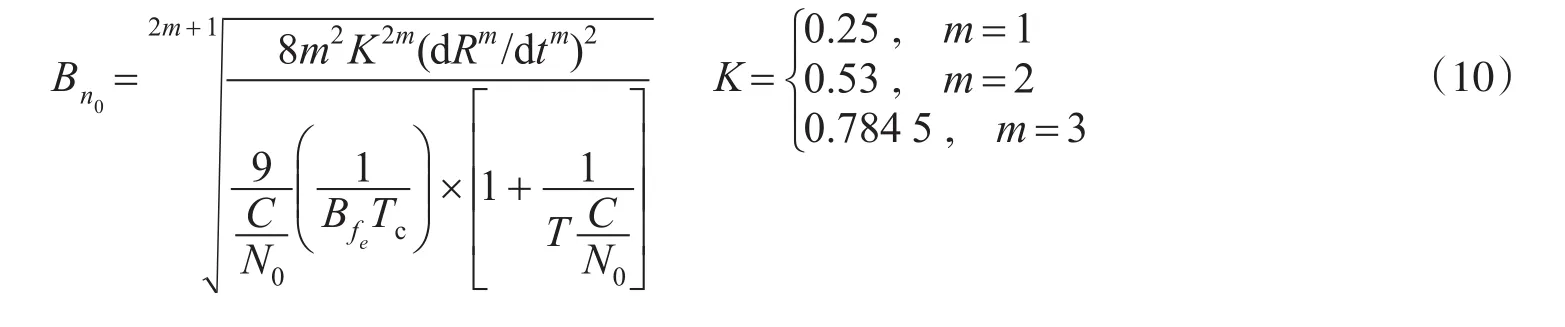

在设计环路带宽时还要求环路带宽尽量接近最佳带宽。所谓的最佳带宽就是环路跟踪误差最小时对应的环路带宽。满足的Bn0就是环路的最佳带宽,最佳带宽的计算公式如式(10)所示。

3 算法仿真

3.1 算法流程

在分析伪码跟踪环时,可认为载波跟踪环已有稳定的输出,图3为伪码跟踪策略的程序流程图。

图3 码跟踪策略的程序流程图Fig.3 The program flow chart of code tracking strategy

本算法采用C/A码伪距测距方案,因此,通过优化伪码跟踪环设计方案,提高伪码跟踪环的精度,从而可以提高测距精度,最终提高系统定位精度。本文中主要采用上文提出的预检积分时间可变的环路控制策略来优化伪码跟踪环设计方案。以位同步是否成功作为环路切换的条件,将伪码跟踪分为两个阶段:预检积分时间为1个码周期的阶段为环路的粗跟踪阶段,在有载波辅助的情况下,伪码跟踪环的粗跟踪阶段持续1 s。接着进行1 s的位同步,估计出数据位跳变的位置。

如果位同步成功,环路等待输入数据中下一个比特跳变起始的位置,从新的比跳变的位置开始收集I、Q路相关值作为精跟踪阶段环路的输入,这样可以消除数据位跳变对码环性能的影响,可以将预检积分时间延长至20个码周期。此时环路进入有载波辅助的精跟踪阶段,即伪码跟踪环的预检积分时间为20个码周期的跟踪阶段。如果1 s内位同步不成功,则继续进行位同步,直到达到设定的最大时间tmax。其中tmax值的选择可以根据接收机的使用环境决定。出于系统稳定性考虑,当达到或超过tmax,环路仍不能位同步,则宣布伪码跟踪环失锁。根据失锁前保存的相关信息,程序回到捕获状态重新进行信号的捕获。本方案中采用环路控制策略,既满足了动态指标,又在此基础上兼顾了接收机对精度的需求。

3.2 实验分析

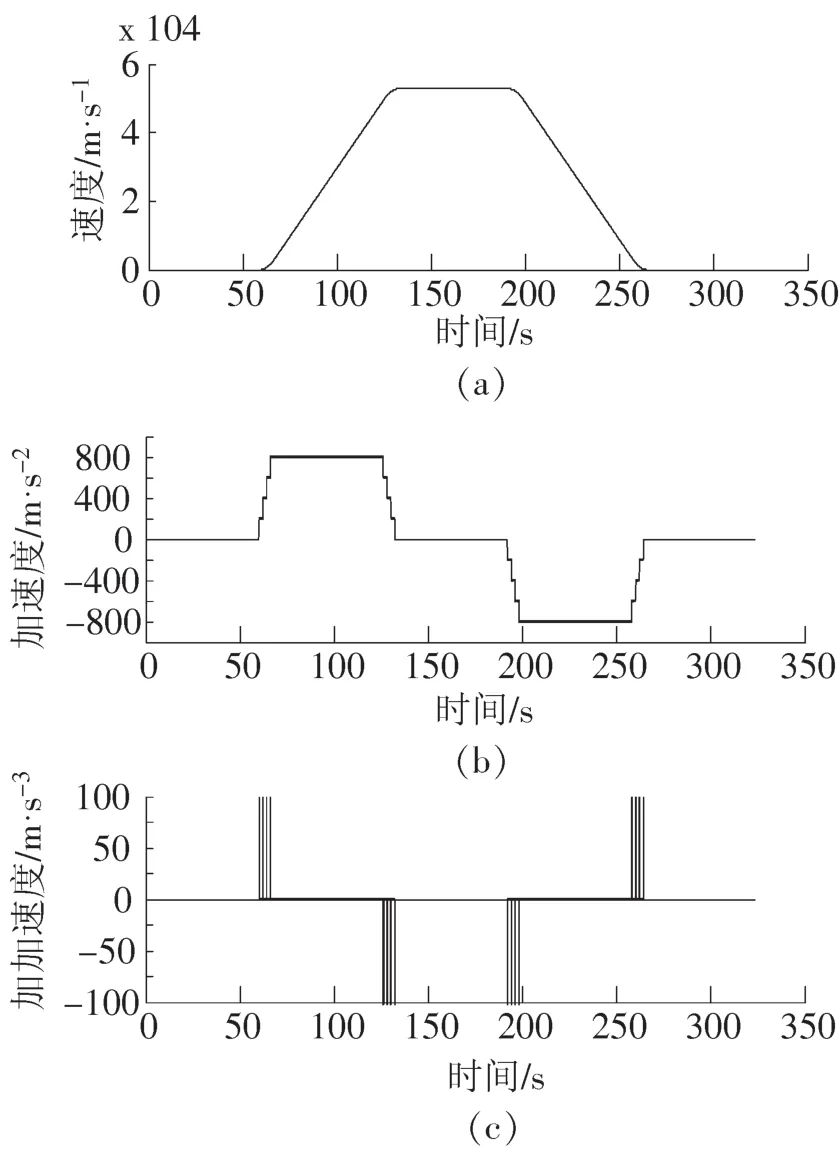

GPS信号模拟器模拟载体的运动状态如图4所示,载体运动的时间为324 s,共分9段,其中包含静止、匀速直线运动、加速度为±80 g的匀加速直线运动、加加速度为±10 g·s-1的变加速直线运动。在捕获阶段,一般要求本地伪码的码元误差在±0.5 chip范围内。在跟踪阶段,要将这个误差进一步缩小并保持在误差允许的范围以内。为了满足系统定位精度的要求,在跟踪阶段,本地伪码的码元误差要求在±0.02 chip范围内。

GPS接收机中常用Jaffe-Rechtin数字滤波器。文献[9]给出了一、二、三阶滤波器的特性。环路的稳态误差与接收机到卫星间的视距R的n阶(n即环路阶数)导数成正比,与环路带宽Bn成反比。根据本文给出的载体动态指标可知,为了跟踪相位加加速度信号,必须采用三阶或二阶DLL环实现伪码相位的跟踪。

本文采用载波跟踪环辅助伪码跟踪环技术,通过载波跟踪环消除载体大部分动态,此时伪码跟踪环阶数可降为一阶。但考虑到高动态接收机稳定性和可靠性的需要,所以本文采用的是二阶Jaffe-Rechtin滤波环 路 ,选 择ξ=0.707,结 合 公 式(10)可 得Bn=0.53ω0。一阶环路和三阶环路的相应参数可参考文献[9]。

图4 载体运动状态Fig.4 The motion state of carrier

依据上述分析,在无载波辅助的情况下,应考虑载体动态性对伪码跟踪环的影响,结合动态指标可知,伪码跟踪环的环路带宽必须有Bn≥1.73 Hz。在无载波辅助的情况下,环路带宽采用Bn=1.73 Hz,此时码环鉴相器输出如图5所示。

结合载体的运动轨迹对图5进行分析。当载体处于静止状态时,环路的鉴相误差保持在±0.02 chip范围内;载体处于高动态运动时,考虑载体动态性对伪码的影响,此时环路的鉴相精度急剧变差,输出的码相位误差峰峰值为0.2 chip。当载体再次处于静止状态时,码环输出的鉴相误差重新回到±0.03 chip范围内。对输出的数据进行统计分析,其数学期望为4.029×10-4chip,标准差为0.031 2 chip。由以上分析可知,此时码环性能较差,不能满足系统对定位精度的要求。

图6为仅采用环路控制策略时伪码跟踪环输出的码相位误差。处于粗跟踪阶段时,伪码跟踪环能迅速收敛,此时鉴相误差在±0.01 chip范围内。精跟踪阶段时,当载体处于高速匀速直线运动或高动态运动状态时,码环输出的鉴相误差峰峰值为0.12 chip,不能满足系统对定位精度的要求。对其精跟踪阶段输出的数据进行统计分析,其数学期望为3.089×10-4chip,标准差为0.029 7 chip。相较于图5,在载体处于高动态的情况下,采用环路控制策略时伪码跟踪环输出的鉴相误差减小了。采用载波环辅助码环技术消除了伪码跟踪环所承载的大部分动态,此时可以忽略载体动态引入的误差。当载波环已有稳定的输出时,码环跟踪门限主要由热噪声决定。由式(5)可推知Bn≤0.5 Hz。结合d取0.5 chip时相应的最佳环路带宽由式(10)得,Bn选择0.5 Hz。

仅采用载波环辅助码环技术时鉴相器的输出如图7所示。由图7可知,不采用环路控制策略时,伪码跟踪环输出的鉴相误差峰峰值为0.11 chip,不能满足系统对定位精度的要求。对其精跟踪阶段输出的数据进行统计分析,其数学期望为-4.233 5×10-6chip,标准差为0.009 9 chip。比较图6和图7可知,采用载波环辅助码环技术可以消除掉伪码跟踪环所承载的大部分动态,减小码环输出的鉴相误差的标准差,使得码环输出的鉴相误差比较平滑。

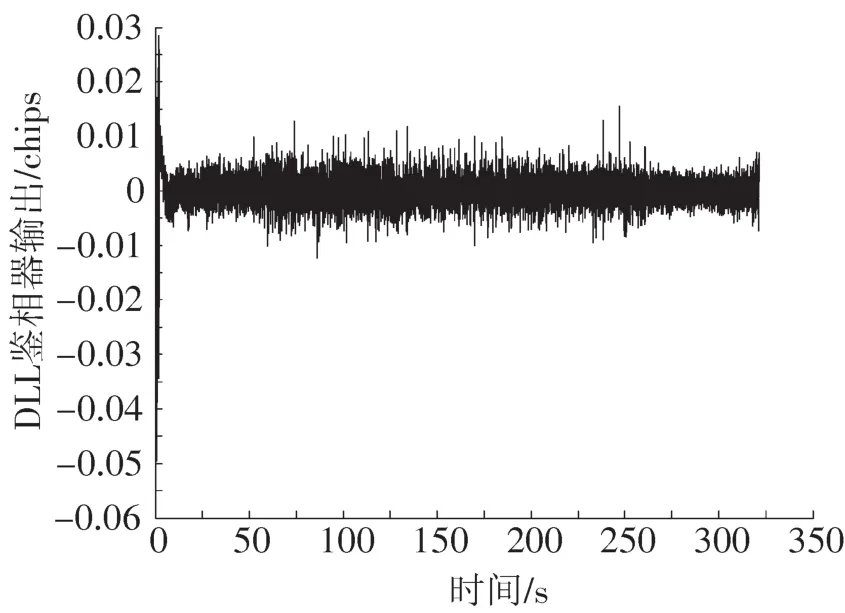

采用载波环辅助码环技术和环路控制策略的码相位误差如图8所示。在粗跟踪阶段和位同步阶段,环路迅速收敛,伪码跟踪环输出的相位误差不超过0.055个码片。进入精跟踪阶段后,伪码跟踪环的相位误差峰峰值为0.02 chip,相位误差的数学期望为-3.883 2×10-6chip,标准差为0.002 2 chip,能很好的满足系统对定位精度的需求。由图8可知,相较于图5、图6、图7而言,伪码跟踪环的性能有了显著的提高。实验证明,采用环路控制策略能兼顾系统对动态性和精确性的要求。

图5 无载波环辅助无环路控制策略时码环鉴相器的输出Fig.5 The DLLdiscriminator output without any optimization

图6 仅有环路控制策略时码环鉴相器的输出Fig.6 The DLLdiscriminator output with control strategies of the code tracking loop

图7 仅有载波环辅助码环技术时码环鉴相器的输出Fig.7 DLLdiscriminator output with carrier aiding

图8 有载波环辅助有码环控制策略时码环鉴相器的输出Fig.8 The DLLdiscriminator output with carrier aiding and control strategies of the code tracking loop

由以上分析可知,当载体处于高动态运动状态时,须采用载波环辅助码环技术,以便消除载体动态性对伪码跟踪换的影响,减小环路带宽,从而减小环路噪声。另外,在精跟踪阶段,采用预检积分时间可变的伪码跟踪环路控制策略,可以改善伪码跟踪环的性能,提高环路的鉴相精度,改善系统的定位精度。

4 结论

对高动态GPS接收机核心算法中的伪码跟踪算法的优化设计进行了分析,并对码跟踪环关键参数的设置进行了详细的介绍,最后讨论了载波环辅助码环技术和环路控制策略对码环性能的影响。基于MAT⁃LAB建立了仿真的系统模型。

通过实验得出如下结论:在高动态环境下,增长预检积分时间,减小相关间隔和环路带宽都能提高环路的精度,但同时将减弱环路对动态应力的适应能力,因此在伪码跟踪环的设计中,首先要合理设计这些关键参数和合理的环路结构。实验结果证明,本文中的设计方案能很好的满足系统对实时性的要求。

[1]NESREEN I,ZIEDAN.GNSS receivers for weak signals[M].Norwood,MA:Artech House,2006:71-85.

[2]孙礼.GPS接收机系统的研究[D].北京:北京航空航天大学,1998:8-11.

[3]李小民.高动态环境GPS应用中的几个关键问题研究[D].北京:北京航空航天大学,1999:15-23.

[4]胡辉,孙函子,纪兆云.高动态GPS载波跟踪算法和环路控制策略研究[J].宇航学报,2011,32(8):1805-1812.

[5]胡辉.高动态数字化GPS接收机的研制[R].上海:上海航天局博士后工作站,2002:51-84.

[6]NABIL J,ALEXANDRE V,MARC J,et al.Implementation of an optimized code loop for indoor positioning[C].Proceedings of the 20th International Technical Meeting of the Satellite Division of The Institute of Navigation(ION GNSS 2007),Fort Worth,TX,2007:1396-1404.

[7]ALAQEELI A S,JVAN GRAAS F.Real-time acquisition and tracking for GPS receivers[J].Circuits and Systems,2003,ISCAS’03,2003(4):500-503.

[8]DAVID M L,JAMES BYT.High Performance Tracking algorithms for software GPS receiver[C].Proceedings of the 18th International Technical Meeting of the Satellite Division of The Institute of Navigation(ION GNSS 2005),Long Beach,CA,2005:1638-1644.

[9]KAPLAN E D,HEGARTY C.Understanding GPS:principles and applications[M].Norwood,MA:Artech House,2005:161-200.

[10]胡辉,叶鑫华.基于GP2010的GPS接收机前端模块实现[J].华东交通大学学报,2008,25(4):75-79.