高性能计算机系统电源研究与实现*

2013-06-07姚信安胡世平

姚信安,宋 飞,胡世平

(1.湖南大学电气与信息工程学院,湖南 长沙 410082);2.国防科学技术大学计算机学院,湖南 长沙 410073)

1 引言

高性能计算机是衡量一个国家科技创新能力和综合国力的重要标志,主要应用于石油勘探、高端装备制造、生物医药、动漫设计、新能源、新材料、工程设计与仿真、气象预报、金融风险分析等领域。

高性能计算机系统对供电电源的要求非常苛刻。单板供电电压种类多达十几种,最高电压稳定度为±1%,最低输出纹波要求为10mV,最大动态响应能力高达数百安培每微秒,所有插件板均要求能够热插拔和热更换,可靠性要求非常高。针对这些特殊要求,本文采用12V母线直流分布式供电系统设计了某高性能计算机的全部电源。详细介绍了计算机柜的总体设计方案和其中最关键的计算主板电源设计,并对计算主板上的关键电源电路参数进行了具体的计算和分析。

2 总体设计

某高性能计算机由N 个机柜组成,其中包含计算机柜和互连通信机柜。在电气上每个机柜相互独立,机柜之间采用光纤实现数据通信。互连通信机柜相对比较简单,本文重点介绍计算机柜的电源设计。

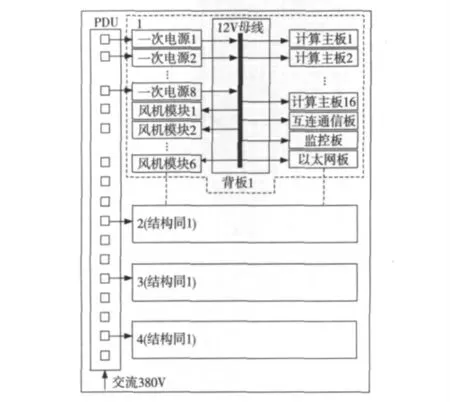

图1示出了单个计算机柜的电源设计框图。

Figure 1 Block diagram of power supply for computing cabinet图1 计算机柜电源设计框图

每个计算机柜分为四个独立的单元,采用12 V 母线直流分布式供电方式。交流380V 电压首先进入到位于机柜侧壁的电源分配单元(PDU)中,PDU 上有数十个电压输出端口,通过电缆连接到一次电源模块的输入端口中。一次电源模块的输出电压为直流12V,八台一次电源模块全部插在背板上,通过背板实现并联冗余。

每块背板上插有16块计算主板、一块互连通信板、一块监控板、一块以太网络板及六个风机冷却模块。所有插件板/模块均采用双面对插方式,分布在背板两面,再通过插座从背板上取电和进行数据通信。每块背板上流过的电流高达1 000多安培,这对于背板的设计和制造都是很大的挑战。

12V 电压进入到各插件板后,首先经过热插拔和滤波电路,然后通过放置在板上的DC-DC 变换器变换成各种直流低电压,供给负载。全部插件板(含风机模块)都支持带电热插拔,为系统维护提供了极大的方便。

3 计算主板电源设计

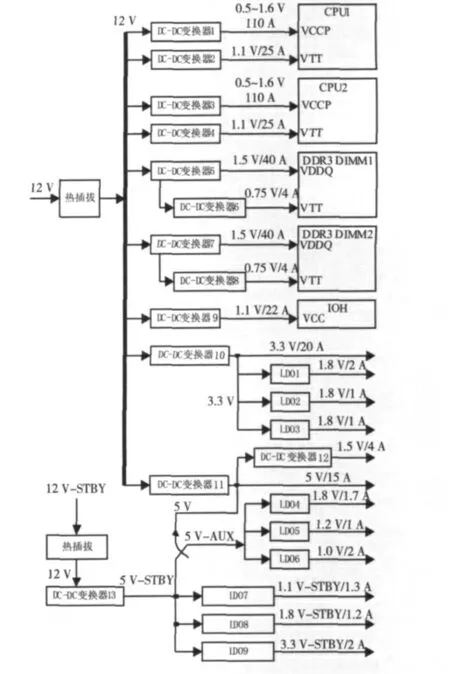

计算主板由多个CPU、多条内存、多个专用集成电路等组成,每块板功耗约800瓦,需十几种工作电压,单路最大工作电流为100A,最高动态响应能力为300A/μs。图2给出了计算主板的电源设计框图。

Figure 2 Block diagram of power supply for motherboard图2 计算主板电源框图

直流12V 主电压和12V-STBY 待机电压从背板通过插座进入到计算主板中,经过热插拔和滤波电路之后,送入到各个DC-DC变换器中,变换成各种不同输出电压、电流和动态响应能力的直流低电压,供给CPU、内存条、IOH、ICH10等芯片。

电源工作原理如下:12V-STBY 待机电压首先建立,产生5V-STBY 待机电压。5V-STBY 电压再通过LDO 线性稳压器变成3.3V-STBY、1.8V-STBY、1.1V-STBY 待机电压,主板上的控制电路开始工作,进行初始化,并等待系统加电命令。当接收到系统加电命令时,控制电路按照预定的时序发出加电命令,逐步将各种DC-DC 变换器加电。当各种电压都正常后,产生系统电压正常信号和复位信号,使CPU、DIMM 条等开始正常工作,从而引导BIOS和操作系统启动。

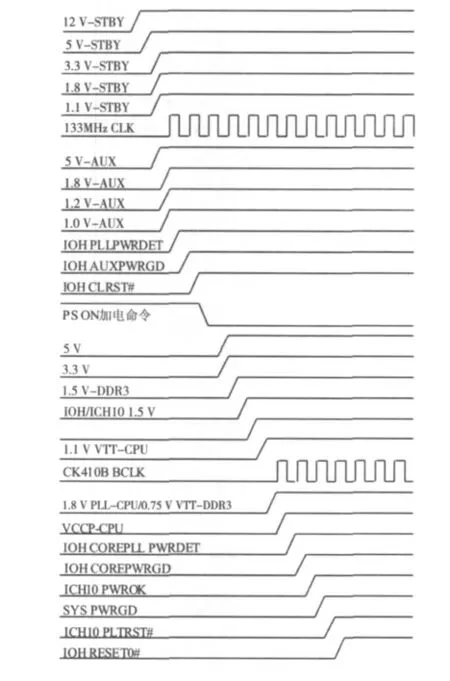

计算主板加电和复位时序框图如图3 所示。由于时序非常复杂,采用了一片可编程CPLD 芯片来完成加电和复位功能。

Figure 3 Power-on and reset sequencing of motherboard图3 计算主板加电和复位时序

计算主板的各种DC-DC 变换器设计,根据供电电流大小及动态响应能力要求,分别采用了单相、两相和多相同步整流buck变换器来实现电压变换。其中,处理器的最大供电电流为100A,最高动态响应能力要求为300A/μs,需按照Intel VRM11.1标准进行供电[1]。

下面重点介绍处理器的电源设计电路。

4 处理器电源设计

处理器的电源通常称为电压调节模块VRM(Voltage Regulator Module)。

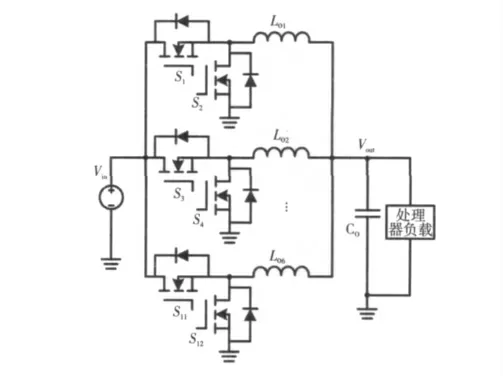

根据VRM11.1供电标准,采用了六相交错并联同步整流buck 变换器,电源框图如图4 所示。其中,Vin为输入电压,S1和S2组 成 第一相,S3和S4组成第二相,S11和S12组成第六相。S1和S2、S3和S4、S11和S12的开关时序为互补关系,S1、S3、S5、S7、S9、S11是各相的主开关管,每周期内相差60度导通;S2、S4、S6、S8、S10、S12为各相的同步整流管。滤波电感Lo1=Lo2=…=Lo6,Co为输出滤波电容。

4.1 回路增益设计

Figure 4 Block diagram of power supply for processor图4 处理器电源框图

对于六相交错并联同步整流变换器来说,每一相的输入电压相同,又共享同一组补偿回路,因此其小信号模型可以等效成一个等效电感等于每相电感的1/6、等效开关频率等于每相开关频率6倍的单相同步整流buck变换器[2]。

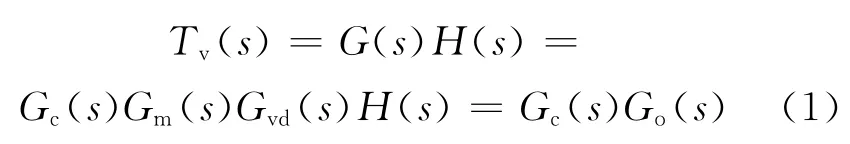

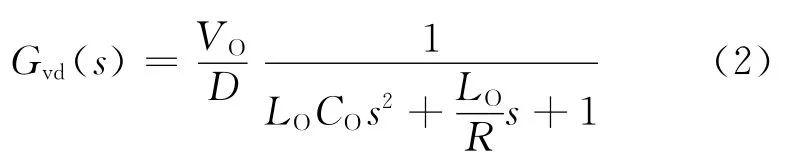

单相同步整流buck 变换器的回路增益函数为:

其中,Go(s)=Gm(s)Gvd(s),H(s)为未加补偿网络Gc(s)的回路增益函数,称为原始回路增益函数。Gm(s)是PWM 脉宽调制器的传递函数,等于调制器中锯齿波幅值Vm的倒数。Gvd(s)是输出电压对控制变量的传递函数,H(s)表示反馈分压网络的传递函数,等于1。

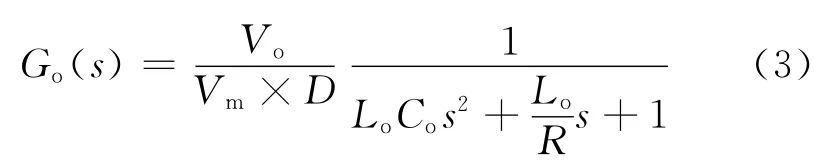

原始回路增益函数Go(s)为:

其中,VO表示输出电压,Vm是锯齿波幅值,D 是占空比,Lo是等效输出电感,Co为输出滤波电容。

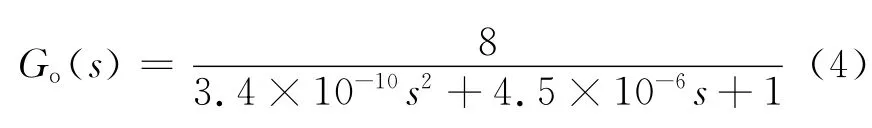

图4中,Vin=12V,Vout=1.1V,输出电流为100A,Lo1=Lo2=…=Lo6=300nH,输出滤波电容为8 200μF,开关频率为250KHz,负载电阻为11mΩ。根据这些参数可求出Go(s)为:

用MATLAB 软件绘制出Go(s)的Bode图,如图5所示。从图5中可以看出,相位裕度Pm只有5.29°,系统虽然是稳定的,但会有较大的超调量和调节时间。通常需选择相位裕度在45°左右,增益裕度Gm在10dB左右。

Figure 5 Bode plot of original loop gain图5 原始回路增益函数波特图

4.2 补偿网络设计

由于原始回路增益函数Go(s)不能满足DCDC变换器静态和动态特性的要求,因此需加入补偿网络Gc(s)。补偿网络只是变换器中一个很小的部分,但对变换器的静态和动态特性却非常重要,它会影响到DC-DC变换器的输出稳压精度、电压调整率、频带宽度以及瞬态响应[3]。

图6是C 型补偿网络电路,该补偿网络可以提供两个零点和三个极点来拓展回路增益的带宽和增加相位裕度。

Figure 6 Compensation network of C-type图6 C型补偿网络电路

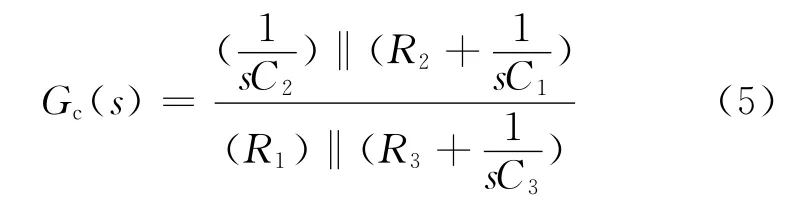

补偿网络的传递函数Gc(s)为:

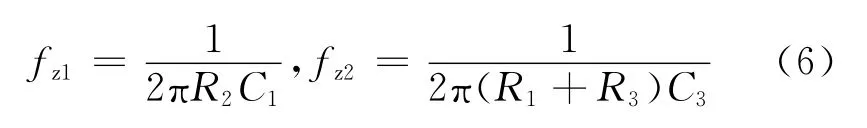

零点为:

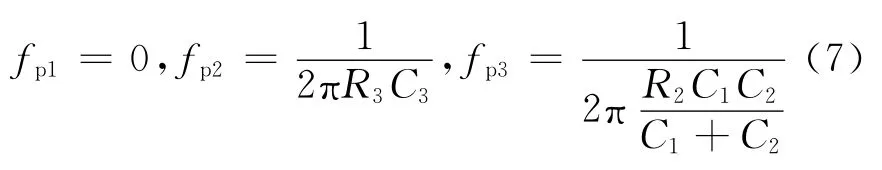

极点为:

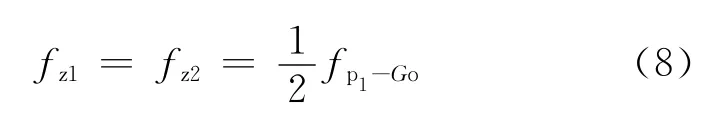

原始回路增益函数Go(s)有两个相近的极点fp1_Go=fp2_Go=8636Hz;补偿网络可以提供两个零点fz1、fz2和三个极点fp1、fp2、fp3。下面通过分析它们之间的关系来确定补偿网络的参数。

(1)首先选择补偿后的增益交越频率fg。fg理论上可设定为开关频率fs的1/2,但是实际上考虑抑制输出开关纹波,fg一般取为开关频率的1/5。

(2)原始回路增益函数有两个极点,可将补偿网络Gc(s)的两个零点设计为原始回路函数极点频率的1/2,即:

(3)原始回路函数没有零点,可将补偿网络的两个极点fp2、fp3设定为fp2=fp3=fs,以减小输出高频开关纹波。

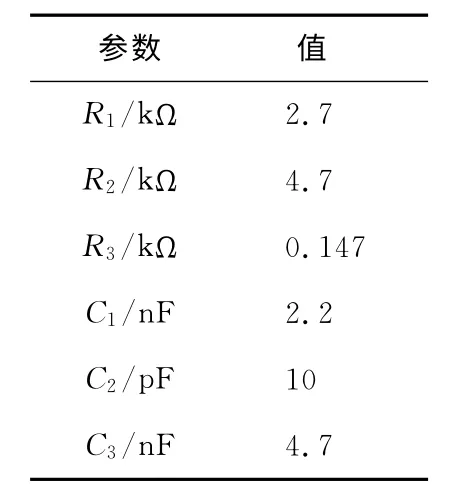

按照以上公式设计的补偿网络各补偿元件参数如表1所示。

Table 1 Parameters of compensation network表1 补偿网络各元件参数

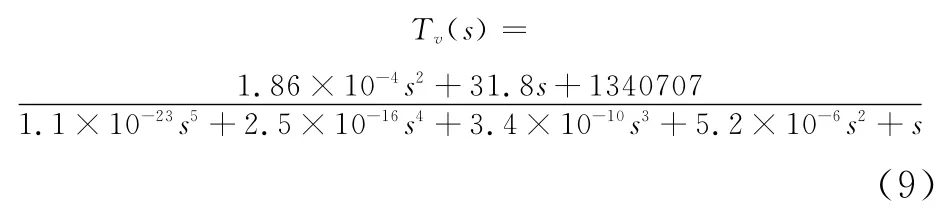

根据表1的参数可求出Gc(s),进而可求出回路增益函数Tv(s)为:

波特图如图7所示。从图7中可知,补偿后回路增益的相位裕度Pm在51.5°左右,增益裕度Gm为31.4dB左右,满足系统稳定性要求。

Figure 7 Bode plot of compensated loop gain图7 补偿后回路增益函数波特图

4.3 输出滤波器设计

输出滤波器电容的种类和电容值大小可以改变DC-DC 变换器从控制到输出的传递函数,从而对电路的稳定性产生不利的影响[4]。

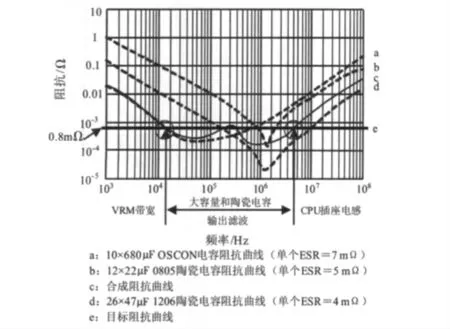

根据VRM11.1设计指导,处理器的目标阻抗为0.8mΩ,即必须保证在任何区段内电源的输出阻抗小于0.8mΩ,如图8中直线e所示。

Figure 8 Output impedance characteristic图8 输出阻抗曲线图

(1)低频段,即从0Hz到VRM 带宽的区段,阻抗由VRM 的反馈补偿回路来保证。VRM 带宽可设为大容量电容的阻抗开始小于目标阻抗时的频率。

(2)中频段,即VRM 带宽到处理器插座电感开始上升的区段,阻抗由大容量电容、陶瓷电容和印制板的寄生参数来确定。陶瓷电容的数量根据VRM11.1推荐的电容种类和数量进行放置。

(3)高频段,阻抗由处理器插座电感和处理器封装来控制。

对于VRM 来说,必须保证低频和中频的阻抗低于目标阻抗。

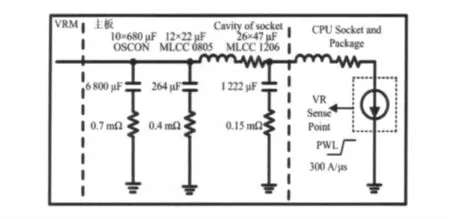

综合考虑输出阻抗、动态响应能力、电压超调、印制板层数等因素,输出滤波电容设计如图9 所示。

Figure 9 Output filter capacitors图9 输出滤波电容

图9 中,大容量电容由10 个680μF 的OSCON 电容并联,单个电容的串联等效电阻ESR 为7mΩ,总ESR 为0.7mΩ;高频电容为12个0805封装的22μF 陶瓷电容并联,单个电容的ESR 为5mΩ,总ESR 为0.4mΩ;另外还有26个1206封装的47μF陶瓷电容放在处理器插座中间,总ESR为0.15mΩ。

输出电容的阻抗曲线图如图8所示,曲线c为电容的合成阻抗曲线。从阻抗曲线中可以看出,在中频段,大容量电容、陶瓷电容的合成阻抗小于目标输出阻抗,满足设计要求。

5 实验结果

根据以上设计思路,采用ISL6336A 为控制芯片,设计了处理器电压调节模块。对电压调节模块的输出电压纹波、动态响应能力、电压调整率、负载调整率等技术指标进行了测量,结果完全满足处理器供电要求。图10所示分别为电压调节模块的输出电压纹波和动态响应波形。

Figure 10 Measured waveforms of voltage regulator module图10 实测电压调节模块波形

对计算主板上其它十几种电源的技术指标也进行了测量,结果完全满足主板供电要求。

该主板已经大量应用于“天河一号”等高性能计算机系统中,整机性能处于国际领先水平。

6 结束语

本文采用12V 母线直流分布式供电方式,成功地实现了某高性能计算机系统的电源。文中详细介绍了计算机柜和计算主板的电源设计框图、工作原理和加电/复位时序设计等,并重点介绍了主板中处理器电源的设计方法,对其中的回路增益、补偿网络、输出滤波器等参数设计给出了具体的计算公式。应用结果表明,该电源完全满足高性能计算机系统的供电要求。

[1]Intel.Voltage regulator module(VRM)and enterprise voltage regulator-down(EVRD)11.1design guidelines[EB/OL].[2009-08-01].http://www.intel.com/Assets/PDF/designguide/397898.pdf.

[2]Wong Pit-Leong.Performance improvements of multi-channel interleaving voltage regulator modules with integrated coupling inductors[D].Blacksburg:Virginia Tech,2008.

[3]Xu De-hong.Modeling and control of power electronics system[M].Beijing:China Machine Press,2006.(in Chinese)

[4]Brown M.Power supply cookbook[M].Translated by Xu De-hong,Shen Xu,Yang Cheng-lin,et al.Beijing:China Machine Press,2004.(in Chinese)

附中文参考文献:

[3]徐德鸿.电力电子系统建模与控制[M].北京:机械工业出版社,2006.

[4]Brown M.开关电源设计指南[M].徐德鸿,沈旭,杨成林,等译.北京:机械工业出版社,2004.