关于提高硬件电路设计质量和可靠性的一点思考

2013-05-09周英才杨光伦马振球北京全路通信信号研究设计院有限公司北京100073

周英才 杨光伦 马振球(北京全路通信信号研究设计院有限公司,北京 100073)

1 概述

硬件系统是保证整个系统正常工作的基础,尤其是安全相关的控制系统中的关键硬件。硬件工作过程中存在许多可能造成硬件失效的因素,如随机干扰、静电、雷电感应、温度因素、电子元件发生闩锁等。对于一个安全系统如列车控制系统,它的所有安全功能的安全性是以硬件的可靠性为基础的。一旦硬件失效,可能会造成严重的后果。因此硬件设计的过程需要全面考虑所有对硬件可靠性有重要影响的因素,本文从元器件选型、电路设计、硬件设计流程的角度提出了几点提高硬件可靠性的建议。

2 元器件选型

2.1 硬件系统可靠性

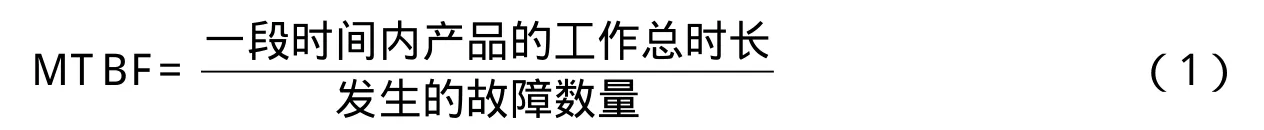

电子产品的可靠性通常用平均故障时间MTBF来表示:

要获得系统M TBF值,关键是要测出某段时闻内发生的故障数量,这通常需要做长时间的加速寿命实验,或对系统进行较长时间的故障跟踪记录。但这样做的最大问题是所需时间太长,对提高产品可靠性的直接指导作用有限。实际上,系统的MTBF值通常是通过下式计算:

式中λ为系统的失效率。

要想算出系统的M TBF,关键是求出系统的失效率。为了能简单有效对系统的失效率进行预计,人们提出了许多的计算方法,如:相似预计法、元器件计数法、应力分析法和简单枚举不完全归纳可靠性快速预计法等。

周英才,男,硕士毕业于北京理工大学,助理工程师,硬件开发工程师。主要研究方向为嵌入式硬件和底层软件,曾参与车载国产化深化研究项目。

相似预计法是利用以前使用过的相似电路的经验来对现有电路可靠性进行估计。其准确性取决于两个电路之间的相似性和等效性。其优点是简单快捷,缺点是需要有长时间的经验积累,可用性较差。

元器件计数法采用串联可靠性预计模型,把电路中所有用到的元器件的失效率进行简单累加。虽然不够精确但是计算简便,常用于早期的可靠性估计。其计算公式如下:

为第种元件的失效率式中:

λGS为设备总失效率,10-6/h;

Nik为第i中元器件的数量;

λGi为第i种元件的通用失效率;

πQi为第i种元件的通用质量系数;

n为系统的元件种类总数。

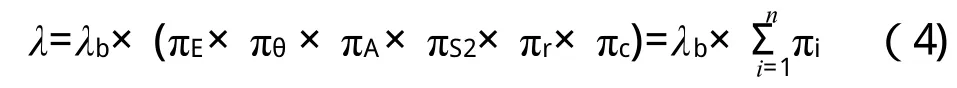

应力分析法通过分析元器件所受到的应力,根据失效模型计算该应力条件下元器件的失效率。应力分析法全面考虑了电、热、机械环境应力和质量等因素对元器件可靠性的影响。通过分析元件受到的电应力、热应力以及了解元件的质量等级,承受电应力、热应力的额定值,工艺参数和应用环境,预计电子设备的可靠性。其计算公式如下:

式中:λb为基本失效率;

πθ为质量系数,不同质量等级同类器件取值不同;

πE为环境系数,其数值取决于器件的种类和除温度外的环境类别;

πA为应用系数,指应用电路的影响因素,同一器件在不同的线路中使用时,取值不同;

πS2为电压应力系数,器件加不同电压时,取值不同;

πr为额定功率或额定电流系数,不同额定功率或电流的器件有不同的取值;

πc为结构系数,相同类型的单管、双管、复合管有不同的取值,此外还有πt(温度应力系数),πR(阻值系数),πCV(电容量系数),πL(成熟系数),πTAPS(引出端系数);πK(种类系数)等共37个π系数。

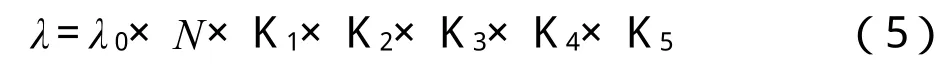

简单枚举不完全归纳可靠性快速预计法于20世纪80年代由王锡吉研究员提出,简称CW(Ch ina W ang)法。CW法经过大量实践验证,于1985年成为电子工业部标准(SJ2585-85)。CW法的计算公式如下:

式中:λ0为电子元器件的平均基本失效率;

K1为降额设计效果因子;

K2为老练筛选效果因子;

K3为环境影响因子;

K4为机械结构影响因子;

K5为制造工艺影响因子;

N为复杂因子;

2.2 元件失效率估计

从系统的可靠性计算过程来看,元器件的可靠性水平决定了系统可靠性。元器件的失效率一般可以通过官网站进行查询,或通过GJB-Z 299C-2006、M IL-HDBK-217F等标准手册进行估计。

有一些厂家只给出规定应力条件下的参数。但是元器件的失效率并不是一个常数,它与芯片工作时所受到各种应力的实际值密切相关。例如:电容的工作温度每上升10℃,它的失效率大致会增加50%。除此以外,元件所受的各种机械应力和电应力都会对可靠性造成影响。这时需要一定的方法对给定值进行修正。例如:某型号的铝电解其官方手册给出40℃时的基本失效率大约为5×10-6,假设实际的工作温度为55℃。通过查询手册可知铝电解电容的失效率计算公式为:

式中只有基本失效率λb与温度有关系,查询手册可计算得出55℃和40℃时基本失效率λb的比值约为1.8。通过对基本失效率进行修正可以得到55℃时该铝电解电容的失效率大约为9×10-6。除热应力外,基本失效率λb还与负载率等电应力因素有非常大的关系。式中πE为环境因子,它与应用环境的机械应力情况密切相关。

2.3 元器件选择

要实现某一个特定的功能,其可选的电路方案往往有多种。电路方案的不同,系统的可靠性可能会有很大的差别。合理的使用元器件,对于提高系统的可靠性非常重要。从提高电路可靠性的角度来看,元器件的选择除了电气参数需要满足要求以外,还需要注意以下问题:

1)尽量避免使用固有失效率高的器件。如光耦芯片等,尽可能用其他的类似功能的芯片替代。通过官方手册查询H CPL0630型光耦器件的手册可得到环境温度为40℃,置信概率为90%的失效率为9×10-8。而A DUM 1401型磁耦芯片在环境温度40℃时,置信概率为90%的失效率为0.21×10-9。磁耦芯片的可靠性比光耦芯片的可靠性要高出3个数量级,因此尽量用磁耦代替光耦。此外,电路中也尽量不要选用铝电解电容,可选择钽电容代替。

2)尽量不要使用分立元器件而要选择集成度较高的方案。集成度越高所使用的芯片的数量越少,虽然单个芯片的失效率会有所升高,但是整个方案的失效率往往会下降。

3 电路设计

单独依靠提升元器件的可靠性很难满足系统对硬件的可靠性要求。首先,元器件的可靠性水平越高成本也就越高。其次,某些元器件的固有失效率过高,往往会成为整个硬件电路的瓶颈。另外,硬件电路会受到各种干扰,而且经常遇到各种异常情况。因此要实现一个高可靠的硬件电路,必须要有合理的电路设计。硬件电路的可靠性涉及到的方面很广,现就主要的几点简单介绍。

3.1 降额设计

从元器件的可靠性预计计算过程可以知道,元器件的可靠性与它所受到的应力大小密切相关。所谓降额设计,就是为了提高可靠性而采取增加元器件在实际中使用时可能承受到的应力裕量。不同的元器件所要考虑的应力因素各不一样,通常要考虑的有:电压、电流、温度、电容的耐压及频率特性以及电阻的功率等。对电感的电流及频率特性,半导体器件的结电流、结温或扇出系数,电源的开关和主供电源线缆的耐压、电流和耐温性能,信号线缆的频率特性,还有散热器、接插件、模块电源等器件的使用要求进行降额设计。降额的幅度应根据实际情况而定,通常采用50%~70%的降额。

3.2 热设计

热设计是确保硬件可靠工作的重要一环。在硬件设计之初需要确定产品的运行环境温度指标,以及设备内部及关键元器件的温升限值。一般说来,元器件工作时的温度上升与环境温度没有关系,而工业级的元器件允许工作温度最高大多在85℃。为了保证在极限最高环境温度下元器件的工作温度还在其允许温度范围内并有相当的裕量,需要严格控制元器件的温升。在硬件单板设计时,首先要明确区分易发热器件和温度敏感器件(即随着温度的变化器件容易发生特性漂移、变形、流液、老化等),PCB板布局布线时对易发热器件采取散热措施,温度敏感器件与易发热器件和散热器隔开合适距离,必要时应进行热仿真分析。良好的热设计对于降低元件工作时的温度,提高系统的可靠性有很大帮助。

3.3 抗干扰和防护设计

外界环境对硬件电路的干扰总是无时无处不在。对于模拟电路,由于其对干扰信号非常敏感,比较容易被设计者发觉。而对于数字电路,由于它具有较强的抗干扰能力,只有当工作环境比较恶劣时才容易暴露出问题。因此数字电路必须经过专门的测试分析并采取合理的抗干扰措施。

1)屏蔽是所有抗干扰方法中最有效的一条途径。屏蔽可以有效切断干扰的传播途径,保护电路不受到干扰。屏蔽可以分为:电屏蔽、磁屏蔽和热屏蔽等。对复杂且工作频率很高或高频噪声分量较大的系统,或者对内部兼容性要求高的系统,层、框之间采用金属丝网或金属箱体进行屏蔽。使用屏蔽电缆的地方要把电缆的屏蔽层真正利用起来(与地或屏蔽壳体可靠连接)。

2)隔离是通过隔离器件将信号线两端的信号隔离开来,以防止干扰信号的传递。尤其是输入输出通道一般通过光耦、磁耦和变压器等隔离手段来防止外部干扰进入系统内部。

3)滤波是有效的抑制噪声的一种途径。各级电源的输入、输出端都要尽可能使用合适的滤波电路。尽可能同时滤除差模噪声和共模噪声,噪声泄放地与工作地特别是信号地要分开,考虑使用保护地;集成电路的电源输入端要布置去耦电容,以提高抗干扰能力。

硬件电路工作时经常会出现一些异常情况,如果不采取合理的防护,系统将变得十分脆弱。常规防护主要包括:电浪涌、电快速脉冲群、静电等。

电浪涌防护是针对雷电感应而采取的防护措施,一般是针对系统与外部的接口。常用的防护器件有:空气放电管、压敏电阻、TVS管,根据防护等级的不同可以采取多级防护措施。电快速脉冲群的防护与电浪涌的防护类似,它的强度较电浪涌弱但频率较高。

静电防护是需要认真考虑的一点。硬件电路板在生产、运输和实际使用过程中,都有可能会受到静电的威胁。静电损伤是一种软损伤,电路板受到损伤后并不立即暴露出问题。它具有较强的隐蔽性,这很可能会埋下隐患。静电防护设计要求:1)避免使用静电敏感器件,选用器件的静电敏感度一般不低于2 k V,否则要仔细推敲、设计抗静电的方法;2)暴露在外的器件或是能被手触及到的地方,其静电防护等级要满足相应标准的要求;3)在结构方面,要实现良好的地气连接及采取必要的绝缘或屏蔽措施,提高整机的抗静电能力。

3.4 冗余设计

对于系统的关键功能或者可靠性达不到要求的电路可以采用冗余设计来提高可靠性。冗余设计根据并联层次的不同可以分为元件级冗余设计、模块级冗余设计和系统级冗余设计,设计时可根据需求灵活选择。例如某系统由于现场环境非常恶劣,CAN通信经常受到干扰。为了提高可靠性,该系统的CAN总线通信采用双路冗余办法。在M VB中为了提高可靠性,物理介质可选择使用双路冗余的方案。在许多的系统中,接插件往往是一个不可靠的因素,对于关键信号一般采用多个触点冗余的办法。

4 设计流程

硬件电路所涉及到的知识面错综复杂,要真正的深入了解它需要非常深厚的专业知识,有一些甚至是学科前沿知识,所以很多时候硬件设计并不能很好的靠理论知识来解决。硬件设计人员要完全掌握所有的知识难度很大,尤其是经验尚浅的工程师。这时经验的积累显得十分重要,通过下面几种方法可以快速的积累经验避免走弯路。

1)建立公共的通用基础模块库。对于一般的数字电路一般都会包含:电源电路、时钟电路和复位电路,对通信端口一般都会进行防护设计。完全可以把这些公共的电路模块的典型设计加入到公司的库里。这对公司来说也是一笔无形的财富。另一方面,一个公司的产品往往具有很强的相似性,其电路结构也具有很多相似性。这一部分电路也可以通过综合总结加入到模块库中,以减少重复性的劳动并提高设计质量。

2)关键的新型硬件电路设计通过评审小组进行评审。一个公司的硬件方面的人才可能会有很多,但是必然有一些人在平均水准之下。只有通过评审严格把关,才能够保障产品质量的一致性。由于个人的精力始终是有限的,设计过程中难免会有所疏忽。此外每个人的设计经验也不同,可能设计者并不是对每一部分的电路都是十分精通。通过评审既能够有效的发现问题,对于提高设计人员的设计经验也非常有帮助。

5 总结

本文首先介绍了硬件电路可靠性在列控设备上的重要性,然后根据系统可靠性的计算方法,针对提高电路的可靠性从元件质量和电路的设计质量两个方面提出几点见解。最后从设计流程角度对如何提高硬件可靠性设计水平提出个人的一点思考。上述思考和建议对于硬件可靠性设计具有较强的参考和借鉴意义。

[1]郭荣佐, 黄君.嵌入式实时控制系统硬件可靠性及应用研究[J]. 电子技术应用, 2012,38(5):11-14.

[2]蓝志洋, 黄明华.嵌入式系统硬件可靠性和抗干扰性技术[J].电子技术应用, 2005, 28(14):51-53.

[3] EN50126:1999 Railway applications -The specification anddemonstration ofReliability, Availability,Maintainability andSafety (RAMS)[S].Brussels: European Committee for Electrotechnical Standardization, 1999.

[4] Electric railway equipment Train bus Part 1: Train communication network[S]. Switzerland: International Electrotechnical Commission, 2007..

[5] EN50129:2003 Railway applications-Communication,signalling and processing systems-Safety relatedelectronic systems for signalling[S].Brussels:European Committee for Electrotechnical Standardization, 2003.

[6] GJB/Z 299C-2006电子设备可靠性预计手册[S]. 北京: 中国人民解放军总装备部,2006.

[7] GB/T 24338.4-2009 轨道交通电磁兼容第3-2部分:机车车辆设备[S]. 北京: 中国国家标准化管理委员会,2009.