基于SOPC的惯导组件多模式数据采集系统研究

2013-05-03张志文

张志文,刘 斌

(西安工业大学电子信息工程学院,陕西 西安 710032)

0 引 言

惯导组件一般是由陀螺仪和加速度计组合而成[1]。有的惯导组件直接输出脉冲信号,有的则是通过串行总线接口输出数字信号。对于惯导组件的标定,一般是将其固定在三轴转台上,通过在不同的温度下改变转台的位置和速率,由检测系统对其输出的脉冲信号或串口数字信号进行测量,再对测量值进行相应的数学处理,从而得到惯导组件的性能参数。由于惯导组件的参数对温度非常敏感,所以需要在多个温度点下对其进行标定。而每个温度点需要保温4h后才能进行测量,因而完成一个产品的标定一般需要3d左右。国外采集方法一般是通过PCI卡来实现数据的采集,该方法对计算机要求较高,需要计算机有较多的PCI卡槽,且不适合野外作业[1]。国内一般是通过PFGA和CY7C68013-128AC的USB来实现12路的脉冲信号采集[1],由于该USB内置的是8位的51内核,大大降低了USB的传输速度。对于串口的数据采集,一般的MCU都很少能拥有4个串口,所以一般需要通过两个MCU来完成[2],这样不但增加了电路的复杂性,还降低了系统的可靠性。针对这种情况,本文提出了一种基于SOPC的设计方案[3-4],通过使用FPGA的32位的高速NIOS软核,对脉冲信号或串口数据进行采集,再通过USB总线把采集的数据发送到PC机上。

1 设计原理

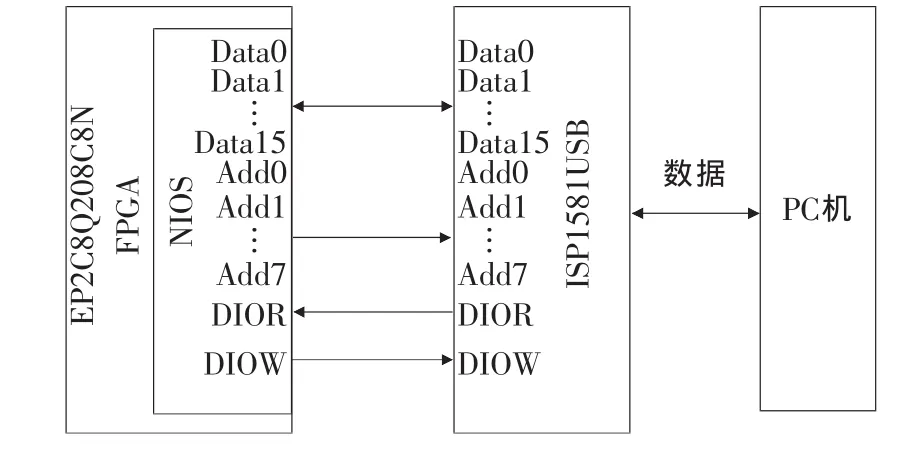

本系统使用SOPC的设计方案,通过Verilog语言对24路脉冲计数模块进行设计,实现对24路脉冲信号的计数,再调用SOPC Builder里的4个UART核实现同时对4路串口数据的接收。并通过在SOPC中添加NIOS软核,实现对脉冲计数模块和串口数据接收模块的控制,将接收到的数据通过高速USB ISP1581发送到PC机,由PC机对接收到的数据进行处理,采集系统框图如图1所示。

图1 数据采集系统框图

在图1中,脉冲信号的计数是NIOS软核每隔5ms向24路计数模块发送相应的地址,获得24路脉冲计数模块的计数值,再通过USB总线把数据发送到PC机上。而串口数据则是通过NIOS,对UART核进行设置,确定其中断优先级和波特率,然后通过中断方式接收串口数据,再通过USB总线发送到PC机。

该测试系统是由下位机和上位机两个部分构成。下位机由FPGA和USB接口电路组成,实现对脉冲信号的计数和串口数据的接收。而上位机是装有Windows XP系统的PC机,通过VC++6.0的程序设计,对接收到的数据进行实时地处理、显示和保存。

2 SOPC系统设计

2.1 24路脉冲计数模块设计

本设计使用的FPGA芯片是ATMEL公司的EP2C8Q208C8N,它拥有非常丰富的逻辑单元,可以满足设计内核的需要。而且这款芯片内部还拥有两个锁相环,最高频率可达250MHz,使得数据处理速度更快。

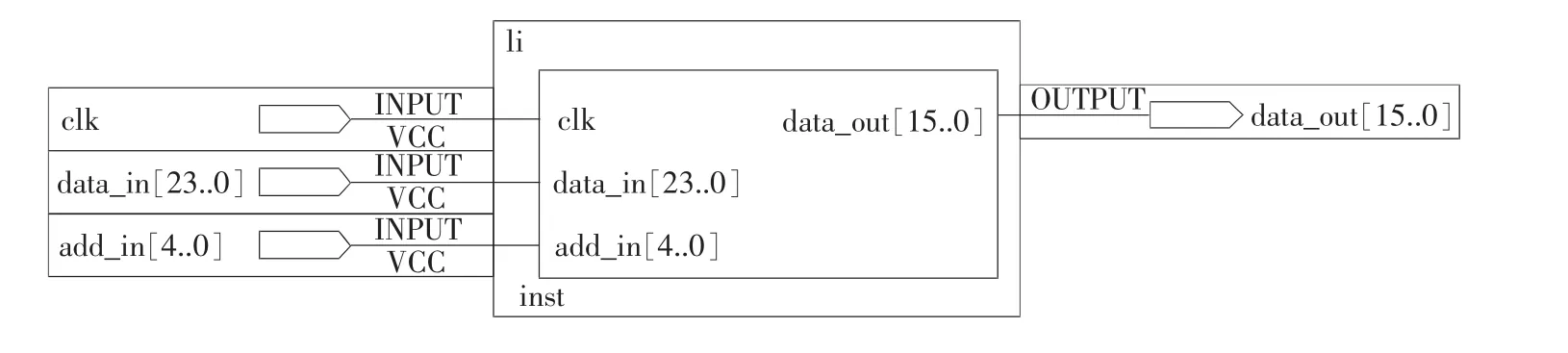

开发平台使用了Quartus II 9.0,相比MAXPLUS II的开发平台,Quartus II 9.0的开发界面更加人性化,支持的芯片也更加丰富,最重要的是它增添SOPC builder,使得软核的开发得到了应用。该系统的24路脉冲计数模块设计是通过使用Verilog语言实现的,可以对惯导组件输出的信号分别计数,如图2所示。该模块data_in[23..0]是24路惯导组件的脉冲输入,add_in[4..0]是每个脉冲输入通道的地址,data_out[15..0]是计数单元的计数值输出。

2.2 4路串口数据接收电路设计

串口数据接收电路的设计,是通过在SOPC Builder里添加UART软核实现的。在SOPC Builder里有很多的软核可以调用,由于该设计需要4个串口同时对4个惯导组件输出的4路串口数据进行接收,而一般的处理器很少拥有4个串口。虽然有很多串口扩展芯片可以对串口进行扩展,但需要在外部对电路进行扩展,不利于系统的可靠和稳定工作,而且提高了系统的成本。SOPC Builder可以很好地解决这个问题,它是在FPGA内部完成串口的设计,只需要调用软核就可以完成4个串口的拓展。电平转电路使用MAX490,其作用是把422电平转换为UART的TTL电平。为解决4路串口数据同时接收的问题,本系统对4个串口的中断优先级进行了设置,串口1的中断优先级最高,并依次降低。UART通过中断方式对字节进行接收。当接收到完整的一帧数据,再由NIOS对不同串口的数据添加不同的帧头,并写入到USB缓冲区中。待数据缓冲区存满后,通过USB总线发送到PC机上。由于每路数据添加有不同的帧头,所以PC机能够识别不同串口的数据,并进行处理。

2.3 USB数据传输电路设计

使用飞利浦公司的ISP1581USB作为USB接口电路。它是一款价格低,功能强大的通用串行总线(USB)接口器件,符合USB2.0规范,并且兼容USB1.1规范,具有高速的USB通信能力。其内部集成了串行接口引擎(SIE)、PIE、8 kB的多结构FIFO存储器和数据接发器。拥有7个IN端点,7个OUT端点和1个固定的控制IN/OUT端点。端点的双缓冲配置增加了数据吞吐量,实现了实时数据的高速传输[5~6]。

图2 24路脉冲计数逻辑电路图

图3是USB数据传输电路设计原理图,由NIOS对USB芯片进行读写操作,完成USB的枚举和控制。由于该设计使用的USB芯片没有其公司提供的通用驱动,还需要对驱动程序进行开发。本设计使用VC++6.0、DDK和Driver Studio对驱动程序进行开发,与传统使用VC++6.0和DDK对驱动进行开发相比,开发难度大大降低,减少了开发时间,提高了开发效率。

图3 USB数据传输设计电路原理图

2.4 NIOS软核设计

NIOS软核是本设计的核心,下位机所有的功能都是由NIOS软核来控制的。NIOS软核是一个32位的嵌入式微处理器,其性能超过了200DMI/s。而且支持多CPU的SOPC设计,使得设计的方法更加灵活。

本系统使用NIOS控制的模块有24路脉冲计数模块和4路串口数据接收模块,以及USB数据传输模块。工作时需要对各个模块进行初始化,然后通过接收PC机发送的模式选择命令,来接收脉冲数据或者串口数据,把接收到的数据保存到相应的缓存区里。再通过对USB进行控制,设置USB包的大小和批次,把数据发送到PC机,进行处理、保存和显示。

3 系统软件设计

系统软件设计主要由SOPC下位机程序设计和WindowsXP环境下的上位机应用程序设计两个部分组成。FPGA的SOPC主要作用是:系统上电后,FPGA通过SOPC里的各个软核相互协作,把24路脉冲数据或者4路串口数据通过USB总线传输到上位机。上位机应用程序的设计是应用VC++6.0提供的WIN32 API函数,把下位机通过USB发送数据包传递到上位机。在WinsowsXP环境下利用MFC来设计程序界面,实现上位机实时对下位机传输的数据进行处理、保存和显示。

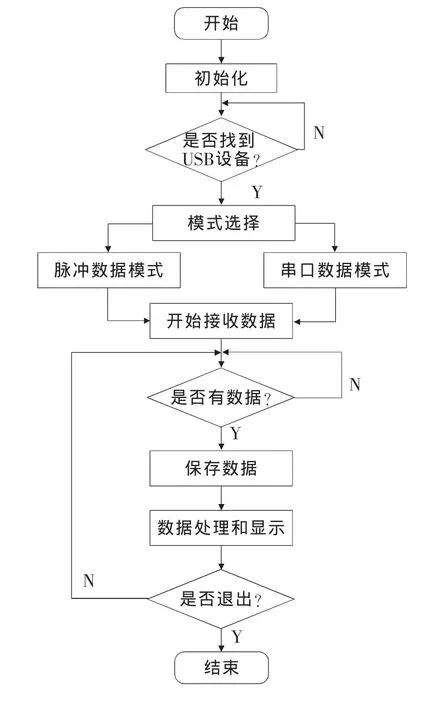

3.1 SOPC的程序设计

图4是SOPC的程序设计流程图。首先,对所有的模块进行初始化,包括对NIOS的I/O方向寄存器进行初始化。其次,对USB进行枚举,如果枚举成功,等待接收上位机的模式选择命令,如果是串口数据模式,则对串口的波特率和中断优先级进行初始化,然后对USB的数据包的大小进行设置。如果是脉冲数据模式,则对定时器进行设置,每5ms对计数模块进行数据的读取,设置USB的包大小。设置完成后,下位机就开始等待数据。如果有数据,就开始接收数据,把接收的数据进行相应的处理,并通过USB总线发送到PC机。

图4 SOPC的程序设计流程图

图5 应用程序开发流程图

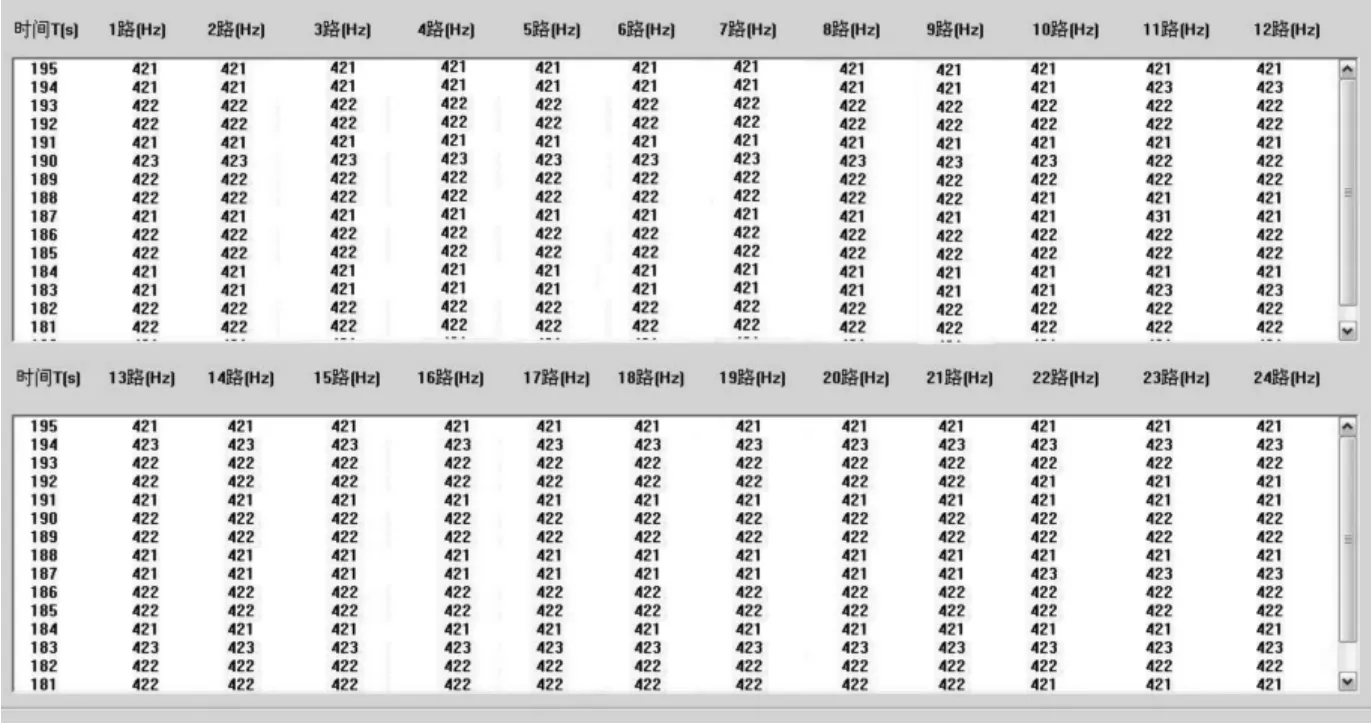

图6 24路脉冲数据测量结果

图7 4路串口数据测量结果

3.2 应用程序设计

本设计采用VC++6.0的MFC来设计应用程序,通过MFC的编程设计用户界面,再通过WIN32 API函数来读取USB驱动程序里的数据[7~8],并对所接收的数据进行实时处理,应用程序的开发流程如图5所示。首先,对所有的函数类进行初始化,并对USB的设备进行查找,通过查找USB的GUID,来获得需要的设备。然后,再选择接收对应模式下的数据,等待数据的到来。当数据到来,开始读取存储在USB驱动里的数据包,把读取到的数据进行处理和保存,最后,把处理好的数据进行实时的显示。

4 实验结果

对系统脉冲计数模式测量时,使用SP1641D信号发生器作为脉冲信号源,当信号源输出信号为422 Hz方波信号时,测量结果如图6所示。通过实验验证,本系统能够满足对两个惯导组件的24路脉冲信号的无缝计数要求。由于实验室条件所限,SP1641D信号发生器带负载能力有限,导致系统有1个脉冲计数的偏差。对单路测试时,实验结果没有出现误差。通过实验证明,该系统的误差率在1.0×10-7内。对系统串口数据模式测量时,使用专用的422串口数字信号发生源,测量的结果如图7所示。由于使用了专用的信号源,没有出现误差,能够准确地接收数据,通过实验验证,本系统也能够满足对4个惯导组件的4路串口数据接收的设计要求。

5 结束语

基于SOPC的惯导组件多模式测量系统,既解决了24路脉冲信号的计数,又解决了4路串口的数据接收,实现了多模式的测量需求。由于大部分的设计都是在FPGA芯片内部完成的,提高了系统的稳定性和抗干扰能力,且同时降低了系统的成本。该设计完全满足惯导系统的标定,通过大量的实验证明,其可以作为惯导组件的新型测量设备。

[1]张志文,赵浩.惯导组件的脉冲输出测控系统[J].西安:西安工业大学学报,2009,29(5):461.

[2]张志文,刘美飞,李剑.基于USB的多串口测试系统软件设计[J].西安:西安工业大学学报,2012,5(32):400-405.

[3]夏宇闻.Verilog数字系统设计教程[M].2版.北京:北京航空航天大学出版社,2008:5-7.

[4]李兰英.Nios II嵌入式软核SOPC设计原理及应用[J].北京:北京航空航天大学出版社,2006(11):1-20.

[5]Axelson J.USB mass storage designing and programming devices and embedded hosts[M].Lakeview Research,2006(6):200-240.

[6]薛圆圆.USB应用开发技术大全[M].北京:人民邮电出版社,2011(1):161-181.

[7]Microsoft Corp.Microsoft visual C++6.0 MFC library refer-ence[M].Microsoft Press,2007.

[8]孙鑫,余安萍.VC++深入详解[M].北京:电子工业出版社,2006.