一种基于AD9854的BPSK信号产生设计

2013-04-25裴少俊胥嘉佳黄克平

裴少俊,胥嘉佳,黄克平

(1.南京模拟技术研究所 科技处,江苏 南京210016;2.南京模拟技术研究所 科研处,江苏 南京210016)

当前通信系统的软、硬件日趋模块化、标准化和通用化,其主要功能由软件确定并完成,工作参数具有可编程特性,软件无线电技术已成为通信系统的主要设计平台[1]。

在通信系统中,需要将基带通信信号通过中频混频器调制为中频信号,之后通过射频混频、滤波以及放大等工作将信号调制为射频信号,并通过天线以电磁波的形式发射出去。在采用软件无线电技术处理通信信号时,常用数字混频加DAC来实现基带信号到中频信号的调制。中频信号的频率约为70 MHz,信号带宽一般<10 MHz,根据采样定理,DAC时钟至少设置在150 MHz。在软件设计时,需要考虑高速数字上变频的实现,采用中、低档次的数字器件将数字信号的工作时钟调到150 MHz以上也存在一定难度;在硬件设计时,在电路PCB上设计150 MHz数据传输线,需要考虑数据线的信号差分特性、微波衰减特性以及电磁兼容特性,并当DAC的位数较高时,数据线的走线问题相当复杂。

由于通信系统中采用的数据调制方式多为FSK,BPSK,AM等方式,而ADI公司的DDS芯片AD9854能够对基带信号直接进行常用调制,因此与数字混频加DAC的传统解决方案相比,采用AD9854处理中频信号混频的问题具有优势。

1 AD9854简介及其应用

直接数字式频率合成技术(Direct Digital Synthesis,DDS)采用全数字技术,基于相位的线性性质以及相位与幅度的对应关系实现频率合成,是一种新的频率合成方法[2]。AD9854是ADI公司推出的一款高性能DDS芯片[3-4],系统时钟频率最高为300 MHz,可以工作于FSK,BPSK,AM等常用的调制方式,包含两个集成12位DAC,一个超高速比较器、4~20倍可编程参考时钟倍频器、两个48位可编程频率寄存器、两个14位可编程相位偏置寄存器,并具有12位幅度调制和可编程功能。它采用0.35μmCMOS工艺,可以产生输出频率高达150 MHz的同步正交信号,每秒能够产生百万新频率。输出的正弦信号经过滤波后,可以再通过内部比较器转化为方波。其内部的幅度、频率、相位寄存器,可以对输出信号的幅度、频率和相位进行控制。

由于AD9854支持BPSK方式,因此可以用它作为BPSK信号的混频器使用。当配置成BPSK工作方式时,只需要给AD9854输入基带BPSK信号,就可以输出所需频点的中频调制信号。由于控制信号和输入的基带信号均为低频信号,其硬件设计比采用DAC大为简化,而软件设计部分也因为绕开了高速的数字上变频工作而得到相应的简化。

2 用FPGA控制AD9854产生BPSK信号

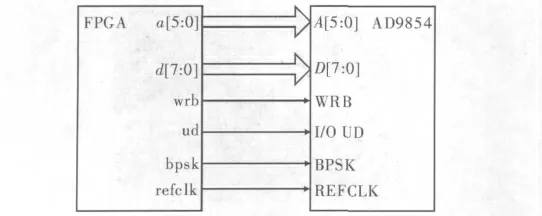

对AD9854进行控制,首先搭建硬件电路。将AD9854的S/P Select管脚拉高,则AD9854工作于并行配置方式,它与FPGA的硬件连接示意图如图1所示。图中管脚的解释如下:A[5∶0]是6位并行编程地址总线输入;D[7∶0]是8位并行编程数据总线输入;WRB是将并行数据写入寄存器的控制信号输入;I/O UD是双向频率更新信号,如果设置为输入,那么AD9854将在I/O UD上升沿时刻刷新,并按寄存器中的设置工作;BPSK为相位选择信号输入,也就是BPSK基带信号输入,输入‘0’时芯片输出选择1号相位,输入‘1’时芯片输出选择2号相位;REFCLK是外部参考时钟输入,从软件无线电的角度考虑,选择用FPGA控制输出该时钟信号,以达到中频频率软件可调的要求。

图1 FPGA与AD9854的硬件连接示意图

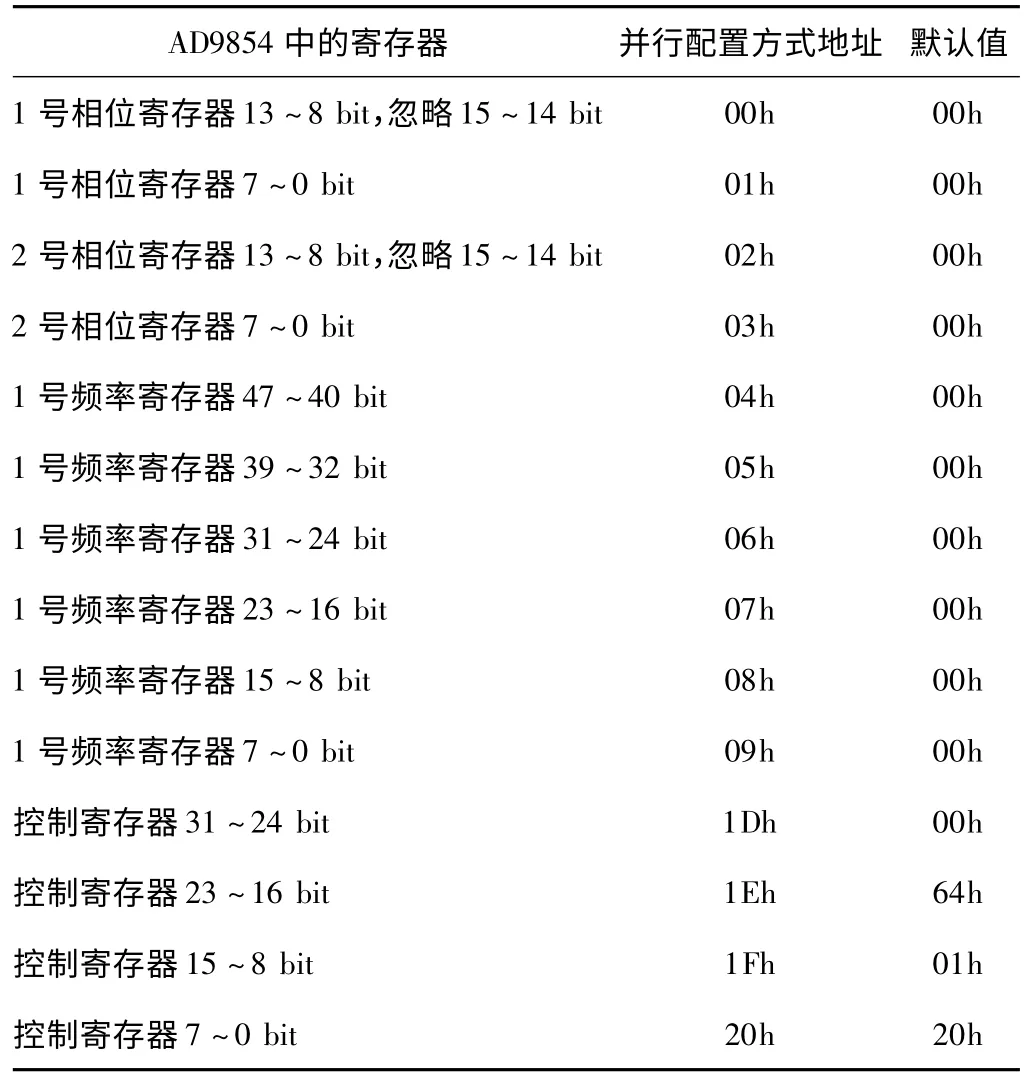

硬件电路搭建完毕之后,需要考虑AD9854中寄存器的配置问题。当AD9854工作于BPSK方式时,需要配置的寄存器如表1所示。

表1 AD9854工作于BPSK模式下需要配置的寄存器

相位寄存器配置值的计算公式为(φ/2π)×214,其中φ为需要配置的相位值,对于BPSK信号,一般1号相位寄存器表示的相位值与2号相位寄存器表示的相位值相差π。频率寄存器配置值的计算公式为(f/fs)×248,其中,f是需要输出的BPSK载频,即中频频率;fs为系统时钟频率,它由从REFCLK得到的外部参考时钟频率经可编程参考时钟倍频器倍频后得到。需要考虑的控制寄存器各比特定义和配置值如表2所示。

表2 需要考虑的控制寄存器各比特位的意义

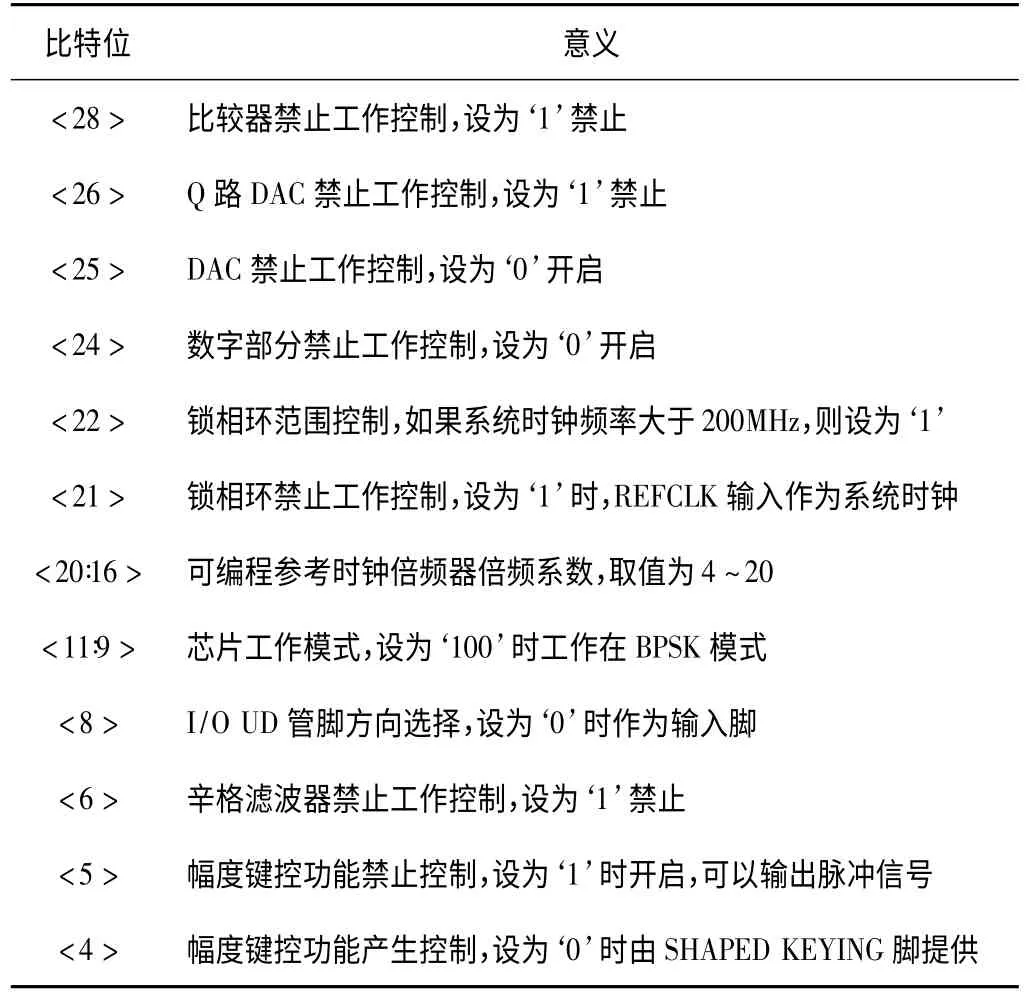

AD9854工作于并行配置方式下的写时序,如图2所示,图中最大时延TWRHIGH为7 ns,在编写程序时需要注意时延量。

图2 并行配置方式下AD9854的写时序

最后的控制步骤就是编写软件,用FPGA对AD9854进行控制可以通过状态机的方式实现。

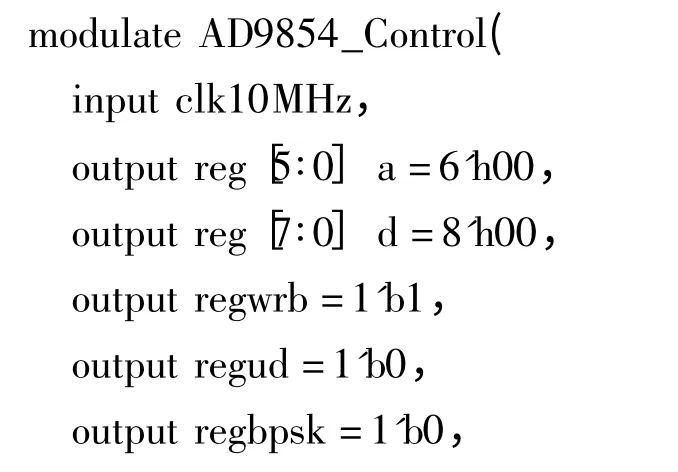

(1)采用Verilog HDL语言定义FPGA的管脚如下

(2)给出refclk的频率为10 MHz

assign refclk=clk10MHz;

(3)用状态机的方式配置AD9854内部的寄存器,使之工作于需要的BPSK参数方式,配置流程如图3所示。

图3 FPGA对AD9854的配置流程图

图3中,“*”表示对AD9854进行写入操作,就是将wrb脚置低,再置高。这时AD9854的系统时钟设置为140 MHz,而波形频率设置为系统时钟的1/2,也就是70 MHz。从BPSK管脚输出一个码速率设置为9.6 MHz的0、1码流,即得到需要的载波频率70 MHz的BPSK信号。

3 实验结果

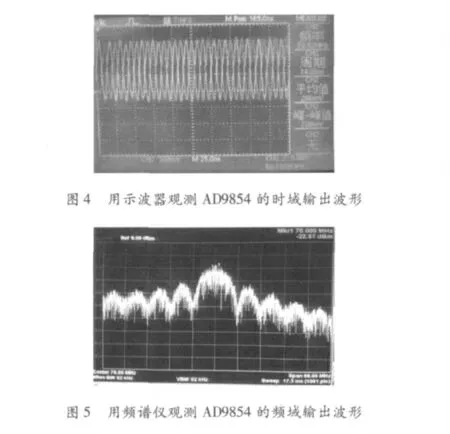

用示波器和频谱仪分别观测AD9854芯片的输出,如图4和图5所示。

由于BPSK信号的相位差为π,因此其码元‘0’和‘1’所对应的信号相位完全取反,从图3所示的示波器观测图可以看出,AD9854的输出波形由相位完全相反的两组正弦波在时域相互叠加,形成了眼图的效果,眼图匀称,说明BPSK信号的输出稳定,无抖动。从图4所示的频谱仪观测图可以看出,AD9854的输出信号载频为70 MHz,观测带宽(Span)设为96 MHz,因此可以看出信号的主瓣宽度为19.2 MHz,副瓣宽度为9.6 MHz,说明BPSK信号的码速率为9.6 MHz,这与软件设计中的参数完全一致。

4 结束语

文中利用FPGA对AD9854进行控制,产生了BPSK信号,并给出了软、硬件设计方法,实验结果证明了设计的正确性,为通信系统中的中频处理提供了一个有效的方法。

[1] 粟欣,许希斌.软件无线电原理与技术[M].北京:人民邮电出版社,2010.

[2] 徐丹燕,甘志银,梁观平,等.16位单片机对AD9854控制的实现[J].计算机与数字工程,2007,35(3):182-184,189.

[3] 张玉梅,陈健,傅丰林.用DSP控制AD9854实现跳频通信[J].世界电子元器件,2003(9):64-65.

[4] 詹艳艳.基于DDS的波形信号发生器的设计[J].沈阳理工大学学报,2008,27(3):52-56.