基于DDS的多功能高精密信号发生器设计

2013-04-25林冲锋梁龙学索云天

林冲锋,梁龙学,索云天

(兰州交通大学 电子与信息工程学院,甘肃 兰州730070)

随着科学技术的不断进步,人们对相应的测试仪器和测试手段也提出了更高的要求,传统的信号发生器大多由模拟或数字电路构成,其可编程性、精度以及稳定度等性能已经无法满足人们对高精密高稳定度信号发生器的要求。因此,设计新型的多功能高精密信号发生器具有一定的意义。设计采用新型DDS芯片AD9854和单片机ATmega32构成信号发生器的核心部分,通过上位机设置信号参数,可输出高频率分辨率的正弦波、方波以及FSK、ASK等多种波形,并且具有成本低、体积小等优点。

1 DDS及AD9854简介

1971年,美国学者J.Tierney等人在其撰写的《A Digital Frequency Synthesizer》一文中首次提到了直接数字频率合成(DDS)的概念[1]。但是,限于当时的技术和器件水平,其性能指标尚不能与已有的技术相比,故未受到重视。近年来,随着微电子技术的迅速发展,直接数字频率合成技术得到了飞速的发展,以有别于其它频率合成方法的优越性能和特点,广泛应用于现代频率合成技术中。其优点和特点具体体现在相对带宽大、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有较高的性价比。DDS技术现已广泛应用于通讯、导航、雷达、遥控遥测、电子对抗以及现代化的仪器仪表工业等领域。

DDS是根据正弦函数的产生,从相位出发,由不同的相位给出不同的电压幅度,即相位-正弦幅度变换,最后滤波,平滑输出所需要的频率。其基本结构如图1所示。

图1 DDS的基本结构

相位累加器在每一个时钟脉冲内,与频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,就可以把存储在波形存储器内的波形抽样值经查找表查出,完成相位到幅值转换[2]。波形存储器的输出送到D/A转换器,D/A转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。低通滤波器用于滤除不需要的取样分量,以输出频谱纯净的波形。输出频率f0表示为

其中,K为频率控制字;fc为系统时钟,由外部参考时钟经过内部倍频后得到。最终的输出频率是由频率控制字、时钟和相位累加器位数共同决定的。

AD9854是ADI公司推出的一款DDS芯片。它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号[3]。AD9854[4]的DDS核具有48位的频率分辨率,在300 MHz系统时钟下,由式(1)可以得出其频率分辨率可达1μHz;由奈奎斯特采样定理得,允许输出的最高频率为150 MHz。

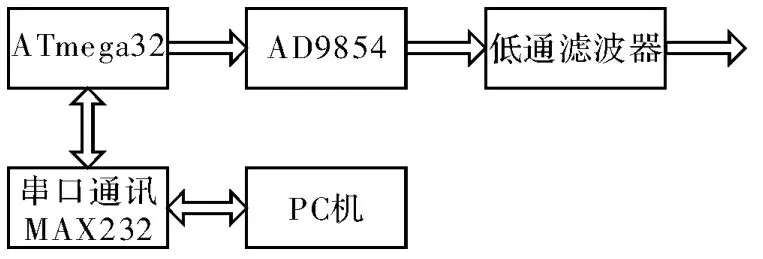

2 系统总体结构设计

系统由单片机ATmega32、AD9854、串口通讯电路、上位机以及低通滤波器组成。单片机通过串行方式与AD9854连接,同时通过MAX232串行通信接口接上位机。由上位机软件设置波形参数,并将信息发送给单片机,单片机根据接收到的信息,控制AD9854输出相应的波形。由于AD9854内部不含低通滤波器,因此需要在其末端加上低通滤波器,滤除高频分量。系统整体结构如图2所示。

图2 系统整体结构图

3 系统硬件设计

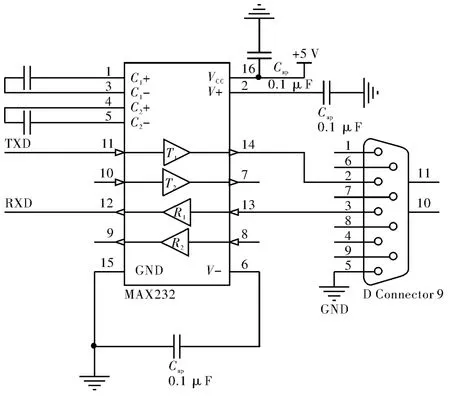

3.1 串口通讯电路设计

RS-232是目前常用的串行接口标准,用于计算机与计算机之间,计算机与外设之间的数据通信。由于RS-232电路电平与TTL电平不同,因此RS232驱动器与TTL电平连接时必须经过电平转换,系统采用Maxim公司的MAX232来完成这一功能。MAX232芯片包含两路接收器和驱动器,内部有一个电源电压转换器,可以把输入的+5 V电压变换为RS-232输出电平所需的-10~+10 V电压。因此,采用此芯片接口,串行通信系统只需单一的+5 V电源即可。串口通讯接口电路连接如图3所示。

图3 串口通讯接口电路

ATmega32有一个全双工的串行通讯口,可以通过MAX232与PC进行交互。采用三线制连接串口,即9针串口只连接其中的3根线:第2脚的IN与MAX232的T1OUT(PIN14)连接,第3脚的OUT与MAX232的R1IN(PIN13)连接,第5脚的GND接地。MAX232的T1IN引脚(PIN11)和单片机ATmega32的TXD引脚(PIN15)连接。R1OUT引脚(PIN12)和ATmega32的RXD引脚(PIN14)连接。MAX232的其它引脚连接法如下:V-引脚(PIN6)与GND引脚(PIN15)接地,V+引脚(PIN2)与VCC引脚(PIN16)接+5 V电源,其中VCC,V+,V-对地加0.1μF的去耦电容,目的是提高抗干扰能力。

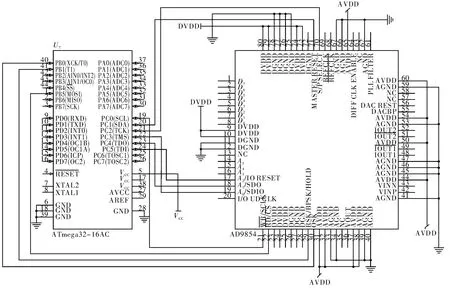

3.2 单片机与AD9854接口电路

ATmega32是具有32 kB系统内可编程Flash的8位AVR微控制器,采用先进的RISC结构,具有32个可编程I/O口。文中采用串行方式与AD9854通信,完成对AD9854的控制。接口电路如图4所示。

串行传输时,AD9854主要引脚定义如下:MASTER RESET为芯片复位端;I/O RESET为串行通信的复位端;SDO为串行数据输出口(3线模式);SDIO为串行数据输入口(3线模式);I/O UD为频率更新端口;WRB/SCLK为串行模式时钟信号输入端;RDB/CSB作为串行模式片选端;FSK/BPSK/HOLD为多功能复用引脚,用来选择芯片的工作模式;OSK在编程操作时可用来控制幅度与时间斜率;REFCLK为单端时钟信号输入端。

3.3 滤波器的设计

因为AD9854内部不含低通滤波器,所以在信号输出端需要增加一个滤波器。考虑到AD9854的输出信号受参考时钟及器件本身噪声等因素的影响,高端散杂噪声干扰较大,而椭圆函数低通滤波器具有较窄的过渡带特性,且7阶滤波具有更高下降速度的过滤带,可以有效地滤除高频干扰,因此,设计选用7阶椭圆函数滤波器作为低通滤波器。电路如图5所示。

图4 ATmega32和AD9854的接口电路图

图5 7阶椭圆函数滤波器

4 系统软件设计

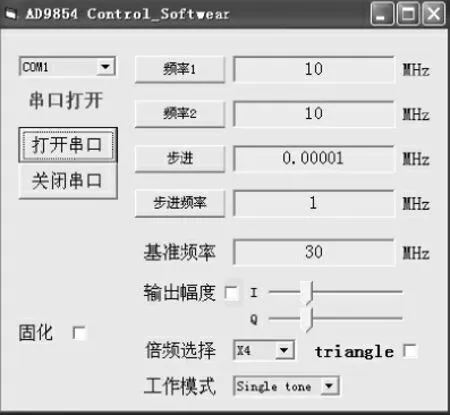

软件设计包括Windows系统下的上位机控制台软件设计和单片机程序设计两部分。控制台软件使用VB语言编写,控制台软件AD9854 Contror_Softwear的操作界面如图6所示。

图6 AD9854 Contror_Softwear的操作界面

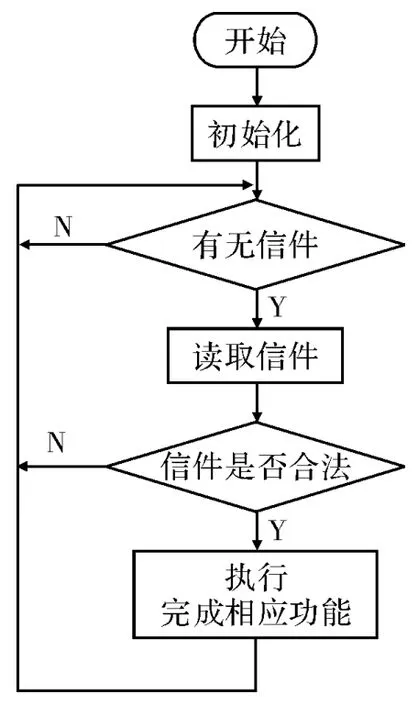

单片机程序主要包括主程序、定时器中断处理子程序和串行中断处理子程序。串行中断处理子程序完成控制命令的接收;主程序完成器件的初始化、处理控制命令、控制DDS芯片工作等功能[5-6]。主程序流程图如图7所示。

图7 主程序流程图

5 实际测试结果

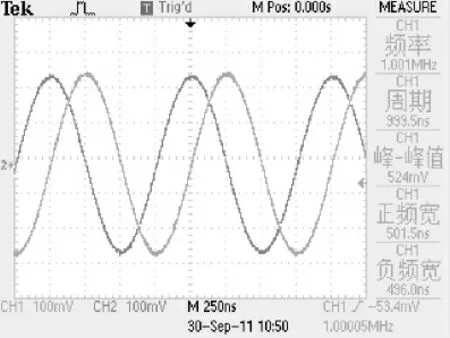

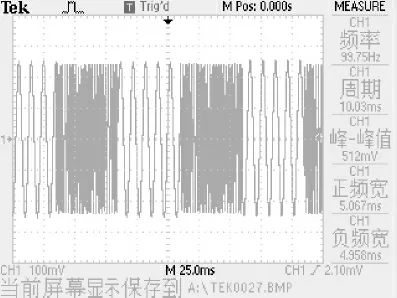

为测试信号发生器的性能,借助示波器对其输出波形进行了测试,测试结果如图8~图10所示。

图8 输出两路相互正交的正弦波

图9 输出FSK调制信号

6 结束语

本系统是一个基于DDS技术的信号发生器,DDS技术的应用大幅提高了信号发生器的性能。实验结果表明,该系统具有频率分辨率高、频率转换速度快、输出频率高、可输出多种波形等特点,并且具有可编程性好、性价比高、运行稳定可靠等优点。

图10 输出ASK调制信号

[1] 白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

[2] 唐颖.单片机技术及C51程序设计[M].北京:电子工业出版社,2012.

[3]Analog Devices,Inc.AD9854 Datasheet——COMS 300 MSPS Complete DDS[M].USA:Analog Devices,2007.

[4] 江志红.AVR单片机系统开发实用案例精选[M].北京:北京航空航天大学出版社,2010.

[5] 高士友,胡学深,杜兴莉,等.基于FPGA的DDS信号发生器设计[J].现代电子技术,2009(16):35-37,40.

[6] 张鑫.一种基于LabVIEW的多功能虚拟仪器的构建方法[J].西安邮电学院学报,2011,16(5):68-71.