FPGA的PS配置方式在显示系统中的应用

2013-04-25吴乾科陈国庆

吴乾科,陈国庆

(西安电子科技大学 技术物理学院,陕西 西安710126)

在当今的市场变化环境中,产品是否能在线升级,是否能方便使用,成为产品进入市场的关键。在这种背景下,Altera公司的基于SARM LUT的FPGA器件得到了广泛应用,这类器件的配置数据存储在SARM,然而由于SARM具有掉电易失性,故通电自动加载配置是这类器件应用必需的。Altera公司也提供了几种被动下载的配置的方式,本文就其中的PS下载配置方式作详细概述,并介绍在远程显示系统中的应用过程。

1 FPGA常用加载方式介绍

Altera公司生产的FPGA器件中CycloneⅣ系列提供了以下几种配置方案:主动串行(AS)、主动并行(AP)、被动串行(PS)[1]、快速被动并行(FPP)和JTAG,其中最常用的是主动串行、被动串行与JTAG。AS、PS、JTAG配置方式的区别有:AS模式:烧到FPGA的配置芯片里保存的,FPGA器件每次上电时,作为控制器从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程,AS配置方案中这些配置器件是具有非易失内存的低成本器件,具有简化4管脚接口和小型化的特征;PS模式:EPCS作为控制器件,把FPGA当做存储器,把数据写入FPGA中,实现对FPGA的编程。该模式可以实现对FPGA在线可编程;JTAG:直接烧到FPGA里面的,由于是SRAM,断电后要重烧,JTAG配置方案可以使用USB-Blaster等下载电缆下载数据到器件上,这种方式便于测试,可以进行在线仿真。考虑到在产品上的应用,PS配置可实现远程的在线配置[2],便于产品的维护与升级,所以得到广泛应用。

2 PS加载方案

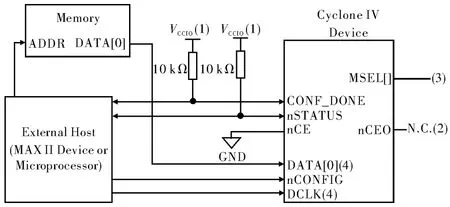

2.1 使用外部主机进行单器件PS配置

当开始配置时,外部主机器件必须在nCONFIG管脚中产生一个由低至高的跳变。当拉高nSTATUS时,外部主机器件必须一次一位地将配置数据放置在DATA[0]上。在使用.rbf、.hex、.ttf格式时,必须首先发送每个数据字节的LSB。CylongⅣ器件在DATA[0]上接收配置数据,时钟在DCLK上被接收。在DCLK的上升沿,数据被锁存到器件中。数据不断送入目标器件,直到CONF_DONE变高以及器件进入初始化状态。

图1 单器件配置结构图

在CONF_DONE变高后需要两个DCLK的下降沿以开始初始化器件。当初始化完成后,INIT_DONE被释放和拉高。外部主机器件必须能检测到由低到高的跳变,其标志着器件已进入用户模式。在PS方案中,DATA[0]管脚在用户模式下默认为三态,它必须由外部主机器件驱动。要在QuartusⅡ软件中更改这种默认选项,选择Device and Pin Options对话框中的Dual-Purpose标签。配置时钟(DCLK)的速度必须低于指定系统频率,以确保正确的配置。无上限DCLK周期的存在,意味着可以通过停止DCLK无限期地暂停配置。CONF_DONE管脚必须由外部主机器件监控以便检测错误和确定编程序是否完成。如果所有配置数据被发送后,但CONF_DONE INIT_DONE没有变高,外部器件必须对目标器件进行重配置。

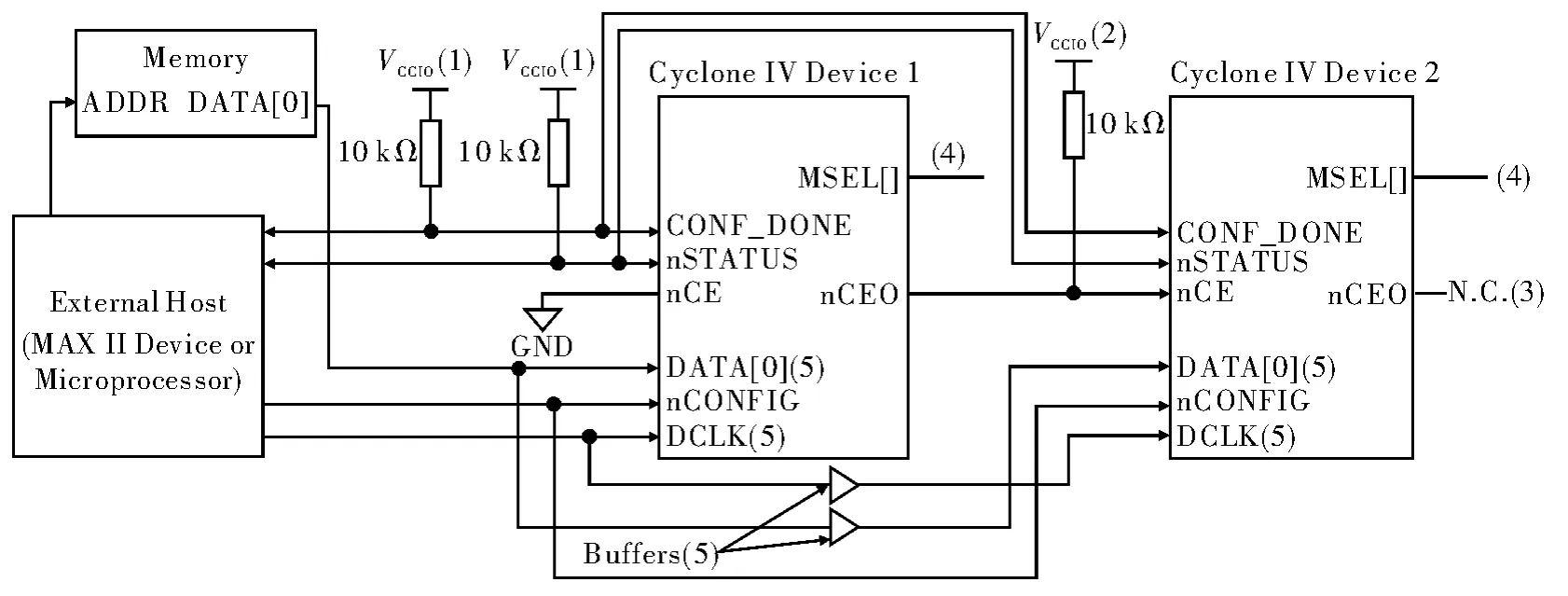

2.2 使用外部主机进行多器件PS配置

在多器件配置链中完成第一器件配置后,其nNEO管脚驱动至低电平以激活第二个器件中的nCE管脚,提示第二个器件开始进行配置。链中第二个器件开始在一个时钟周期中的配置。因此,对于外部主机器件,传输数据的目的地是透明的。nCONFIG、nSTATUS、DCLK、DATA[0]和CONF_DONE配置管脚都连接到链中的每个器件上。为了确保信号的完整性以及防止时钟的偏斜问题,配置信号可能需要缓冲。确保DCLK和DATA线是缓冲的。所有器件初始化并且同时进入用户模式,因为所有的CONF_DONE管脚都是连在一起的。

图2 多器件配置结构图

如果任何器件检测到一个错误,整条链的配置都将停止,然后必须对其进行重配置。

2.3 PS配置时序

PS配置时序[3],如图3所示。

图3 PS配置时序

配置结束后,FPGA还需要一个初始化的过程才能进入正常工作状态。在QuartusⅡ生成的配置文件中已经包含了额外的初始化比特,只需要将配置文件的数据在配置时钟的同步下全部送出就已经完成了初始化。

2.4 配置文件的使用

Altera公司的开发工具QuartusⅡ可以生成多种格式的配置文件,针对不同的配置方式需要使用不同格式的配置文件[5]。设计项目编译后自动生成.sof文件和.pof文件。基于.sof文件还可以生成.hex、.rbf和ttf文件。其中,.rbf文件时二进制文件,1 Byte的rbf数据包包含8 bit的配置数据,使用时将其存入ROM中。微控制器从ROM中将其读出再送入FPGA[4],串行和并行配置方式都可以使用这种格式的文件。

3 系统设计

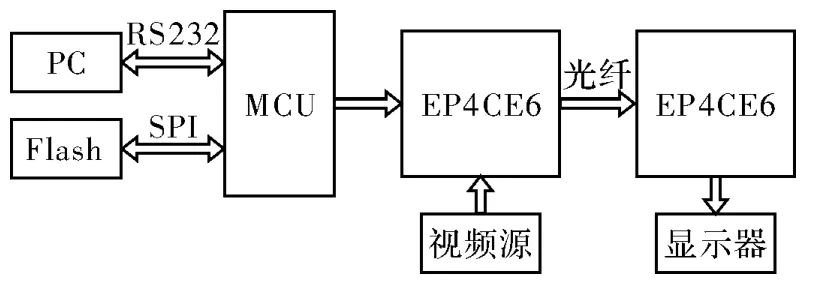

3.1 硬件设计

显示系统利用STC12LE54单片机对EP4CE6F256C8N进行PS配置的硬件结构如图4所示。

图4 系统结构图

因为这里用的FPGA是EP4CE6,其配置文件大小有2 Mbit,在给FPGA配置数据时,配置文件经由上位机通过MCU存储在Flash中,因为MCU的内部容量有限,上位机也分次传送,由于选用的Flash为W25x32VSSIG,其所支持的页操作为256 Byte,故每次传送256 Byte,最后一次传送剩下的字节。在配置FPGA的过程中,MCU一边读取Flash中的数据,一边在给FPGA配置,这里采用PS配置多器件的方案,当配置完控制板上的FPGA后继续从Flash中读取接口板FPGA的配置数据,数据通过总线的工作方式从控制板FPGA到串化器,在另一端的解串器解出这3位并行数据,从而完成接口板的FPGA配置。

3.2 软件设计

在该配置方案中,软件包括在PC上位机端的控制软件和在MCU端的控制程序。PC上位机端的窗口软件采用C#编写,MCU程序采用C语言。

对于文中所用的FPGA:EP4CE6,其配置文件大小为2 Mbit,由于单片机存储限制使得无法一次性地将配置文件全部发送至单片机,所以一些通用的串口调试助手无法使用,所以必须在PC上位机上编写个一个文件分割的串口软件。

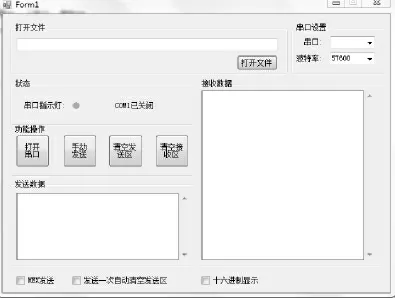

上位机软件如图5所示,主要功能是将.rbf配置文件进行256 Byte分割,发送至MCU,使MCU方便对Flash的写页操作。

图5 PC上位机软件界面

MCU对FPGA的配置程序流程图如图6所示。

图6 单片机程序流程图

4 结束语

利用单片机采用PS配置方案实现FPGA的数据加载方式,经过系统调试,当给单片机加载程序后,通过PC上位机串口助手将配置文件发送给单片机后断电,然后重新通电,系统在2 min后正常工作,虽然配置时间较长,但比较稳定,重置率低。其主要优势在于一方面可以上电被动加载,无需次次重新配置,另一方面当要更新系统时只需通过串口发送更新的配置文件即可,为实际应用带来较大的便利。

[1] 薛昀,李宗艳,张德安.基于单片机的FPGA被动串行配置方式[J].桂林电子工业学院学报,2005(3):29-32.

[2]胡启道,张福洪,戴绍港.基于MCU的FPGA在线配置[J].电子器件,2007(3):1049-1051.

[3]Altera公司.Cyclone device handbook[EB/OL].(2013-03-01)[2013-03-12]http://www.pudn.com/downloads193/ebook/deta.

[4] 徐维祥,刘旭敏.单片微型机原理及应用[M].大连:大连理工大学出版社,1996.

[5] 胡修林,席向清,张蕴玉.嵌入式系统中FPGA的被动串行配置方式[J].单片机与嵌入式系统应用,2004(3):21-23.