基于FT2232H 的边界扫描测试控制器的研究与设计

2013-04-09汪选胜陈真

汪选胜,陈真

(河海大学 能源与电气学院,江苏 南京 211100)

随着大规模的集成电路技术朝着超深亚微米方向发展,芯片的内部结构变得日趋复杂。芯片的集成度也已达千兆位,时钟频率正朝着向千兆赫兹以上发展,芯片的引脚数量也在急剧上升。新型的芯片封装技术如PGA,BGA,SMT,MCM 等被大量采用,同时电路板的布线层数和密度也大大增加,使得外部可以接触的引脚越来越少,特别是如今正日益兴起的片上系统(SOC),在一块芯片上集成了整个系统,因此也就不能通过外部的物理探针对系统的内部节点进行访问测试;而且,对于高密度的复杂电路板而言,采用物理探针可能会对电路板结构和布线造成损坏。可以看出,集成电路实现的功能是越来越强大,其内部结构的复杂度也日益增强,但是测试的费用却呈指数递增,测试的开销在电路和系统总开销中所占的比例日益变大。对电路板在线测试的传统方法通常是通过测试探针或针床技术来实现的,它必须用金属探针与PCB 电路板上的器件和走线产生直接的物理接触。可以看出,用传统的线路检测设备(ICT)和针床测试需要付出很高的代价,有时甚至不能解决这些问题[1-2]。

针对传统测试方法在测试复杂数字电路板过程中所遇到的阻碍,以及电路的板级、芯片级、乃至系统级等不同层次的测试实现的需求,本文提出并设计了一种基于FT2232H 的边界扫描测试控制器,能显著简化电子设备的测试过程,缩短测试所需时间,增强测试设备的故障诊断能力,提高电子设备的可测性。

1 测试需求分析

边界扫描测试系统的要求是能够根据测试人员提供的硬件描述文件(电路板网络表文件和器件边界扫描描述文件)产生合适的测试矢量集,将测试矢量加载到被测电路,完成对被测电路的测试,分析,诊断等功能,进一步要求测试系统具有友好的人机交互界面、精确的故障诊断能力等。其具体需求如下:

1)边界扫描测试的时钟频率可调。由于边界扫描测试时候,测试矢量是通过TDI 串联加载到被测电路的,所以测试的速度是测试过程中考虑的重要因素,在这套系统中,测试速度主要取决于测试时钟TCK 的频率,但是,很多被测芯片对最高的TCK 频率有限制,所以就要求边界扫描测试系统的时钟是可调的。

2)JTAG 接口的电平兼容问题。由于测试系统的输出电平与被测电路的接口电平不一定完全相同,为了使系统具有更高的兼容性,需要将边界扫描测试系统的输出电平转换为被测电路的需要的接口电平。

3)支持对具有多个扫描链的对象的测试。在实际的测试中,很多比较复杂的被测对象可能具备多个独立的边界扫描链,为了支持对这种复杂的对象的测试,就要求边界扫描控制器能提供多个IEEE 1149.1 总线测试端口。

4)准确的故障覆盖率和定位精度。边界扫描测试系统的主要功能就是故障检测和故障定位,良好的测试矢量集是保证故障覆盖率和定位精度的关键。所以要求测试能够根据各种经典测试算法产生测试矢量集。

5)软件的通用化和模块化。要求边界扫描系统能够根据被测电路的网表文件和器件的BSDL 文件,从中提取有用的信息,结合一定的测试测试矢量生成算法,生成相应的测试矢量。此外,为了方便后期软件的维护与升级,把实现每个功能的模块打包成动态库形式。

2 总体设计

边界扫描测试技术为数字电路的测试与研究提供了一套完整的、标准化的方法。该测试系统主要包括两个部分:主机控制部分和受控部分。主机控制部分提供符合IEEE1149.1 标准的信号,受控部分就是包含有边界扫描结构的被测电路,主要是接受测试矢量,产生响应。这一部分可以是芯片,也可以是电路系统。

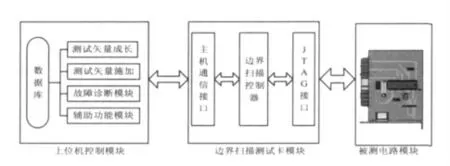

根据边界扫描测试系统功能和性能需求,边界扫描测试系统采用主/从结构设计,由主控计算机模块、边界扫描测试卡模块和被测电路板模块组成。系统总体结构如图1 所示。

图1 系统总体结构图

图1 中上位机控制模块使用的是普通PC 机,主要运行边界扫描测试软件,完成测试任务、人机交互界面和数据的管理。边界扫描测试卡模块的任务是与主控计算机进行通讯,接收主机发过来的测试矢量集,产生符合JTAG标准的测试总线,通过TDI 将测试矢量加载到被测电路上进行测试;测试结束后,测试卡向主机发出通知,此时主控计算机将测试响应数据读走。图1 中被测电路模块是完成可测试性设计的电路板,在设计电路板时一定要考虑可测性的要求,使电路板不仅能满足功能需求,也可以使用边界扫描测试系统对其进行测试。

3 系统硬件设计

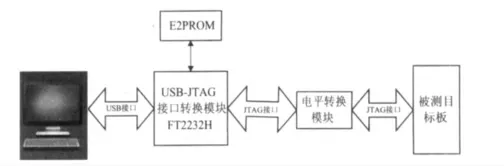

边界扫描测试控制器硬件可分为两部分:一部分是USB接口通信控制芯片,另一部分是JTAG 主控芯片.综合考虑芯片的传输速度,内部的硬件资源,功耗,开发工具包,与JTAG接口的连接等因素,选择FTDI 公司的FT2232H[3]芯片。该芯片的最大特点是将整个USB 协议处理都做到芯片里,而且不需要编写任何的固件程序,所有的数据收发和协议转换工作全部由转换器来独立完成,开发过程简单。控制器利用USB控制芯片实现USB 协议与PC 机进行通信,同时通过操作JTAG 主控芯片,使其输出到JTAG 总线上的数据符合IEEE 1 149.1标准,从而达到由PC 机控制JTAG 总线的目的。在这里主控芯片就通过操作MPSSE(多协议同步串行机接口)来实现USB 到JTAG 的转换。降低了开发难度。总体硬件框图如图2 所示。

图2 系统硬件结构图

在上面的系统中,有两条数据通道,一条是流出主控计算机的通路,首先主控计算机通过USB 总线将数据输出到FT2232H 的RX 缓冲区中,然后USB 芯片通过MPSSE 接口将数据转换成合IEEE1 149.1 标准的数据,通过MPSSE 接口输出测试信号;另一条是流入主控计算机的通路,首先是MPSSE 接口采集到测试响应,存放在FT2232H 的TX 缓冲区中,主控计算机通过发送命令,将数据从缓冲区中读回,为故障诊断做准备。

3.1 供电电路设计

USB 总线接口具有向外提供电源的能力,这样在一定程度上可以满足USB 设备的电源需求。USB 协议中规定,供电输出电压一般为4.75 V~5.25 V,每个USB 端口的最大输出电流为500 mA,并且电流大小可以通过程序控制。鉴于测试控制器功耗低,对电流要求不高,USB 总线的驱动能力足以驱动测试卡,因此,测试控制器不需要外部电源供电,采用总线供电的方式即可。

在测试系统中,USB 控制芯片FT2232H 要求有一个+3.3 V的电压供应。所以需要在电路中进行电压转换。本设计采用的TI 公司的TPS73 433 芯片是一款单路稳定输出电压为3.3 V 的低静态电流低噪声的稳压器。可以稳定提供给FT2 232H 工作,具体电路图如3 所示。

图3 FT2232H 电源工作模块

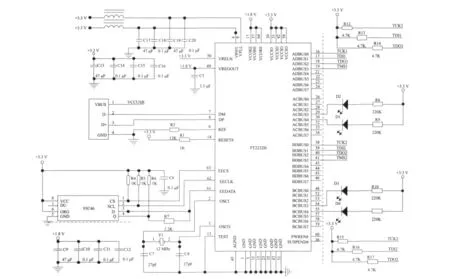

3.2 FT2232H 工作电路设计

FT2 232H 的具体应用电路如图4 所示,在FT2 232H的每个通道有两个IO 引脚控制LED 状态指示灯,分别用于指示传输和接收数据。传输/接收数据时,各自引脚从三态驱动至低电平,LED 灯闪烁指示数据正在传输。如果使用数字计时器,数据传输的百分之几也可清楚传输至用户终端。FT2 232H 外接12M 的晶体振荡器,在XTDI,XTOUT 与GND 之间增加电容器,这将有利于晶体的起振,增加一个外部的E2PROM(93C46/56/66)可以允许将每个通道单独的配置成串口或者并口的模式,这个E-2PROM 也可以用来定制USB 设备的VID,PID,串行号,设备描述符等信息,该E2PROM 必须是16 位宽,工作在4.3 V~5.25 V 范围内,在FTDI 的网站上提供了MPROG V3.4 a 软件可以对该E2PROM 编程[4],当然如果没有外置E-2PROM,则FT2 232H 被缺省配置成一个双向串行口,设备使用缺省的VID,PID,设备描述符等。

图4 USB 到JTAG 转换接口图

3.3 JTAG 电平转换电路

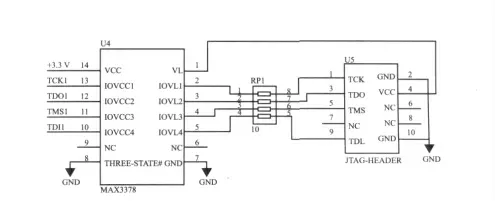

FT2 232H 的通道被配置为输出高电平是3.3 V,而被测电路的板的接口电平却是多种多样的,目前数字电路中广泛使用的接口电平主要有1.8 V,2.5 V,3.3 V,5 V 等几种。为了使本测试卡的JTAG 接口具有更高的电平兼容性,要求电平转换芯片能把MPSSE 接口的3.3 V 电平转换成被测电路板需要的接口电平,除此之外,从TDO 口返回的信号也要能从被测电路板的电平转换成3.3 V。

从以上分析看出,接口电路对电平转换要求比较高,需要支持几种电平的双向转换,综合考虑,选择Maxim 公司的MAX3378 芯片[5],此款芯片有4 个I/O 通道。两个基准电压输入脚VCC(1.25 V~5.5 V)和VL(1.65 V~5.5 V),通过在这两个管脚上面施加不同的基准电压,可以很方便地实现电平的双向转换,此外还有一个输入管脚THREE-STATE,用来控制电平转换的使能端,低电平有效,具体的电路如图5 所示。

把JTAG 接口上TCK,TMS,TDI 和TDO 管脚都通过MAX3 378 连接到FT2 232D 的A 通道的可编程I/O 管脚。MAX3 378 的VL 脚连到JTAG 接口的4 管脚,由相应的被测电路板提供给这个基准电压。同样的道理,通道2的JTAG 的设计也是如此。

图5 JTAG 接口电平转换原理图

4 测试系统软件设计

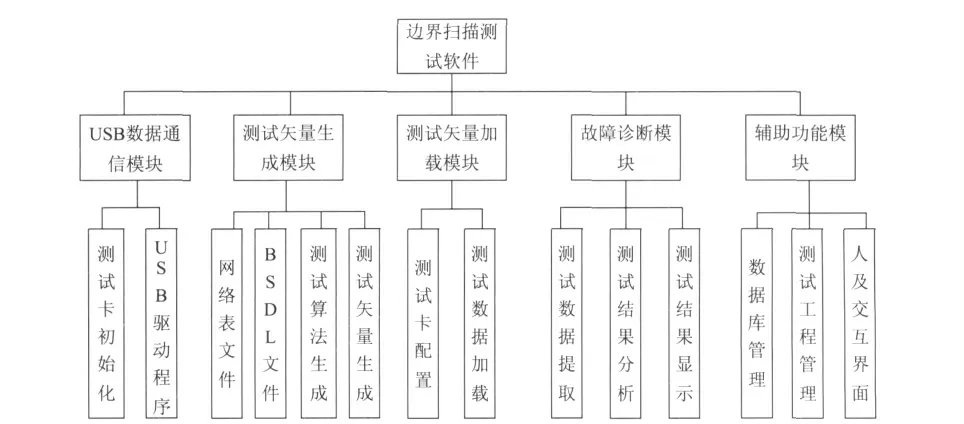

据边界扫描测试过程和系统的性能要求,测试应用软件是运行在Windows XP 系统上,在Visual C++6.0 环境下,使用面向对象技术开发完成。根据测试系统的功能将整个软件注意分为以下几个模块,分别为:测试文件生成模块、USB 上下数据通信模块、测试数据生成模块、响应数据分析模块、故障诊断模块和辅助功能模块。另外为了完善的数据的管理和方便各个模块间的数据调用,测试软件引入了Access 数据库,数据库将存储BSDL 文件和电路网表文件的分析结果并且保存生成的测试矢量集和测试结果响应矢量集。软件结构图如图6 所示。

图6 系统软件设计结构图

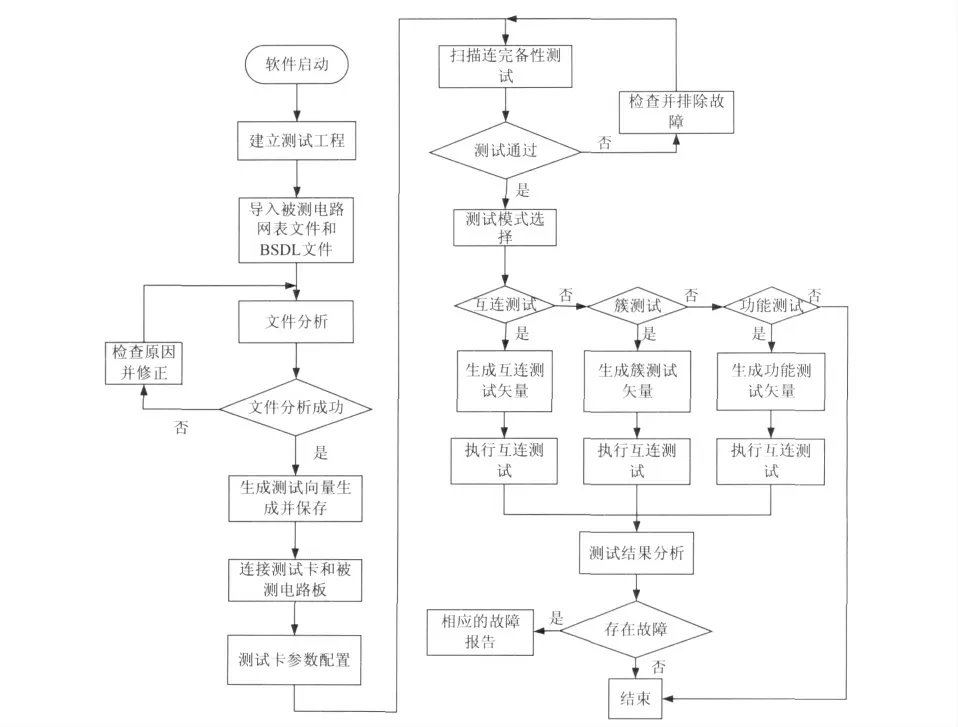

测试软件的主体分为5 个模块,分别是测试矢量生成模块、测试矢量施加模块、USB 上下位机通信模块故障分析模块和辅助功能模块。测试矢量生成模块是通过分析电路的网络表文件和BSDL 文件,提取其中的有用信息,再结合具体的算法生成测试矢量集,再将测试矢量集转换为可以施加到扫描链上的测试数据。测试矢量加载模块是负责配置测试卡,并将生成的测试数据加载到被测电路中。USB 数据通信模块是负责根据驱动程序,初始化测试卡,为数据传送做好准备。故障诊断模块是根据获得的响应数据,提取有用信息,根据板级测试理论进行故障的分析和定位。辅助功能模块提供人机交互的界面,数据库的测试工程的管理[6-7]。整个软件的工作流程如图7 所示。

图7 软件设计的流程图

5 结论

针对传统电路测试中的阻碍,本文研究了一种的边界扫描测试控制器,以FT2 232H 芯片为核心,能够通过各种配置,快速方便地实现USB 接口道JTAG 接口之间的转换,而且各种USB 协议的处理工作都是芯片内部自动完成;以计算机为平台,利用微软公司的Microsoft VC++6.0 通过面向对象的程序设计方法和可视化界面技术开发出软件控制界面,以此完成测试矢量的生成与加载和响应数据的回收和数据分析,并最终完成故障诊断和结果显示的功能。结果表明该测试控制器不仅具有测试时钟可调,测试速度快、成本低、便于携带、开发难度较低等优点,还能缩短测试所需时间,增强测试设备的故障诊断能力,提高电子设备的可测性,具有很高的工程应用价值。

[1]陈光禹,潘中良.可测性设计技术[M].北京:电子工业出版社,1997.10-22,177-180,285-292,194-201.

[2]Plunkett,Domainic.Taking JTAG Testing Further Electronic Product Design[J],International Test Conference,2005,9(50):58-60.

[3]FTDI 公司.FT2232H Data sheet[DB].http://www.ftdichip.com/Documents/DataSheet/ DSFT2232H_V201.pdf .2008.

[4]王计元,王立胜,黄昶.新的FT2232C 型USB UART/FIFO 电路的特征及应用[J].电子设计工程,2005,13(8):44-46.

[5]Maxim.Max3378 Data Sheet[DB].http://pdfserv.maxim-ic.com/en/ds/MAX3372E-MAX3393E.pdf.2003.

[6]Hansen P.Testing Conventional Logic and Memory Cluster using Boundary Scan Devices as Virtual ATE Channels[J].Proc.of Intl.Test Conf.1989:200-209.

[7]王宁.基于边界扫描的逻辑簇测试诊断软件开发[J].半导体技术,2006,(4):276-279.