一种新型delta-sigma小数分频器的FPGA实现

2013-02-21王水鱼冯晓靖

王水鱼,冯晓靖

(西安理工大学 自动化与信息工程学院,陕西 西安 710048)

新一代移动通信系统对频率源的要求集中在低相位噪声、快捷变这两个方面[1]。delta-sigma调制(DSM)技术最初应用于模数转换[2-5],但其良好的噪声成型技术却使其应用相当广泛,一个最典型的例子就是应用于小数分频技术[6-8]。众所周知,经典小数分频的一个最大的瓶颈就是其输出相位噪声比较严重[9]。而相噪指标太低,必然制约了小数分频技术在当今无线通信系统中的应用[10-12]。DSM在小数-N频率合成方面的应用主要起到一个调节分频比的作用。输入一个常数,这个常数为小数-N分频的分数部分值,输出为不断变化的分频比,利用DSM噪声成型的作用,量化部分的噪声可以被DSM本身搬移到高频的部分,这样,就可以利用PLL本身的低通性能,在噪声加到VCO之前就被滤除掉。因此,DSM技术既可以实现小数分频,同时又可以较好地抑制小数分频出现的杂散情况。

1 delta-sigma原理分析

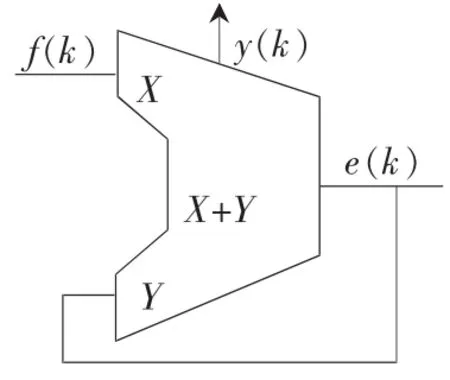

delta-sigma(△-∑)调制具有噪声整形特性,能将噪声从低频段整形到高频段,大大减小了带宽内的量化噪声[13]。单环的delta-sigma调制器实质是一个单阶误差反馈电路,其结构如图1所示。

图1 单环delta-sigma调制器

其中,x[n]为 n bit表示的小数分频比,Q[.]为量化器,y[n]为量化输出,M满足 M=2n。该结构与一级相位累加器的数学模型是一致的,因此可以用一级累加器来实现单环△-∑调制器,累加器模型如图2所示。

图2 一级累加器模型

令累加器位数为 n bit,同理,f(k)表示分频比的小数部分,y(k)为累加器溢出值,溢出为1,否则为0,e(k)为累加值。 一级相位累加器作为单环 △-∑调制器对其自身量化误差e(k)具有一定的滤波作用,但十分有限,通常会采用高阶MASH结构以克服量化误差。

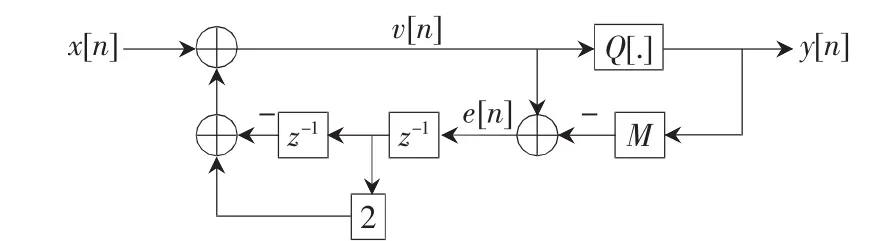

MASH1-2-1结构是在三级MASH结构的基础上加以改进的结构,量化器产生的白噪声经过几级调制后就被变换成了高通型噪声,噪声能量绝大部分处于锁相环本身的低通滤波通带之外。该结构包含了两个一阶量化器和一个二阶量化器,一阶量化器的结构如图1所示,二阶量化器结构如图3所示。

图3 二阶△-∑误差反馈结构

该结构的Z域模型为:

Y(z)=X(z)-(1-H(z))E(z)

其中,H(z)=1-(1-z-1)2=2z-1-z-2。

噪声传递函数为:

N(z)=(1-z-1)2

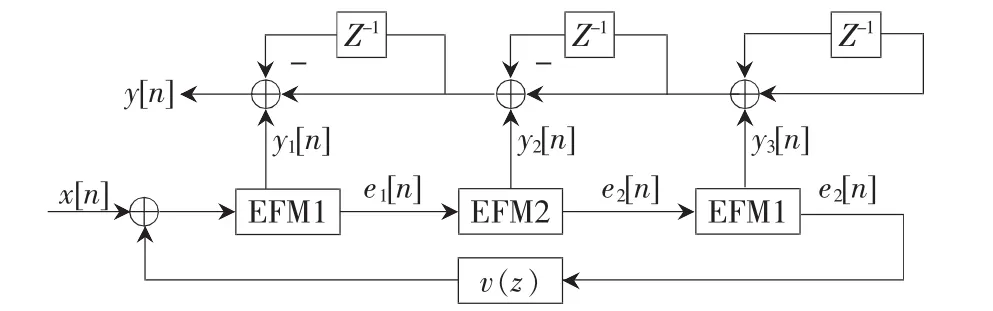

MASH1-2-1结构如图4所示。

图4 MASH1-2-1结构框图

由图 4 可知,输入输出关系为 Y(z)=X(z)-(1-z-1)4E3(z),且噪声传递函数为 N(z)=(1-z-1)4。 由于第三级误差反馈结构的误差输出序列的周期很长,可以近似视为随机序列,将此信号序列反馈回输入端,相当于在输入端注入了抖动信号,可以进一步降低杂散信号的周期性,减少杂散信号离散谱线的输出。加入抖动信号的MASH1-2-1结构如图5所示。

图5 加入抖动的MASH1-2-1结构

其中,v(z)是为了降低输入噪声而设置的二阶滤波器,v(z)=(1-z-1)2。

2 基于delta-sigma小数分频的FPGA实现

小数N分频器是通过周期性地改变分频比使平均分频比为N+F/M,其中,F为数字量化后的分频比小数部分,M为n比特累加器的最大值2n。小数分频器的输入输出频率关系为fvco=N.F×fREF,其小数分频锁相环结构方框图如图6所示。

图6 delta-sigma结构的小数分频锁相环

图6中虚线框内的结构即为需用FPGA实现的delta-sigma小数分频部分,该部分可分为delta-sigma调制模块和整数分频模块两个模块设计。△-∑调制模块采用小数分频后的时钟信号作为参考信号,根据小数分频值F来产生周期性可变分频比 △N,使得N+△N的均值为N.F,整数分频器根据分频比N+△N对VCO输出的信号进行分频,并将分频后的信号送往鉴相器与参考信号进行比较。下面分别讨论delta-sigma调制部分和整数分频部分的FPGA实现。

delta-sigma调制部分采用图5所示的加入抖动的MASH1-2-1结构,EFM1可以直接利用一阶累加器实现,EFM2可以采用一阶加法器和D触发器来组合构成,同样v(z)也可利用一系列D触发器组合实现。由于要对EFM1和EMF2的溢出值进行加减运算,因此需将溢出值转换为补码表示,且加法器需进行补码的加减运算。对于MASH1-2-1结构来说,最终输出的由小数分频比产生的控制信号 △N可能存在的值为±3,±2,±1,0。再利用加法器将整数分频比输入N和控制分频比△N相加,就得到控制锁相环整数分频比变化的分频信号。MASH1-2-1结构的顶层原理图如图7所示。

3 实验结果与分析

该顶层原理图通过仿真得到输出分频比的仿真波形如图8所示。f_N为输入的整数分频比,frac是输入的小数分频比部分,由于累加器采用8 bit位宽,故此时真正的小数分频比为 F=93/256≈0.4,fdiv_N即为输出的实际整数分频比N+△N,其均值应为N.F=10.36。

整数分频器根据delta-sigma调制器输出的分频比对VCO的输出信号进行分频,在完成一次分频过程后再从delta-sigma调制器中取下一个分频比进行下一次分频。由于分频比可能为奇数也可能为偶数,故分频器必须能够实现奇数分频和偶数分频。

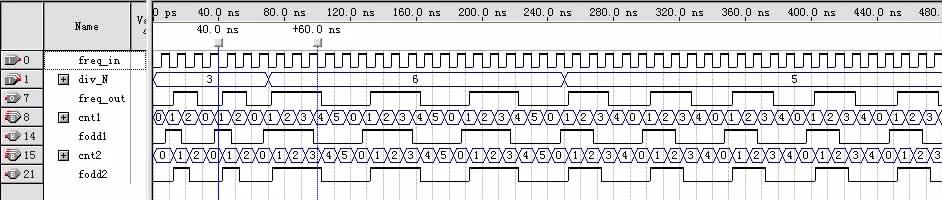

分频器仿真波形如图9所示。

图9中,freq_in为输入的待分频信号,div_N是输入的整数分频比,可以看出,该分频器既能实现奇数分频又能实现偶数分频,且当分频比改变时,能够及时地根据新分频比进行分频。

综合以上分析即可得到delta-sigma小数分频器,如图10所示,freq_out就是小数分频后的输出信号。

所得到的仿真波形如图11所示。从图11可以看出,freq_out是分频比为10.4的仿真波形。在对应的整数分频比内,输出信号正确地按照该分频比值fdiv_N进行分频;输入分频比变化时,输出信号频率也能及时地发生相应变化,从而实现了对输入信号的小数分频。

图7 MASH1-2-1结构顶层原理图

图8 delta-sigma调制输出分频比

图9 分频器输出波形

图10 △-∑小数分频器

图11 △-∑小数分频仿真结果

本文通过对MASH1-2-1结构原理的分析,论述了可实现的FPGA模型,并完成了基于FPGA的deltasigma小数分频器的实现。该结构不用于一般的MASH单阶多级结构,在第二级引入二级误差反馈环路,使得调制器整体阶数为四阶,这样做的目的在于:在不增加MASH结构级数的情况下,通过改变单元调制器的结构来降低量化噪声。同时,为了使得输出噪声功率谱曲线更加平滑,在输入端引入随机序列来打断输出周期性。通过FPGA实现模块化,可以很方便地嵌入到锁相环的设计中,提高了设计的通用化和高效化。

[1]RILEY T A D,COPELAND M A, KWASNIEWKI T A.Delta-sigma modulation in fractional-N frequency synthesis[J].IEEE Journal of Solid-State Circuit, 1993,28(5):553-559.

[2]REINHARDT V, GOULD K, MCNAB K, et al.A short survey of frequency synthesiser techniques[C].40th Annual Symposium on Frequency Control,1986:355-365.

[3]WARE K M,LEE H,SODINI C G.A 200 MHz CMOS phase-locked loop with dual phase detectors[C].1989 IEEE InternationlSolid-State Circuits Conference,36th ISSCC,Digest of Technical Papers, 1989:192-193.

[4]CANDY J C,BENJAMIN O.The structure of quantization noise from sigma delta modulation[J].IEEE Transactions on Communications,1981,29(9):1316-1323.

[5]CANDY J C.Use of double integration in sigmadelta modulation[J].IEEE Transactions on Communications,1985,33(3):249-258,.

[6]NORSWORTHY S R, SCHREIER R,TAMES G C.Deltasigma data converters[M].New York: Wliey IEEE Press,1997.

[7]MOTAMED M,SANDERS S,ZAKHOR A.The double loop sigma delta modulator with unstable filter dynamics:stability analysis and tone behavior[J].IEEE Transactions on Circuits and Systems II: Anglog and DigitalSignalProcessing,1996,43(8):549–559.

[8]KOZAK M A,KALE I.A pipelined noise shaping coder for fractional-N frequency synthesis[J].IEEE Transactions on Instrumentation and Measurement, 2001,50(5):1154-1161.

[9]MENINGER S E,PERROTT M H.A fractional-N frequency synthesizer architecture utilizing a mismatch compensated PFD/DAC structure for reduced quantizationinduced phase noise[J].IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 2003,50(11):839-849.

[10]PAMARTI S,GALTON I.LSB dithering in MASH deltasigma D/A converters[J].IEEE Transactions on Circuits and Systems I: Regular Papers, 2007,54(4):779-790.

[11]KOZAK M,KALE I.Rigorous analysis of delta-sigma modulatorforfractional-N PLL frequency synthesis[J].IEEE Transactions on Circuits and Systems I: Regular Papers, 2004,51(6):1148-1162.

[12]MILLER B,CONLEY R J.A multiple modulator fractional divider [J].IEEE Transactions on Instrumentation and Measurement, 1991,40(3):576–583.

[13]BORKOWSKI M J, RILEY T A D, HAKKINEN J, et al.A practical△-∑ modulatordesign method based on periodicalbehavior analysis [J].IEEE Transactions on Circuits and Systems II: Express Briefs,2005,52(10):626-630.