基于FPGA的数字信号传输性能分析仪的设计与实现

2013-01-15樊汝森裴秀高

樊汝森,王 勇,裴秀高,张 源,宋 辰,刘 丹

(1.上海电力学院,上海 200090;2.山东莱芜供电公司,山东莱芜 271100;3.青岛大学,山东青岛 266071)

随着曼彻斯特编码和m序列在通信、以太网领域的广泛应用,作为一种数据传输通道性能检测的设备,数字信号传输性能分析仪在数据传输系统的安装与调试及日后系统的维护中起着越来越重要的作用.通过观察眼图,可以得到信号的畸变范围、噪音的容限,以及门限电平和定时误差灵敏度等有效信息,以此可以定性反映码间干扰的大小和噪音的强弱,因此可通过观察眼图来分析信道传输性能.

现场可编程门阵列(Field-Programmable Gate Array,FPGA)基于反镕丝技术或SRAM 技术,具有良好的抗干扰性能,其并行运算处理速度快,因此FPGA的数字化设计已经成为数字逻辑电路设计的重要发展方向.

为了扩宽信号分析带宽,特别是低频信号的分析带宽,提高眼图显示的稳定性、测试精度,以及系统的抗干扰性能,降低系统功耗,节约能源,本文提出了一种基于FPGA的新颖设计方法.该方法以FPGA为系统控制核心,采用改进型计数方式控制曼彻斯特编码数据率,在采集信号后先进行数字滤波,再进行信号分析,达到实时刷新提取同步时钟信号的目的,这不仅大大简化了设计复杂的外部硬件电路,而且极大地提高了眼图显示的稳定性和信道性能测试的精确性.

1 系统组成

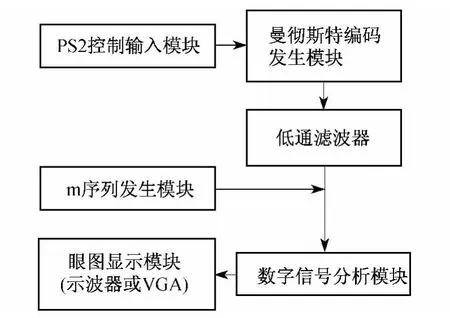

系统结构框图如图1所示.系统主要由5个模块构成,即:PS2控制输入模块;曼彻斯特编码发生模块;m序列发生模块;数字信号分析模块;眼图显示模块.系统采用PS2键盘输入曼彻斯特编码(用来模拟传输信号)的时钟频率,FPGA接受控制信号后产生m序列并采用曼彻斯特编码,在数据率为10~1×106b/s时连续可调,然后将信号送入低通滤波器(用来模拟信道数字信号传输特性).滤波器输出的信号与隔直的数据率10 Mb/s高频m序列(用来模拟信道噪音)相叠加,FPGA控制高速AD进行信号采样后经数字信号分析模块提取曼彻斯特编码同步时钟频率,利用所提取的同步时钟频率进行同步,采用示波器显示信号眼图.

图1 系统结构框图

2 硬件电路的设计

为了便于系统测试,故设计低通滤波器来模拟信道数字信号的传输特性,采用硬件电阻分压来调整信道噪音大小.

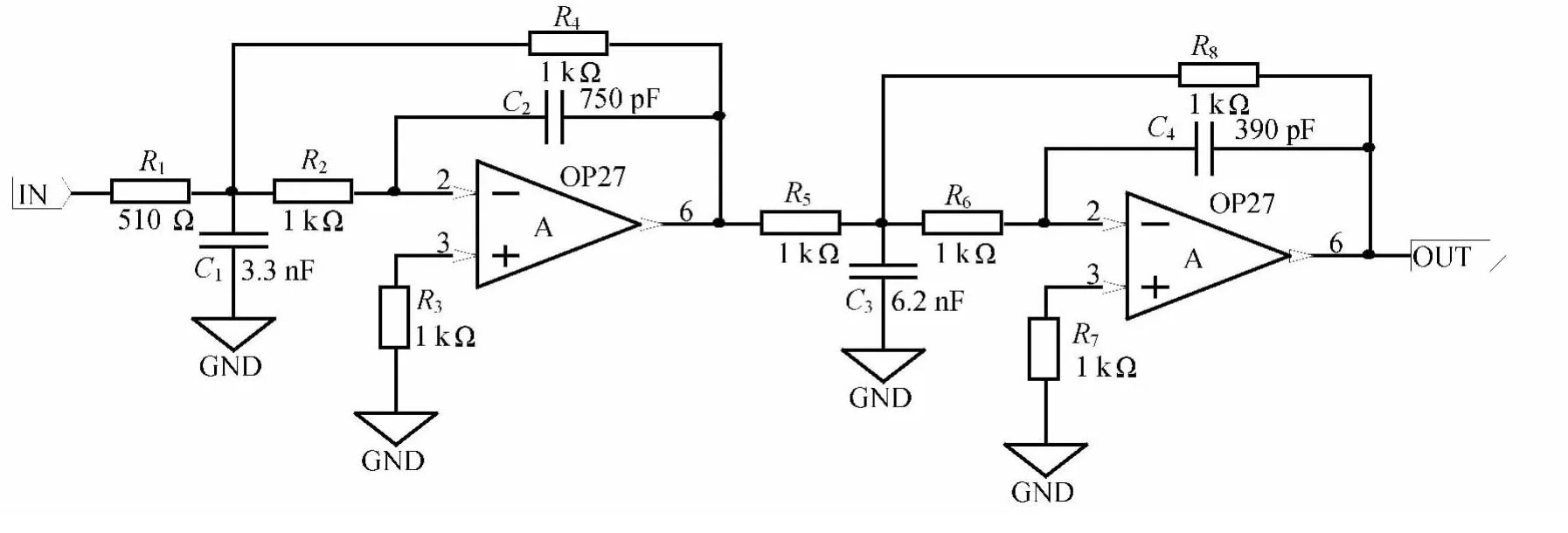

系统采用截止频率分别为100 kHz,200 kHz,500 kHz的有源低通滤波器,且每个滤波器带外衰减不少于50 dB/10倍频程,采用4阶无限增益多路反馈滤波电路,其中截止频率为100 kHz的滤波电路如图2所示.

图2 截至频率100 kHz的滤波电路

信道噪音大小可通过硬件电阻分压的方法来调整m序列发生器输出信号的幅值实现.调整后的m序列输出端信号经隔直电容叠加到低通滤波器输出端,叠加后的信号作为数字信号分析电路的输入信号.

3 数字信号发生模块

数字信号发生模块包括PS2控制输入模块、m序列发生模块和曼彻斯特编码发生模块.系统采用高频m序列来模拟信道噪音,系统测试信号m序列采用曼彻斯特编码,曼彻斯特编码的时钟频率采用PS2键盘输入,数据率的控制采用改进型计数方式.

3.1 m序列的产生

由于FPGA内部采用门阵列结构,能够很方便地产生m序列和曼彻斯特编码,系统采用12级m序列:

来模拟信道噪音,其中:

其12级m序列线性反馈移位寄存器结构如图 3 所示[1].

图3 12级m序列线性反馈移位寄存器结构示意

其线性移位寄存器可表示为:

其反馈函数方程为:

3.2 曼彻斯特编码的产生

数字信号发生器为:

其m序列采用曼彻斯特编码输出.在曼彻斯特编码过程中,每一位的中间有一个上升沿或下降沿的跳变.此跳变既可作时钟信号,又可作数据信号,上升沿表示“0”,下降沿表示“1”,可有效防止同步时钟信号的丢失[2,3].

3.3 数字时钟的产生

FPGA产生的时钟频率普遍采取计数比较方式,这种方式存在缺陷,只能生成指定周期整数倍的时钟频率,不能完全随机指定频率.本系统采用了改进方案,即采用定点小数对比累加方式进行时钟生成,用此种方式生成的时钟可以保证在一段时间(取决于定点小数的位数,在此为65 536个生成时钟周期)的统计特性上达到小数位数最小步进值乘以生成周期的精度.虽然无法保证每个周期长度都完全相等(误差在正负1个主时钟周期——在此为100 ns以内),但只要生成时钟的周期远大于这个值,即可忽略其左右的偏移.数字信号发生模块流程如图4所示.

图4 数字信号发生模块流程示意

4 数字信号分析模块

4.1 数字滤波处理

系统采用美国德州仪器的8位半闪速结构的高阻抗并行AD转换器TLC5510,将叠加后的信号采集到FPGA系统.由于采集到的信号噪音太大,须先进行数字滤波处理才可进行相应的信号分析[4].

经Modelsim仿真后,数字滤波处理仿真如图5所示.

图5中,Source为低通滤波器输出信号;Niose为生成的模拟随机噪音,幅值约为满值的50%;AD_data为叠加噪音后的AD采集信号;Smooth为滤波处理后的波形,有些尖脉冲来自于后仿真ps级的跳变不同步信号;Data_out为经寄存器后得到的反向有效输出信号.

图5 平滑数字滤波处理仿真

4.2 提取曼彻斯特编码同步时钟

通过FPGA检测曼彻斯特编码上升沿和下降沿的间隔时间,可以得到曼彻斯特编码的时钟周期.提取曼彻斯特编码同步时钟的流程见图6.

图6 提取曼彻斯特编码同步时钟的流程

为了满足时钟的统计特性,需要对多次采集的结果取平均值,曼彻斯特编码上升沿和下降沿间隔时间只有1倍周期和1/2倍周期两种情况,每次上升沿和下降沿的时间间隔与现有的生成时钟计数进行比较判断,确定是否满足上述两种情况.若满足,则将当前计数放入求平均的寄存器入口,否则更新求平均的所有寄存器的值为当前测量值.

最终利用曼彻斯特编码的跳变沿对生成的时钟信号进行实时刷新,以达到同步的效果.

5 系统性能测试

5.1 测试仪器

测试仪器为数字存储式示波器,采用数控式线性直流稳压电源.

5.2 曼彻斯特编码时钟频率测试

首先使用PS2键盘预设曼彻斯特编码时钟频率,然后将FPGA提取到的曼彻斯特编码同步时钟信号输入示波器任意通道,使用示波器观察提取的同步时钟频率,见表1.

表1 曼彻斯特编码时钟频率测试记录 kHz

测试表明,系统可以从10~1×106Hz的任一整数数值预设曼彻斯特编码时钟频率,并且数字分析电路能够提取曼彻斯特编码同步时钟频率.经计算,预设与提取时钟频率的误差小于0.3%.

5.3 眼图显示测试

眼图采用示波器显示,将提取到的同步时钟信号输入示波器的外部触发端,将叠加有噪音的曼彻斯特编码信号输入示波器任一通道,即可在示波器上生成正确眼图.当噪音较小时,眼图显示见图7,当噪音较大时,眼图显示见图8.

图7 噪音较小时的眼图显示

当存在噪音时,眼图的线迹变成较为模糊的带状线.噪音越大,线条越宽,越模糊,“眼睛”张开得越小.其最佳抽样时刻应是“眼睛”张开最大的时刻;眼图斜边的斜率决定了系统对抽样定时误差的灵敏程度,斜率越大,定时误差越灵敏;模糊带状垂直高度表示信号的畸变范围;中央的横轴位置对应于判决门限电平;抽样时刻的上下两阴影区的间隔距离一半为噪音容限,噪音瞬时值超过它就可能发生错误判断[5].

图8 噪音较大时的眼图显示

经测试,数字分析电路提取的同步时钟信号能够触发叠加噪音的曼彻斯特编码,并能在示波器上准确显示眼图.当噪音峰峰值提高时,仍然能较好地在示波器上显示眼图,噪音峰峰值最大为2 Vpp.

6 结语

系统整体性能良好.曼切斯特编码数据率可以实现从10~1×106b/s连续可调,当噪音峰峰值为2 Vpp时,仍可以正确提取同步时钟信号,并能满足大部分用户的使用.但系统在提取同步时钟信号时仍存在不足,需要进一步改善.

[1] 樊昌信,曹丽娜.通信原理(第6版)[M].北京:国防工业出版社,2006:379-390.

[2] 付林,任志平,刘承杰.基于FPGA技术的曼彻斯特编码器设计[J].现代电子技术,2007(17):55-56.

[3] 晏磊.基于FPGA曼彻斯特码数据传输系统的实现[J].微计算机信息,2006,22(2):169-170.

[4] 郑君里,应启珩,杨为理.信号与系统:下册(第3版)[M].北京:高等教育出版社,2011:209-237.

[5] 樊昌信,张甫翊,徐炳祥,等.通信原理(第5版)[M].北京:国防工业出版,2001:115-116.