高电源噪声抑制比带隙基准源设计

2012-12-29吴丽丽

吴丽丽

(华侨大学 信息科学与工程学院,福建 厦门 361021)

高电源噪声抑制比带隙基准源设计

吴丽丽

(华侨大学 信息科学与工程学院,福建 厦门 361021)

采用CSMC 0.35μm工艺,通过在电源和带隙基准源电路间插入电流源缓冲级的方法,设计提高带隙基准源电源噪声抑制能力的带隙基准源 .在最低工作电压不变的情况下,所设计的带隙基准电源大幅度提高了电路的电源抑制比,且功耗低 .仿真结果表明:电源抑制比值为110dB/40dB,Iq=12μA,Vmin=2.4V,可作为模拟IP(知识产权)且易集成于单片系统中.

带隙基准源;电源噪声抑制比;低工作电压;低功耗;模拟IP

在单片系统(SOC)集成电路工业中,模拟电路主要以模拟IP(知识产权)的形式出现.带隙基准源电路是最经常被使用的模拟IP之一,被广泛应用于线性、开关稳压源电路,模数、数模转换电路,各种温度、电压检测电路等.因此设计出高性能的带隙基准源电路对于集成电路工业具有重要意义[1-2].稳压电源的电源抑制比(power supply rejection ratio,PSRR)在很大程度上取决于带隙基准源的电源噪声抑制能力.文献[3]分析表明:低频PSRR特性完全取决于带隙基准源的PSRR特性.因此,提高电源的PSRR特性需要设计高PSRR的带隙基准源电路,尤其是需要优化其低频段的PSRR特性.本文讨论一种能有效提高带隙基准源电源噪声抑制能力的电路拓扑结构,并从原理上分析其动作原理.

1 提高带隙基准源PSRR的原理

要提高PSRR特性,首先要提高带隙基准源电路中的运放增益.出于稳定性的考虑,一般用于带隙基准源的运放不超过两级,否则很难进行补偿.这就限制了带隙基准源本身的环路增益,即限制了通过提高运放增益来提高其PSRR的空间.要进一步提高其PSRR,比较可行的方法是在实际电源和带隙基准源的电源中加入缓冲[4-5],使从带隙基准源看来的电源波动对于实际电源波动有较大衰减.

缓冲的方法一般有插入电压源和插入电流源.插入电压源即在实际电源和带隙基准源的电源中间插入低压降线性稳压电源(low dropout regulator,LDO),带隙基准电源看到的电源噪声将被衰减.这样带隙基准电源的PSRR将被大大提高,幅度等于LDO的PSRR值.但在实际的芯片系统中,LDO本身就需要带隙基准源来为其提供基准电压[6-7],因此很难找到与带隙基准(band gap reference,BGR)输出值不相关的线性基准源来为其供电 .所以,插入的LDO也必须以BGR的输入作为参考,实际PSRR提高幅度会略低于分析值.这个结构最大的问题是LDO需要BGR的输入作为参考,而BGR需要LDO的输入作为电源 .这就形成了正反馈环路,存在2个简并点,不能自己启动.由于LDO本身也是复杂的反馈环路[2,8],需要较复杂的启动电路来帮助其启动.

插入电流源也可提高带隙基准源的PSRR.当电源电压波动时,参考电流源可以维持偏置电流恒定,使MOS管的栅电压严格跟随电源电压波动.理论上,如果电流源为理想电流源,栅电压变化完全等于电源电压变化,MOS管VGS变化为0,BGR电源端看到的噪声也为0.但是,同插入电压源缓冲一样,实际电路中很难找到与电源电压无关的电流源 .因此,该电流源通常也来自于BGR 产生的偏置电流.尽管这样,该结构还是可以大大提高电路的PSRR.同插入电压源相比,该结构中的电流偏置环路较LDO环路结构简单,环路启动电路容易设计.

2 电路的拓扑结构

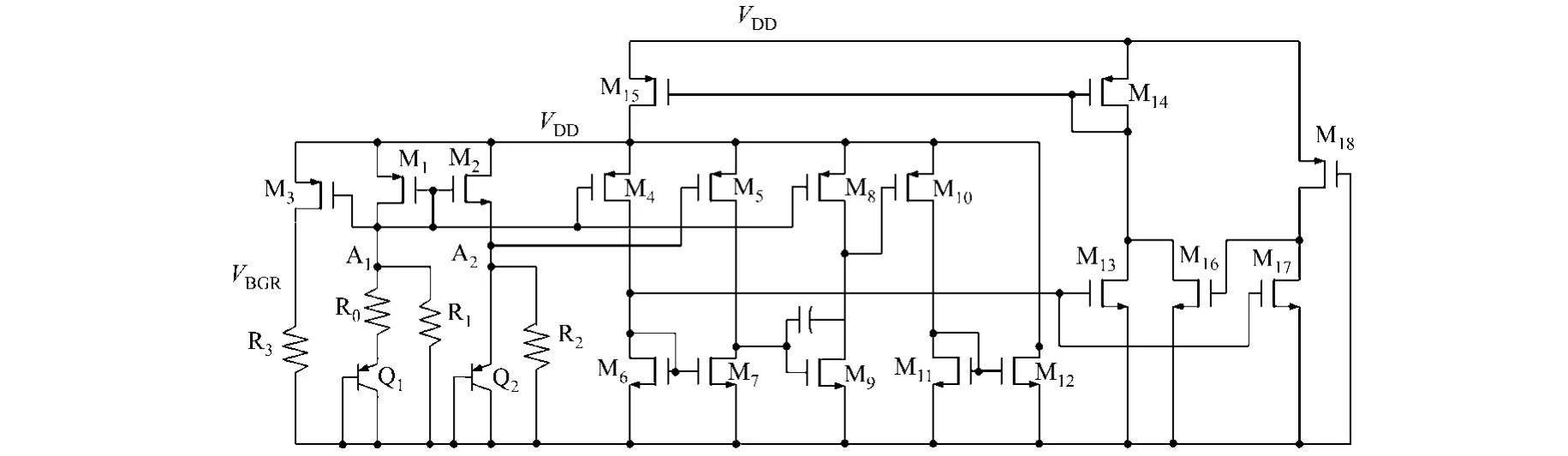

设计的高PSRR带隙基准源,如图1所示 .图1中:M13,M14,M15为插入的电流源,用于提高BGR的PSRR特性;M1~M12为电流模BGR环路,该负反馈环路使A1/A2的电压相等,即流过匹配电阻R1/R2的电流相等,同时M1/M2的电流值也相等.两个电流的差值分别流过三级管Q1/Q2,其发射极

图1 插入电流源提高PSRR的带隙基准源拓扑结构Fig.1 Schematic of high PSRR bandgap voltage reference by inserting current source buffer

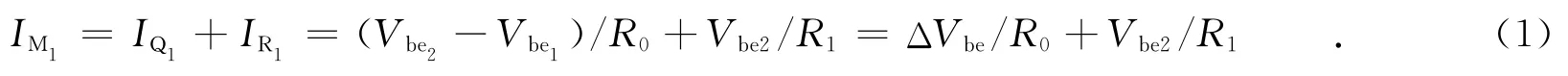

面积的比值为N∶1.由此,可以得出流过M1的电流为

M3镜像M1/M2的电流,流入R3,可得到BGR的输出电压VREF为

最后,得到输出电压为传统BGR[9]输出电压乘以R3与R1的比值.设计中采用了0.6V输出,使M3能够保持在饱和区,保持M1/M2/M3的电流匹配.

为了确保电路的低压工作性能,运放的输出没有像传统结构一样驱动PMOS电流源,而采用了“折叠”的结构,通过驱动NMOS电流源M12来建立负反馈环路,可以使电路的最低工作电压降低1倍的MOS管导通电压Vds.同时,M1/M2电流镜的设计使运放不需要尾电流源,差分端A1/A2与V′DD的差值为M1的Vgs值,可以直接连接到增益级的输入对管M4/M5,又使最低工作电压降低了Vds.最终电路的最低工作电压为Vbe+Vgs+Vds,与传统结构接近.

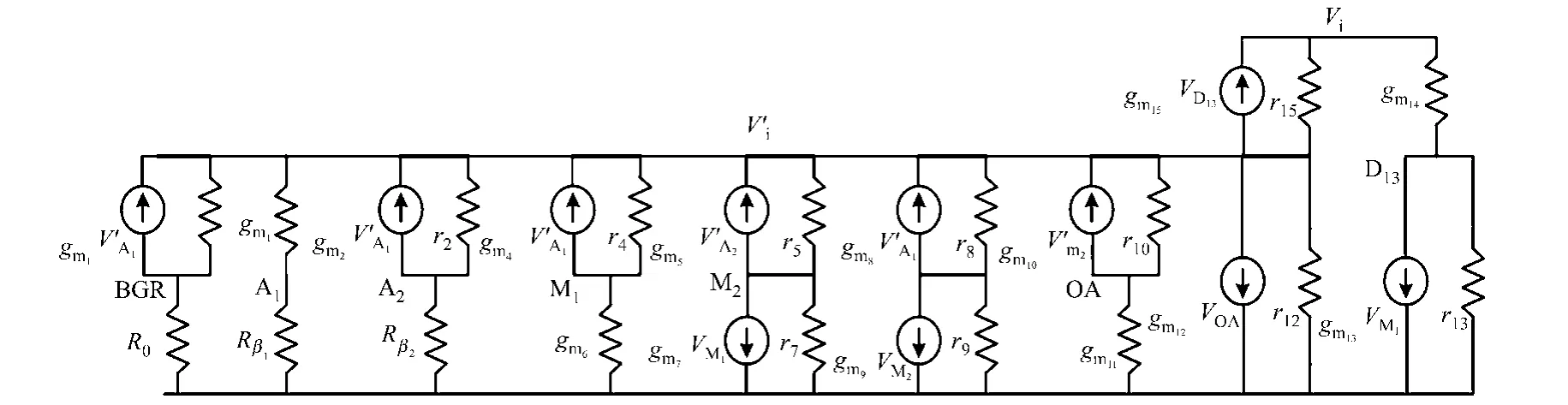

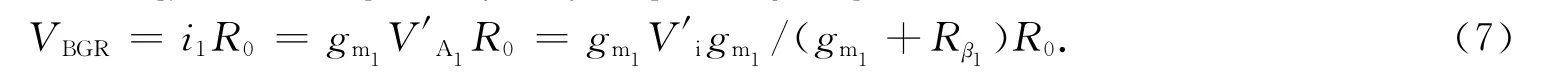

电流小信号模型提高PSRR的原理,如图2所示 .图2中:Vi为电源电压波动,V′i为电流源输出端电压波动,即BGR电路的等效电源波动,V′A1/A2为A1/A2点相对于V′i的电压变化 .根据电路结构,可以得到 M1=M2=M3=M4=M5=M8,M6=M7=M9=M13,M12=k1M11,M15=k2M14.根据V′i点的电流守恒,得到

图2 本带隙基准源电路的小信号模型Fig.2 Small-signal model of the proposed bandgap voltage reference

将式(4),(5)代入式(3)中,可得到

而

将式(7)代入式(6)中,可得到电路的PSRR表达式

3 实验结果

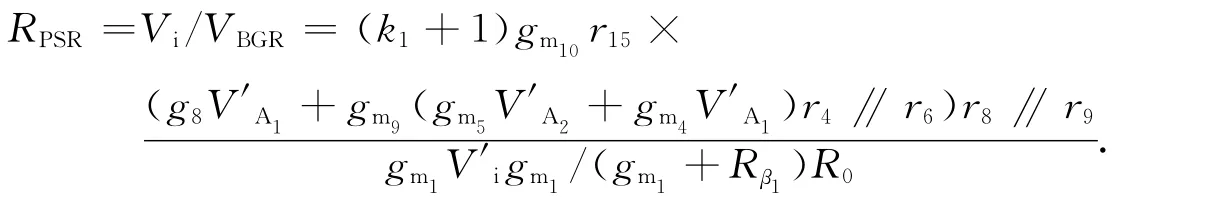

电路采用CSMC 0.35μm工艺设计并进行仿真,静态电流为12μA.CSMC 0.35工艺中晶体管阈值电压为0.9~1.2V,低温下PNP管的Vbe为0.8V,管子的Vdssat一般设计为0.2V,所以电路最低工作电压为2.4V.在不同工作电压的情况下,带隙基准源的温度曲线如图3所示.从图3可知,带隙基准源的温度系数仿真值为7.5×10-6,为典型一阶温度系数补偿曲线.

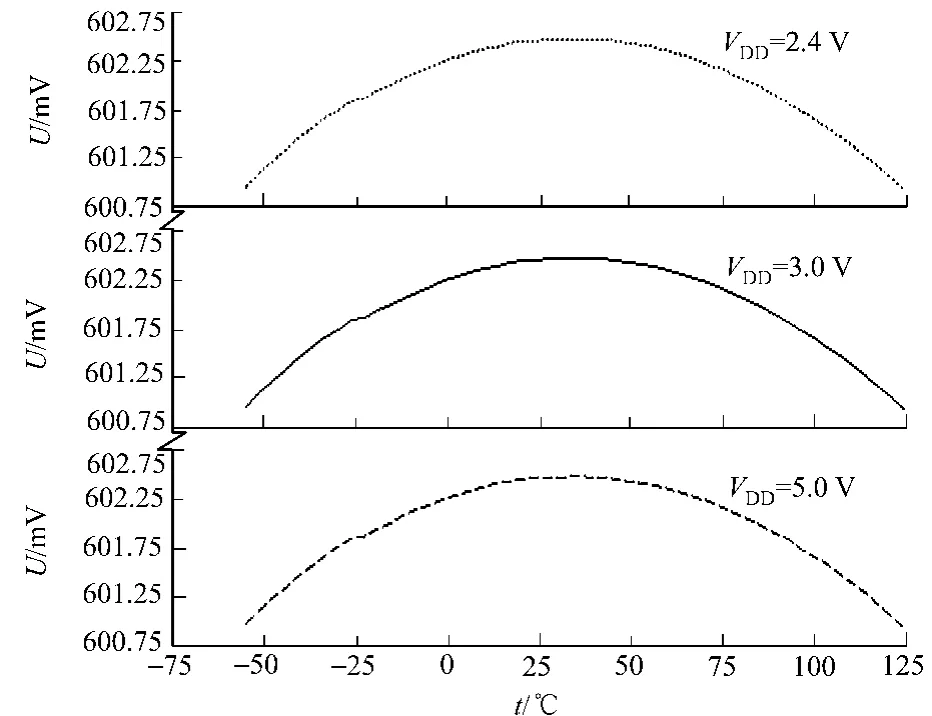

在各个温度及工作电压下,所设计的带隙基准电源噪声抑制比仿真结果,如图4所示 .从图4可知,直流情况下的电源噪声抑制比可以达到120dB.

图3 带隙基准源的温度曲线Fig.3 Temperature curve of bandgap reference

图4 带隙基准的电源噪声抑制比仿真结果Fig.4 Simulated PSRR curves of bandgap voltage reference

3 讨论

由于带隙基准源电路采用2级运放结构(图1中M4~M12部分),环路增益约80dB,可以得出电流源缓冲级结构使PSRR提高约30dB.本设计为低功耗设计(Iq=12μA),限制了电路的交流特性,主极点出现在10Hz附近,在10~100kHz之间出现零极点对,在600kHz处的PSRR衰减至50dB.如果某些应用需要提高交流电源噪声抑制比,可以在结构不变的情况下提高静态电流(同比例减小R0~R3的阻值,并相应增大MOS管的尺寸)[10],以获得更高的带宽,改善中频PSRR特性.

同样,本设计在带隙基准源的输出端级联低通滤波器中加入了带宽约1MHz的一阶RC低通滤波器,使PSRR交流曲线在1MHz处出现拐点.但是,由于片内电阻电容值的限制,这种方法主要高频段有效.通过对交流曲线的分析可以得出,当两种方法结合使用,带隙基准源电路带宽增大和低通滤波器带宽减小被数之积为20倍时,可以使全频率下PSRR高于60dB(当前设计交流PSRR高于40dB).当然这需要对功耗和电路面积进行取舍.

[1]DING Qi-yuan,FENG Liang,HOU Peng,et al.A high-PSR low-power voltage regulating circuit for wireless capsule endoscopy[C]∥10th IEEE International Conference on Solid-State and Integrated Circuit Technology(ICSICT).Shanghai:IEEE,2010:590-592.

[2]HENG S,PHAM C K.Improvement of LDO′s PSRR deteriorated by reducing power consumption:Implementation and experimental results[C]∥9th IEEE International Conference on IC Design and Technology(ICICDT).Austin:IEEE,2009:11-15.

[3]TEEL J C.Understangding power supply ripple rejecton in linear regulators[J].Analog Applicationgs Journal,2005(2Q):8-10.

[4]JIANG Yue-ming,LEE E K F.Design of low-voltage bandgap reference using transimpedance amplifier[J].IEEE J Solid-State Circuits,2000,47(6):552-555.

[5]MALCOVATI P,MALOBERTI F,FIOCCHI C,et al.Curvature-compensated BiCMOS bandgap with 1Vsupply voltage[J].IEEE J Solid-State Circuits,2001,36(7):1076-1081.

[6]HENG S,PHAM C K.A low-power high-PSRR low-dropout regulator with bulk-gate controlled circuit[J].IEEE Transactions on Circuits and Systems(Ⅱ):Express Briefs,2010,57(4):245-249.

[7]HENG S,PHAN C K.Compensated circuit for low dropout regulator having stable load regulation after consideration of bonding wire resistance[C]∥18th Eurpean Conference on Circuit Theory and Design.Seville:IEEE,2007:120-123.

[8]WONG K,EVANS D.A 150mA low noise,high PSRR low-dropout linear regulator in 0.13μm technology for RF SOC applications[C]∥32nd European Solid-State Circuits Conference.Montreux:IEEE,2007:532-535.

[9]梁爱梅,凌朝东 .流镜型二次曲率补偿的带隙基准源设计[J].华侨大学学报:自然科学版,2010,31(3):261-271.

[10]GIUSTOLISI G,PALUMBO G.A detailed analysis of power-supply noise attenuation in bandgap voltage references[J].IEEE Transactions on Circuits and Systems(Ⅰ):Fundament Theory and Applications,2003,50(2):185-197.

Design of the Bandgap Reference with High Power Supply Rejection Ratio

WU Li-li

(College of Information Science and Engineering,Huaqiao University,Xiamen 361021,China)

A band-gap voltage reference with a high power supply rejection ratio(PSSR)is designed by using CSMC 0.35μm processing through the method of inserting current source buffer stage between power and band-gap reference circuit.The proposed band-gap reference greatly improve the circuit`s PSRR and with a low power cost,without changing the lowest working voltage.The simulation results show that,the PSRR with 100dB/40dB,Iq=12μA,Vmin=2.4V,which can be used as analog intellectual property(IP)and easily integrated in the system on a chip(SOC).

bandgap reference;power supply rejection ratio;low working voltage;low-power consumption;analog intellectual property

TN 431.1

A

1000-5013(2012)03-0265-04

2011-05-27

吴丽丽(1982-),女,讲师,主要从事高频电子线路与电子设计自动化的研究.E-mail:will6768@163.com.

华侨大学科研基金资助项目(10HZR05)

(责任编辑:陈志贤 英文审校:吴逢铁)